Fターム[5F102GL09]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 格子定数のずれ、格子歪の利用 (42)

Fターム[5F102GL09]に分類される特許

21 - 40 / 42

半導体装置および半導体装置の製造方法

【課題】GaN系電界効果トランジスタをノーマリオフで動作させつつ、チャネルの電流密度を増加する。

【解決手段】窒素を含む3−5族化合物半導体のチャネル層と、前記チャネル層に電子を供給する電子供給層と、前記電子供給層の前記チャネル層に対向する面の反対面に形成された、窒素を含む3−5族化合物の真性またはn形の半導体層と、前記半導体層と接して形成された、または、前記半導体層との間に中間層を介して形成された制御電極と、を備えた半導体装置を提供する。

(もっと読む)

電界効果トランジスタ

【課題】 非極性面を主面としたIII族窒化物半導体を用いて、積層欠陥の密度が小さい電界効果トランジスタを提供すること。

【解決手段】 非極性面を主面とする基板2の主面からチャネル層4を成長させ、このチャネル層4上にさらに電子閉じ込め層5を成長させることによって、基板2の一方側に窒化物半導体積層構造部3を形成する。チャネル層4および電子閉じ込め層5を成長させるとき、これらを構成するIII族窒化物半導体の格子定数が一致するように、これらのIII族原子のモル分率を適切な値に定める。これにより、チャネル層4上に、チャネル層4とのc軸方向における格子定数が一致する格子整合系の電子閉じ込め層5を形成する。

(もっと読む)

半導体装置

【課題】III族窒化物半導体からなり、ヘテロ接合を有する半導体装置において、HJFETを作製する際、エンハンスメント型のHJFETが容易に実現でき、そのエンハンスメント動作時におけるチャネル抵抗の低減がなされる構造を提供を提供する。

【解決手段】ゲート部を、障壁層に接するように設ける。ゲート直下となる部分では、ゲートを設けていない状態でも、障壁層とチャネル層とのヘテロ接合界面には、二次元電子ガスは発生しないように、チャネル層上に形成されるInAlGaN障壁層を構成する、InAlGaNの組成を選択する。ゲート直下を除き、InAlGaN障壁層の上層として、InAlGaNキャップ層を設ける。InAlGaNキャップ層は、バッファ層と格子整合し、自発分極により、障壁層とチャネル層の界面に二次元電子を発生させる組成のInAlGaNで形成する。

(もっと読む)

半導体装置

【課題】良好なトランジスタ特性を保ちつつ衝突イオン化により生成した正孔を外部に放出することができる半導体装置を提供する。

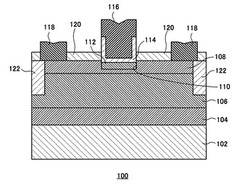

【解決手段】基板100と、基板100上に設けられたIII族窒化物半導体多層膜と、III族窒化物半導体多層膜の上部に設けられた、ゲート電極112、ソース電極110およびドレイン電極114とを備え、III族窒化物半導体多層膜は、正孔走行層104、電子走行層106および電子供給層108を含み、正孔走行層104とゲート電極112とが導電体により電気的に接続されている。

(もっと読む)

半導体エピタキシャル基板、化合物半導体装置、およびそれらの製造方法

【課題】

高周波信号遮断後の回復が早く、素子分離特性のよい化合物半導体エピタキシャル基板を提供する。

【解決手段】

半導体エピタキシャル基板は、単結晶基板と、単結晶基板上にエピタキシャル成長されたAlN層と、AlN層の上にエピタキシャル成長された窒化物半導体層とを有し、単結晶基板とAlN層間界面より、AlN層と窒化物半導体層間界面の方が凹凸が大きい、ことを特徴とする。

(もっと読む)

電界効果トランジスタ用エピタキシャル基板

【課題】良好な電気的得意のFETを高い安定性をもって製造することができる電界効果トランジスタ用エピタキシャル基板を提案すること。

【解決手段】電界効果トランジスタ用エピタキシャル基板において、下地基板1と動作層として動くud−AlGaN層5との間に、Ga又はAlを含むAlN第一緩衝層2とAlGaN第二緩衝層3とを設け、これらの内の少なくとも一方を周期律表においてGaと同一周期にありかつ原子番号の小さい補償不純物元素を添加して高抵抗結晶層とすると共に、この高抵抗結晶層とud−AlGaN層5との間に無添加もしくは空乏状態を維持できる程度の微量アクセプター不純物を含有するud−GaN高純度エピタキシャル結晶層4を設けた。

(もっと読む)

高電子移動度トランジスタ用エピタキシャルウェハ及び高電子移動度トランジスタ

【課題】高電子移動度トランジスタ用エピタキシャルウェハの格子不整合を解消して、このウェハから作製される高電子移動度トランジスタのソース電極−ドレイン電極間の縦方向抵抗を低減する。

【解決手段】GaAs基板1上に、AlGaAs又はGaAsの電子供給層3とInGaAsのチャネル層4とを有する高電子移動度トランジスタ用エピタキシャルウェハWにおいて、電子供給層3とチャネル層4との間に、チャネル層4側から電子供給層3側へIn組成を徐々に小さくしたグレーデッドInGaAs電子供給層7又は8が設けられている。

(もっと読む)

GaN系高電子移動度電界効果トランジスタ

【課題】AlNバリア層の表面のひび割れを防止し、更に、順方向電圧Vf特性を改善する。

【解決手段】AlGaN/GaN−HEMTは、サファイヤ基板21a等の成長基板上にAlN層21bが形成されたAlNテンプレート21と、このAlNテンプレート21上にエピタキシャル成長されたGaNチャネル層22と、このGaNチャネル層22上に形成されたサンドイッチ構造の層とを有している。サンドイッチ構造の層は、下層のAlxGa1ーxNバリア層23と、厚さ2nm以上の中間のAlNバリア層24と、上層側のAlxGa1ーxNキャップ層25とにより形成されている。

(もっと読む)

絶縁ゲート電界効果トランジスタ

【課題】絶縁ゲート構造のGaN−HEMT等において、下地の結晶と格子定数・熱膨張係数の異なる結晶薄膜のAlN膜等をゲート絶縁膜として用いた時に、表面形状の劣化が生じることを防止する。

【解決手段】バリア層又は電子供給層(33)とこのバリア層又は電子供給層(33)に隣接するチャネル層(32)とのヘテロ構造上に、結晶薄膜のゲート絶縁膜(34)が設けられた絶縁ゲート構造のGaN−HEMT等において、下地のバリア層又は電子供給層(33)と同じか、あるいは同様な格子定数又は熱膨張係数を有するキャップ層(35)をゲート絶縁膜(34)上に形成している。そのため、応力がゲート絶縁膜(34)の上下で平均化され、これによって表面形状の改善や、及びその結果得られる電気特性の改善を向上出来る。

(もっと読む)

窒化物系III−V族化合物半導体層の成長方法および半導体装置の製造方法

【課題】基板上に窒化物系III−V族化合物半導体層を良好な結晶品質で成長させることができる窒化物系III−V族化合物半導体層の成長方法を提供する。

【解決手段】GaN層を基板上に化学気相成長法により成長させ、このGaN層上にAlGaN層を化学気相成長法により成長させる場合に、Gaの原料の供給量に対するNの原料の供給量のモル比を8000以上、好ましくは10000以上、より好ましくは11000以上にしてGaN層を成長させる。基板としてはAl2 O3 基板、ZnO基板、SiC基板などを用いる。

(もっと読む)

電界効果型トランジスタ

【課題】窒化物半導体層のヘテロ構造を含むノーマリオフタイプのFETを提供する。

【解決手段】格子定数a1およびバンドギャップEg1を有する第1窒化物半導体層と、第1窒化物半導体層上に積層されていて格子定数a2およびバンドギャップEg2を有する第2窒化物半導体層と、第2窒化物半導体層上に形成されたソース電極およびドレイン電極と、ソース電極とドレイン電極との間の領域において第2窒化物半導体層上に形成されたピエゾ効果膜と、ピエゾ効果膜の領域上に形成されたゲート電極とを含み、格子定数a1とa2との関係がa1>a2であり、バンドギャップEg1とEg2との関係がEg1<Eg2であり、ピエゾ効果膜の第2窒化物半導体層側の表面における残留分極密度が、第1窒化物半導体層と第2窒化物半導体層との界面における2次元電子ガス層の電荷密度以上であって、ピエゾ効果膜の第2窒化物半導体層側の表面にマイナス電荷が分極している電界効果型トランジスタである。

(もっと読む)

半導体電界効果トランジスタ及びその製造方法

【課題】電流ヒステリシス特性が良好で順方向ゲートリークを低減させることができるガリウムナイトライド系電界効果トランジスタを提供すること。

【解決手段】ゲート絶縁膜108を有するガリウムナイトライド系電界効果トランジスタ100において、ゲート絶縁膜108を構成する材料の一部もしくは全部が、比誘電率9以上22以下の誘電体であり、ゲート絶縁膜108に接する半導体結晶層A104と、半導体結晶層A104に近接して、半導体結晶A104よりも大きな電子親和力を有する半導体結晶層B103から構成されるヘテロ接合を有している。ゲート絶縁膜108を構成する材料の少なくとも一部に、HfO2 、HfAlO、HfAlON、又はHfSiO等の酸化ハフニウムを含むようにするのが好ましい。

(もっと読む)

窒化物半導体素子

【課題】良好なノーマリーオフを実現し、低消費電力、大電流、高耐圧、およびハイパワーで動作可能な窒化物半導体素子を提供すること。

【解決手段】電子供給層であるAl0.3Ga0.7N15上に、Al0.3Ga0.7N15よりも大きな格子定数を有する、電子走行層であるGaN16が形成されている。Al0.3Ga0.7N15のGaN16側の表面は、III族面であるので、自発分極電界P自は、Al0.3Ga0.7N15側からGaN16側の方向である。上述のように、GaN16の格子定数はAl0.3Ga0.7N15の格子定数よりも大きいので、GaN16には圧縮応力がかかりGaN16層を歪ませることにより、Al0.3Ga0.7N15側からGaN16側へと向かうピエゾ分極電界が生じる。

(もっと読む)

リサーフ構造を用いた窒化物半導体ヘテロ接合トランジスタ

【課題】リサーフの効果を用いる構造により窒化物系ヘテロ接合トランジスタの高耐圧化を行う。

【解決手段】窒化物半導体により構成されるトランジスタにおいて、GaN層3とAlyGa1−yNバリアー層4のヘテロ接合に形成された二次元キャリアガスの特性を持つn型チャンネルに対して、AlxGa1−xNバリアー層2とGaN層3のヘテロ接合にp型の二次元状キャリアを持つ電界制御チャンネルを平行に形成し、チャンネルと電界制御チャンネルが空乏化したときの空間固定電荷の面密度が実質的に等しくなるトランジスタ構造とすることにより、リサーフ効果を持たせ、これにより、オン耐圧やオフ耐圧の向上を行う。

(もっと読む)

窒化物系半導体装置

【課題】閾値電圧を容易に制御することができるとともに低いオン抵抗を有する窒化物系半導体装置を歩留まりよく提供すること。

【解決手段】ノンドープのAlXGa1-XN(0≦X<1)からなるキャリア走行層1と、キャリア走行層1よりも格子定数の小さいノンドープまたはn型のAlYGa1-YN(0<Y≦1、X<Y)からなる障壁層2と、キャリア走行層1と格子定数の等しいノンドープの半導体からなる閾値制御層3と、キャリア走行層1よりも格子定数の小さいノンドープまたはn型の半導体からなるキャリア誘起層4とが順に積層され、ゲート電極形成領域におけるキャリア誘起層4の全部またはキャリア誘起層4の全部と閾値制御層3の一部を除去したリセス構造30中に形成したゲート電極5と、ゲート電極5を挟んだ障壁層2、閾値制御層3およびキャリア誘起層4のいずれかに形成されるソース電極6およびドレイン電極7と、を備える。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】

寄生抵抗を低減した電界効果トランジスタを提供し、素子の性能および信頼性を向上させることを目的とする。

【解決手段】

基板上に、窒化物半導体からなるチャネル層13と、チャネル層13上に位置し窒化物半導体からなる電子供給層14とを含む積層体を有し、この積層体表面にソース電極16、ドレイン電極17及びゲート電極18を備えた電界効果トランジスタであって、チャネル層13において、ソース電極16及びドレイン電極17各々の下のn型不純物濃度が、ゲート電極18の下のn型不純物濃度よりも高く、電子供給層14において、ソース電極16及びドレイン電極17各々の下のn型不純物濃度が、ゲート電極18の下のn型不純物濃度よりも高い電界効果トランジスタを提供する。

(もっと読む)

歪みシリコンウェーハの製造方法

【課題】SiGe層を有する歪みシリコンウェーハにおいて、SiGe層上に形成される歪みSi層における貫通転位密度の一層の低減化を図ることができる歪みシリコンウェーハの製造方法を提供する。

【解決手段】単結晶シリコン基板上にGe濃度を上げながら組成傾斜SiGe層(Si1−xGex層のGe濃度比xが0<x≦0.5)を厚さ0.1〜3μmにエピタキシャル形成し、その上に厚さ0.1〜1μmのGe組成比が一定である歪み緩和Si1−xGex層を形成し、更に、厚さ5〜30nmの第1歪みSi層を形成し、その上に第2歪みSi層として、第1歪みSi層の成膜温度より低い温度で厚さ10nm以下の歪みSi層をエピタキシャル成長させる。

(もっと読む)

半導体装置

【課題】 半導体のヘテロ構造を含むにも拘らず、ゲート電圧が印加されていない状態では電流が流れないノーマルオフタイプのトランジスタなどの半導体装置を提供する。

【解決手段】 半導体装置1のチャネル層13に接して設けられるバリア層14を、チャネル層13を構成する半導体材料のa軸格子定数a1以上のa軸格子定数a2を有し、かつチャネル層13を構成する半導体材料のバンドギャップEg1よりも大きいバンドギャップEg2を有する半導体材料で形成し、バリア層14に接するようにピエゾ効果材層15を設け、ピエゾ効果材層15のバリア層14に接する側と反対側にゲート電極18を設ける。これによって、ゲート電圧がゼロの場合にはドレイン電流が流れず、ゲート電極18に電圧を印加すると、ピエゾ効果材層15が変形してバリア層14に応力が印加され、ドレイン電流が流れる状態となるノーマルオフタイプのトランジスタ1が得られる。

(もっと読む)

イオン注入および熱アニーリングによるシリコンまたはシリコン・オン・インシュレータ基板上の緩和SiGe層

【課題】Siまたはシリコン・オン・インシュレータ(SOI)基板上に、薄い(300nm未満)歪み緩和Si1-xGexバッファ層を形成する方法を提供する。

【解決手段】これらのバッファ層は、歪みを緩和し、著しく平坦な表面を有し、貫通転位(TD)密度が低い、すなわち106cm-2未満である、一様な分布の不整合転位を有する。この手法は、擬似格子整合またはほぼ擬似格子整合したSi1-xGex層すなわち不整合転位が存在しない層を成長させることから開始し、次いでHeまたは他の軽元素を注入し、続いてアニーリングを行って、実質的な歪み緩和を得る。この方法によって機能する極めて有効な歪み緩和機構は、Si/Si1-xGex界面の下に、Si(001)表面に平行な、Heが誘導した小板(泡でない)における転位核化である。  (もっと読む)

(もっと読む)

半導体装置

【課題】 低いオン抵抗を有するノーマリーオフ型半導体装置を歩留まりよく作製できる半導体装置を提供する。

【解決手段】 InXGa1−XN(0≦X≦1)からなるキャリア走行層1と、キャリア走行層1上に積層され、その一部を除去することで形成されたリセス構造10を有する、もしくはn型のInYAlZGa1−Y―ZN(0<Y≦1、0<Z≦1)からなる障壁層2とを有する電界効果トランジスタにおいて、リセス構造10における障壁層膜厚が、16.4×(1−1.27×Z+0.68×(Y−X))/(Z−4.66×(Y−X))以下である

(もっと読む)

21 - 40 / 42

[ Back to top ]