Fターム[5F102GQ02]の内容

接合型電界効果トランジスタ (42,929) | ヘテロ接合近傍の2次元キャリア層を導電路に利用するもの(H) (2,045) | 単一ヘテロ構造(電子) (1,860) | 電子供給層がチャネル層の下 (138)

Fターム[5F102GQ02]に分類される特許

1 - 20 / 138

半導体装置、高電子移動度トランジスタ、および、複数のチャネルによりソースからドレインに電子を送るための方法

化合物半導体装置及びその製造方法

半導体装置及びその製造方法

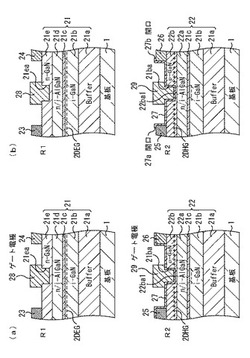

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

半導体装置

【課題】電子が第1励起準位に存在する割合が増えても、量子井戸層の中の電子の有効質量が軽くなる井戸層にできるだけ多くの電子が存在するようにして、より一層の高速化を実現する。

【解決手段】半導体装置を、基板10の上方に設けられた第1半導体層11と、第1半導体層11の上側に接する電子走行層24と、電子走行層24の上側に接する第2半導体層17(25)とを備えるものとし、電子走行層を24、第1井戸層13、中間障壁層14、第2井戸層15を順に積層させた構造を含む2重量子井戸層とし、中間障壁層14の伝導帯のエネルギーが、第1半導体層11及び第2半導体層17(25)の伝導帯のエネルギーよりも低くなり、第1井戸層13及び第2井戸層15の中に基底準位が形成され、2重量子井戸層の中に第1励起準位が形成されるようにする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

トランジスタ素子

【課題】単体構造のHBTデバイスと同等の信頼性を得る。

【解決手段】化合物半導体からなる、高電子移動度トランジスタ(HEMT)とヘテロバイポーラトランジスタ(HBT)とを、同一基板上に重ねてエピタキシャル成長した多層構造のトランジスタ素子において、エピ層として内在するインジウムガリウムリン層(InGaP)のバンドギャップエネルギを1.91eV以上にすることを特徴とする。

(もっと読む)

トランジスタ素子

【課題】n型不純物としてTeを用いたノンアロイ層を有していても、ベース電流、コレクタ電流のリーク電流が少ないトランジスタ素子を提供する。

【解決手段】基板11と、基板11上に設けられた高電子移動度トランジスタ構造層28と、高電子移動度トランジスタ構造層28上に設けられたヘテロバイポーラトランジスタ構造層29とを備えたトランジスタ素子10において、ヘテロバイポーラトランジスタ構造層29のノンアロイ層26,27は、n型不純物としてTeがドーピングされており、n型不純物濃度が1.0×1019cm-3以上2.0×1019cm-3以下にされているものである。

(もっと読む)

電界効果型トランジスタ

【課題】実用上十分なプロセスマージンを備える状態で、リーク電流の増大およびキャリア濃度の低下を招くことなく、ゲート電極とチャネル層との距離が短縮できるようにする。

【解決手段】InPからなる基板101の上に形成された電子供給層102と、電子供給層102の上に形成されたスペーサ層103と、スペーサ層103の上に形成されたチャネル層104と、チャネル層104の上に形成された障壁層105とを備え、障壁層105は、GaおよびAlの少なくとも1つと、Inと、Pとを含んだアンドープの化合物半導体から構成し、InPよりショットキー障壁高さが高いものとされている。

(もっと読む)

半導体装置

【課題】窒化物半導体により、反転型のHEMTが構成された半導体装置において、半導体装置の形成を容易としつつ2DEGを効果的に形成する。

【解決手段】窒化物半導体からなる下地層15の(0001)面上に、窒化物半導体からなる電子供給層17、窒化物半導体からなる電子走行層19の順に積層され、電子走行層19における電子供給層17と反対の面上に、ゲート電極21、ソース電極23、及びドレイン電極25が設けられている。そして、電子走行層19における電子供給層17側に、二次元電子ガスが形成される。このような反転型のHEMTが構成された半導体装置10において、分極の正方向を[0001]方向とした場合、電子供給層17の自発分極とピエゾ分極の和P2が、電子走行層19の自発分極とピエゾ分極の和P1よりも大きくなっている。

(もっと読む)

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

半導体素子

【課題】低オン抵抗で、ノーマリーオフ動作を有し、高信頼性の半導体素子を提供する。

【解決手段】半導体素子1Aは、支持基板10上にN面成長されたAlXGa1−XN(0≦X<1)を含む第1半導体層11と、前記第1半導体層上に形成されたノンドープもしくは第1導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層15と、前記第2半導体層上に形成されたAlZGa1−ZN(0≦Z<1、Z<Y)を含む第3半導体層16と、を備える。半導体素子1Aは、第3半導体層16に接続された第1主電極20と、第3半導体層16に接続された第2主電極21と、第1主電極と第2主電極とのあいだの第3半導体層16の上に設けられたゲート電極31と、を備える。第3半導体層16の厚さは、ゲート電極31下において選択的に薄い。

(もっと読む)

高電子移動度トランジスタ用エピタキシャルウェハの製造方法、及び高電子移動度トランジスタ用エピタキシャルウェハ

【課題】不純物のメモリー効果を低減できる高電子移動度トランジスタ用エピタキシャルウェハの製造方法、及び高電子移動度トランジスタ用エピタキシャルウェハを提供する。

【解決手段】本発明に係る高電子移動度トランジスタ用エピタキシャルウェハの製造方法は、AlxGa1−xAs(ただし、0≦x≦0.3)からなるバッファ層と、バッファ層の上方に設けられ、Se又はTeを含むコンタクト層20とを備えた高電子移動度トランジスタ用エピタキシャルウェハの製造方法であって、600℃以上750℃以下の成長温度、20以上200以下のV/III比の成長条件下で、バッファ層の酸素濃度を2.0E16cm−3以下に制御してバッファ層を単結晶基板上に形成するバッファ層形成工程と、350℃以上500℃以下の成長温度で、コンタクト層20の表面の表面粗さRaを0.5nm以上5.0nm以下の範囲に制御してコンタクト層20を形成するコンタクト層形成工程とを備える。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】フェルミ準位ピン止めが低減された化合物半導体を用いたMOS型の化合物半導体装置がより容易に製造できるようにする。

【解決手段】化合物半導体からなる第1半導体層101を形成し、次に、第1半導体層101より小さいバンドギャップエネルギーの化合物半導体からなる臨界膜厚以下の第2半導体層102を、第1半導体層101の上に接して形成し、次に、第2半導体層102の上にアモルファス状態の金属酸化物からなる絶縁層103を形成する。

(もっと読む)

トランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法

【課題】GaAs基板からHBT構造層に伝搬する転位を抑制したトランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ構造層3が形成され、高電子移動度トランジスタ構造層3上にヘテロバイポーラトランジスタ構造層4が形成されたトランジスタ素子において、GaAs基板2の転位密度が10,000/cm2以上100,000/cm2以下であり、高電子移動度トランジスタ構造層3とヘテロバイポーラトランジスタ構造層4との間に、InGaPからなるエッチングストッパ層12と、エッチングストッパ層12上に設けられたGaAsからなる安定化層21と、を設けたものである。

(もっと読む)

GaNベースの薄膜トランジスタの製造方法

【課題】電流特性と信頼性に優れ、閾値電圧が高いGaNベースの薄膜トランジスタを得ることができる製造方法を提供する。

【解決手段】GaNベースの薄膜トランジスタの製造方法は、n型GaNベースの半導体材を有する半導体エピタキシャル層を、基板上に形成する工程と、半導体エピタキシャル層上に絶縁体層を形成する工程と、絶縁体層上に、絶縁体層を部分的に露出するための開口部を有しているイオン注入マスクを形成する工程と、p型不純物を、開口部および絶縁体層を通してイオン注入して、n型GaNベースの半導体材の中にp型不純物がドーピングされた領域を形成し、その後、絶縁体層およびイオン注入マスクを除去する工程と、半導体エピタキシャル層上に誘電体層を形成する工程と、誘電体層を部分的に除去する工程と、ソース電極およびドレイン電極を形成する工程と、ゲート電極を形成する工程を含む。

(もっと読む)

半導体装置

【課題】化合物半導体上のp型チャネルFETにおいてオン抵抗を低くすることの可能な半導体装置を提供する。

【解決手段】化合物半導体からなる基板10上に、n型チャネルFET領域2とp型チャネルFET領域3とが併設されている。p型チャネルFET領域3において、チャネル層16の下面に接するバッファ層15が、チャネル層16よりも広いバンドギャップを有する第2バッファ層15Bだけで構成された単層構造となっている。さらに、第2バッファ層15Bは、チャネル層16と電子走行層13との間に設けられている。

(もっと読む)

半導体基板、絶縁ゲート型電界効果トランジスタおよび半導体基板の製造方法

【課題】絶縁ゲート型P−HEMT構造において、良好なトランジスタ性能を実現する。

【解決手段】ベース基板、第1結晶層、第2結晶層および絶縁層をこの順に有し、第1結晶層と第2結晶層との間、または、ベース基板と第1結晶層との間に位置する第3結晶層をさらに有し、第2結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層は、ドナーまたはアクセプタとなる第1原子を含み、第3結晶層がドナーとなる第1原子を含む場合、第2結晶層が、アクセプタとなる第2原子を含み、第3結晶層がアクセプタとなる第1原子を含む場合、第2結晶層が、ドナーとなる第2原子を含む半導体基板。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

1 - 20 / 138

[ Back to top ]