Fターム[5F110FF12]の内容

Fターム[5F110FF12]に分類される特許

401 - 413 / 413

自己整合型ナノチューブ電界効果トランジスタおよびこれを製造する方法

【課題】 自己整合型カーボン・ナノチューブ電界効果トランジスタ半導体デバイスを提供する。

【解決手段】 基板(102)上に堆積したカーボン・ナノチューブ(104)と、カーボン・ナノチューブ(104)の第1の端部および第2の端部にそれぞれ形成されたソースおよびドレイン(106〜107)と、誘電体膜(111)によってカーボン・ナノチューブから分離された、実質的にカーボン・ナノチューブ(104)の一部の上に形成されたゲート(112)とを備える。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法。

【課題】 トランジスタの幅が表面積に依存していた。また、半導体シリコン部分を流れる経路が、抵抗として作用していた。

【解決手段】 SOI基板上に、トランジスタのソース部、ゲート部、ドレイン部をウエハ方向に対し横に並べたトレンチ構造で形成し、トランジスタの実効幅が、ウエハ表面に対し垂直方向に依存した構造とした。その結果、微小な面積で大電流を流せるようなトランジスタが制御性良く製造できるようになった。また、CMOSの形成や、様々な半導体素子などとの混載も形成しやすくなった。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】 電界効果トランジスタの製造において、フォトリソグラフィーによって電極を形成するとゲート電極とソース/ドレイン電極間に位置ずれが生じる。

【解決手段】 頂上部のみが分離するように斜面上に活性層と絶縁層を形成する工程と、谷部および前記頂上部に電極を形成する工程を少なくとも含むことを特徴とする電界効果トランジスタの製造方法。

(もっと読む)

ゲート絶縁膜の作製方法

【課題】コストの上昇を招くことなく、より迅速に高品質のゲート絶縁膜が形成できるようにする。

【解決手段】シリコン原料ガス121の供給→パージ→酸素原料ガス122の供給→パージの周期を繰り返す原子層成長法で酸化シリコン層154を形成した後、シリコン原料ガス121と酸素原料ガス122とが混合された混合ガスが酸化シリコン層154の上に供給された状態とし、例えば、全体として55nm程度と、ゲート電圧に耐えられる膜厚の酸化シリコンからなる絶縁層を形成する。

(もっと読む)

薄膜パターンの形成方法、デバイスおよびその製造方法

【課題】 微細な薄膜パターンを精度良く安定して形成できる薄膜パターンの形成方法を提供する。

【解決手段】 本発明の薄膜パターンの形成方法は、基板P上に機能性材料の薄膜パターンを形成する方法であって、基板P上に受容層材料を含む受容層用インク32a(第1の機能液)を配して受容層パターン32を形成する受容層形成工程と、前記受容層パターン32に対し導電性微粒子等を含む導電層用インク(第2の機能液)を配して導電層パターン33を形成する機能層形成工程とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】 高耐圧、低耐圧トランジスタを同一基板に備える半導体装置の、高耐圧トランジスタ領域の面積の削減を図る装置及び方法の提供。

【解決手段】 支持基板10a上の絶縁層10b上に形成された第1半導体層10cと、前記第1半導体層10c内に形成された第1高耐圧トランジスタ100Pと、前記絶縁層上に形成された第2半導体層内に形成された第2高耐圧トランジスタ100Nと、第1半導体層と第2半導体層との間に設けられた絶縁層10bに到達する深さを有する第1素子分離領域110aと、前記絶縁層10b上に形成された第3半導体層内の第1低耐圧トランジスタ200Nと、前記第3半導体層内に形成された第2低耐圧トランジスタ200Pと、前記第3半導体層内に形成され、かつ、前記第1低耐圧トランジスタ200Nと前記第2低耐圧トランジスタ200Pとの間に設けられた、前記絶縁層10bに到達しない深さを有する第2素子分離領域とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 高いドレイン・ソース間耐圧を確保しつつ、低いオン抵抗を実現できる半導体装置及びその製造方法を提供する。

【解決手段】 支持基板1と、支持基板1上に埋込酸化膜2を介して形成され、P-型活性領域3aを有する半導体層3と、ゲート酸化膜17及びLOCOS酸化膜5aの一部を介して半導体層103上に形成されたゲート電極16aとを備え、P-型活性領域3aは、N+型ソース領域11と、P型ボディー領域12と、P+型バックゲートコンタクト領域14と、N型ドレインオフセット領域19と、N+型ドレインコンタクト領域20と、N型ドレインオフセット領域19とP型ボディー領域12との間の局所的な領域に形成されたN型ドレインバッファ領域18とを有し、N型ドレインバッファ領域18はLOCOS酸化膜5aのソース側の端部と接し、N型ドレインオフセット領域19よりも浅い。

(もっと読む)

半導体装置

【課題】同一なチップ内でNチャネルおよびPチャネルの両チャネルが高い耐圧特性を有する高耐圧MOSトランジスタを実現でき得るデバイス構造の製造方法を提供する。

【解決手段】本発明は、Nch型L−DMOS101 とPch型L−DMOS102と論理部103 から成る半導体装置であり、Nch型L−DMOS101 は、N型ドリフト領域12、Pウエル19、P型高濃度拡散層20、ソース拡散層21、ドレイン拡散層22、ソースコンタクト14、ドレインコンタクト16、ソース電極配線15、ドレイン電極17、ゲート電極18の各主要素から成り、SOI領域であるN型ドリフト領域12に形成されたこのNch型L−DMOS101のソース電極14と、領域11と、を電気的に導通して同電位になるように構成するデバイス構造である。

(もっと読む)

ゲート型電界効果デバイス及びその製法

本発明はゲート型電界効果デバイスに関し、その製法にも関する。一例では、ゲート型電界効果デバイスはソース/ドレーン領域ペアを含み、チャンネル領域をそれらの間に有している。ゲートはソース/ドレーン領域間でチャンネル領域に近接して受領される。ゲートはソース/ドレーン領域間にゲート幅部を有している。ゲート誘電体はチャンネル領域とゲートに近接して受領される。ゲート誘電体は少なくとも2つの異なる領域をゲートの幅部に沿って有している。これら異なる領域はそれぞれ異なる誘電率kを有する2つの異質領域を提供するように異なる材料で提供される。 (もっと読む)

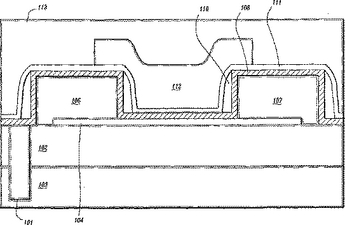

ソース及びドレインの追加絶縁層を備えた共平面型薄膜トランジスタ

共平面型薄膜トランジスタ、TFT(22)及びその製造方法において、追加の絶縁層がソースコンタクト(30)及びドレインコンタクト(32)上に設けられ、当該追加の絶縁層の第1領域(34)がソースコンタクト(30)と実質的に同一領域を占有し、当該追加の絶縁層の第2領域(36)がドレインコンタクト(32)と実質的に同一領域を占有するように形が定められる。これにより、ゲート(62)−ソース容量、及びゲート(62)−ドレイン容量が低減される。一部の構成では、このことが追加のマスク又は形を定める工程なくして実現され得る。  (もっと読む)

(もっと読む)

ブロック・コポリマーの自己集合から形成される絶縁体と有機半導体との結合構成

半導体構造であって、第1のポリマーで形成された絶縁体層を備える。更にこの構造は、第2のポリマーで構成された有機半導体層を備える。これらのポリマーが、半導体層が絶縁体層に隣接して位置する整列順序付けされたコポリマー構造へと自己集合している。この構造は、これらに限られるわけではないが、トランジスタ、複数ゲートのトランジスタ、サイリスタ、などの有機薄膜半導体デバイスであってよい。この半導体構造の製造プロセスも開示される。  (もっと読む)

(もっと読む)

テーパ状単位セル金属酸化物半導体高電圧デバイス構造

電界効果電子デバイス(100,600)(例えばVDMOS等のFET)は、誘電体層(104,608)に隣接して配置されたフィールドプレート(105,607)を有しており、当該フィールドプレートは、半導体層(103,602)に隣接して配置されている。この場合、デバイスのドリフト領域は半導体層中にある。ドーピングレベルはドリフト領域に亘って略非線形的に変化し、デバイスは略一定の低減された表面電界を示す。電界効果デバイスの製造方法は、デバイスの半導体層のドリフト領域に非線形で不均一なドーピング密度を与えることを含んでいる。この場合、半導体層及び誘電体層の両方が一定でない厚さを有している。誘電体層は、low−k誘電材料によって形成され得る。  (もっと読む)

(もっと読む)

マルチゲート構造の半導体素子及びその製造方法

本発明は、複数のスラブを含むメサ型活性領域を有する半導体素子及びその製造方法を提供する。相互連結されている第1活性領域及び第2活性領域を備え、第1活性領域は基板上にライン・アンド・スペースパターン状に形成され、相互逆方向である第1側面、第2側面及び上面をそれぞれ有する複数のスラブから構成され、第2活性領域は第1活性領域とは同じであるか、または異なる物質からなり、複数のスラブを相互連結させるように、基板上でスラブの少なくとも一端部に接して延びている半導体素子である。該半導体素子を製造するために、まず、ライン・アンド・スペースパターン状の第1活性領域を基板上に形成した後、第2活性領域を形成する。  (もっと読む)

(もっと読む)

401 - 413 / 413

[ Back to top ]