Fターム[5F110GG12]の内容

Fターム[5F110GG12]に分類される特許

2,001 - 2,020 / 2,649

半導体装置の製造方法及び半導体装置

【課題】 シリコン層の厚さが極薄膜化した場合でも、チャネル領域の端部での寄生チャネル形成を防止できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】 SOI基板10にLOCOS層15を形成し、LOCOS層15で囲まれた素子領域にnチャネルSOIトランジスタ100を形成する半導体装置の製造方法であって、素子領域のSOI層5にゲート絶縁膜21を形成する工程と、トランジスタのソースとドレインとによって挟まれるチャネル領域のLOCOS層15側の端部のSOI層5に、寄生チャネル防止用のBを導入する工程とを含み、前記Bを導入する工程はゲート絶縁膜21を形成した後で行う。

(もっと読む)

SOI構造を有する半導体装置の製造方法

【課題】ソース/ドレイン領域からの不純物の拡散を抑制することができるSOI構造を有する半導体装置の製造方法を提供する。

【解決手段】フォトレジスト6をマスクとして、シリコン層3の分離注入領域に第1導電型の不純物をイオン注入しチャネル領域よりも高い不純物濃度を有する不純物領域を形成する。フォトレジスト6をマスクとしてシリコン層3を複数に分離する。シリコン層3の主表面上にゲート絶縁膜11を介しゲート電極12を形成する。ゲート電極12をマスクとしてシリコン層3に第2導電型の不純物をイオン注入しソース/ドレイン領域14を形成する。ゲート電極12をマスクとして窒素を注入し熱処理を施すことによって窒素の濃度ピークがフィールド酸化膜13に接する前記シリコン層3表面に位置するようにする。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】読み出し及び書き込み動作時におけるスタティックノイズマージン(SNM)を改善できるメモリセルを有する半導体記憶装置を提供する。

【解決手段】フリップフロップの第1ノードにゲートが接続されたNMOSトランジスタN4と、フリップフロップの第2ノードにゲートが接続されたNMOSトランジスタN6と、NMOSトランジスタN4の電流通路の一端に、その電流通路の一端が接続されたトランスファーゲートN3と、NMOSトランジスタN6の電流通路の一端に、その電流通路の一端が接続されたトランスファーゲートN5と、ビット線対とを備える。さらに、フリップフロップの第1ノードにアノードが接続され、トランスファーゲートN5の電流通路の一端にカソードが接続されたダイオードD2と、フリップフロップの第2ノードにアノードが接続され、トランスファーゲートN3の電流通路の一端にカソードが接続されたダイオードD1とを備える。

(もっと読む)

レトログレード領域を備える横型DMOSトランジスタ及びその製造方法

【課題】レトログレード領域を備える横型DMOSトランジスタ及びその製造方法を提供する。

【解決手段】表面に隣接したソース領域及びドレイン領域と、ソース領域とドレイン領域との間のドリフト領域とを備える半導体基板を備え、ドリフト領域は、ドリフト領域の不純物濃度のピークが半導体基板の表面から離れて位置するように不純物濃度の分布を有することを特徴とするMOSトランジスタである。ドリフト領域は、半導体基板の表面下で一定の距離ほど離れているレトログレード領域を備え、ドリフト領域の不純物濃度のピークは、レトログレード領域の一部内に提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】基板断面の縦方向における耐圧を改善し、700V以上の高い耐圧を有する半導体装置およびその製造方法を提供する。

【解決手段】埋め込み酸化膜3上にあるSOI層1aの表層部に、横型MOSトランジスタ(LDMOS)が形成されてなる半導体装置10であって、シリコン(Si)より誘電率の低い低誘電率領域5が、埋め込み酸化膜3に当接して、LDMOSのソースSとドレインDの間で形成されてなる半導体装置とする。

(もっと読む)

半導体装置

【課題】LOCOS酸化膜が存在しない領域よりも先にLOCOS酸化膜が存在する領域が空乏化し、ソースからドレインに流れる電流経路の途中で電界方向が逆となり、この領域が高抵抗領域化し、電圧電流特性の劣化を引き起こし、ON抵抗の増大を招いている。

【解決手段】P型半導体基板1上のN- 型ウェル拡散層2中に形成されたドレインP+ 型拡散層6とソースP+ 型拡散層7と、LOCOS酸化膜5と、ゲート酸化膜8と、ゲート電極9と、ドレインP+ 型拡散層6の底面部からゲート酸化膜9下に達する電界緩和用の低濃度P- 型拡散層3と、低濃度P- 型拡散層3内に形成された中濃度P- 型拡散層4とを備え、ゲート電極9下部の低濃度P- 型拡散層3における表面部分で、低濃度P- 型拡散層3におけるLOCOS酸化膜5が存在しない領域Aの長さLAをLOCOS酸化膜5の存在する領域Bの長さLB よりも長くしてある。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース/ドレイン間でのリーク電流の発生が防止された半導体装置を提供する。

【解決手段】ゲート電極5およびサイドウォール絶縁膜6は、素子形成領域の上側の領域から素子分離酸化膜2の上側の領域まで延びており、かつ、チタンシリサイド膜は、少なくともサイドウォール酸化膜6および素子分離酸化膜2に隣接する領域であってサイドウォール酸化膜6の外側に位置する領域には形成されていない。

(もっと読む)

トランジスタ

【課題】酸化物半導体を活性層として、経時劣化無く優れた特性を持つ薄膜トランジスタを提供すること。

【解決手段】可撓性プラスチック基材1上にトランジスタ素子とこのトランジスタ素子を覆う保護膜9とを備えるトランジスタであって、トランジスタ素子が、ゲート電極2と、ゲート絶縁膜4と、酸化物半導体から構成された半導体活性層5と、ソース電極8及びドレイン電極7とを備えるものであり、保護膜9として水蒸気透過率が1g/m2/day以下、酸素透過率が1cc/m2/day以下、かつ、電気抵抗率が1011Ω・cm以上である無機化合物を使用する。

(もっと読む)

トランジスタ

【課題】プラスチック基材からの脱酸素、脱水蒸気をガスバリア層で遮断することにより、特性の安定した、移動度やON/OFF比が高いレベルで維持されたトランジスタを提供すること。

【解決手段】プラスチック基材上に設けられた酸化物半導体層と、該酸化物半導体層に電気的に接触して配列されたソース電極と、前記酸化物半導体層に電気的に接触すると共に前記ソース電極に離隔して配列されたドレイン電極と、前記プラスチック基材を真上から見たときに前記ソース電極と前記ドレイン電極の間に位置する前記酸化物半導体層上に設けられたゲート絶縁膜と、該ゲート絶縁膜上に設けられたゲート電極とを備えたトランジスタの、プラスチック基材と酸化物半導体層の間にガスバリア層を設けて、プラスチック基材からの脱酸素、脱水蒸気が酸化物半導体層に行かないようにした。

(もっと読む)

半導体構造物の製造方法

半導体構造物の製造方法は、歪み半導体層(14)を絶縁層(12)の上に有する基板(10)を設ける工程と、第1デバイス領域(18)を設けて、第1導電型を有する第1の複数のデバイスを形成する工程と、第2デバイス領域(20)を設けて、第2導電型を有する第2の複数のデバイスを形成する工程と、そして歪み半導体層を第2デバイス領域において厚くして、第2デバイス領域の歪み半導体層が第1デバイス領域の歪み半導体層よりも小さい歪みを持つようにする工程と、を含む。別の構成として、半導体構造を形成する方法は、第1導電型を有する第1領域(18)を設ける工程と、絶縁層(34)を、第1領域の少なくとも活性領域(32)の上に形成する工程と、絶縁層を異方性エッチングする工程と、そして絶縁層を異方性エッチングした後に、ゲート電極材料(46)を、絶縁層の少なくとも一部分の上に堆積させる工程とを備える。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】従来よりも簡単な構造でウェルに基板バイアス電圧を印加することができる半導体装置とその製造方法を提供すること

【解決手段】p型シリコン基板10と、シリコン基板10に形成され、穴が開いていない平面形状のpウェル20と、pウェル20を反転した平面形状で一体的にシリコン基板10に形成されたnウェル22と、ウェル20、22の上に形成された第1、第2ゲート電極27、28と、第1ゲート電極27の横のpウェル20に形成されたn型ソース/ドレイン領域34と、pウェルに形成され、第1の基板バイアス電圧が印加されるウェルコンタクト用p型不純物拡散領域39と、第2ゲート電極28の横のnウェル22に形成されたp型ソース/ドレイン領域35と、nウェル22に形成され、第2の基板バイアス電圧が印加されるウェルコンタクト用n型不純物拡散領域38とを有する半導体装置による。

(もっと読む)

半導体装置

【課題】トランジスタのオン、オフ状態に合わせてボディ電位を制御しなくても、履歴効

果を抑制できるようにした半導体装置を提供する。

【解決手段】p型SOIトランジスタ10と、n型SOIトランジスタ20とを含んで構

成されるインバータ回路50と、入力端子Vinとを備えた半導体装置100であって、

p型SOIトランジスタ10に並列接続された補完用のp型SOIトランジスタ60と、

n型SOIトランジスタ20に並列接続された補完用のn型SOIトランジスタ70と、

p型SOIトランジスタ60のゲート電極にその一端が接続され、入力端子Vinにその

他端が接続された第1インダクタンス65と、n型SOIトランジスタ70のゲート電極

にその一端が接続され、入力端子Vinにその他端が接続された第2インダクタンス75

と、を備えたものである。

(もっと読む)

液晶表示装置及びこの液晶表示装置に使用できる絶縁膜

【課題】低誘電率、低コスト、高耐熱、高光透過率、厚膜、高平坦の層間絶縁膜を用いることによって、低消費電力かつ低コストで、画像視認性が高い液晶表示装置を得る。

【解決手段】有機シロキサン系絶縁膜を液晶表示装置の層間絶縁膜とし、層間絶縁膜中のシリコン量に対する窒素量(N量/Si量)を元素比で0.04以上になるように制御して、層間絶縁膜の厚膜化によるクラック発生を抑制可能な限界膜厚を1.5μm以上とする。

(もっと読む)

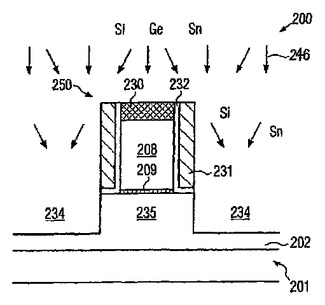

高共有半径の原子を含む埋め込まれた半導体層を利用したシリコンベースのトランジスタに歪みを生成する技術

共有半径が大きくされた原子種、例えば少なくとも一部が置換されたゲルマニウム、を導入することにより、ゲルマニウムの集塊化ならびに格子の欠陥による応力緩和のリスクを低減することができる、非常に実効的な歪みのメカニズムが提供される。錫などの、半径が増加した原子種は、水素化錫に基づくエピタキシャル成長技術により、容易に導入することができる。  (もっと読む)

(もっと読む)

逆T字チャネル型トランジスタを含む複数の型のデバイス、及びその製造方法

半導体デバイスを製造する方法が提供される。この方法は、縦型活性領域(56)と該縦型活性領域(56)の両側に延在する水平活性領域(54)とを有する第1のトランジスタ(94)を形成する工程を含んでいる。この方法はまた、縦型活性領域(58)を有する第2のトランジスタ(96)を形成する工程を含んでいる。この方法は更に、縦型活性領域(60)と該縦型活性領域(60)の片側のみに延在する水平活性領域(54)とを有する第3のトランジスタ(98)を形成する工程を含んでいる。  (もっと読む)

(もっと読む)

トランジスタ、およびその製造方法

【課題】CMOSデバイス設計に適した仕事関数をもつメタルゲート電極を提供する。

【解決手段】

トランジスタおよびその製造工程が開示されている。相補型金属酸化膜半導体(CMOS)デバイスは、第1の厚さを有する第1ゲート電極を含むPMOSトランジスタと、第2の厚さを有する第2ゲート電極を含むNMOSトランジスタとを含み、第1の厚さは、第2の厚さよりも大きい。第1ゲート電極および第2ゲート電極は、同じ材料を含んでいることが好ましく、例として、TiSiN、TaNまたはTiNを含んでいるとよい。第1ゲート電極および第2ゲート電極の厚さによって、PMOSトランジスタおよびNMOSトランジスタの仕事関数が設定される。

(もっと読む)

半導体回路とその製造方法

【課題】 pチャネルSOIトランジスタとnチャネルSOIトランジスタの両方でリーク電流を低減できるようにした半導体回路とその製造方法を提供する。

【解決手段】 SOI基板10に、pチャネルSOIトランジスタ20とnチャネルSOIトランジスタ40とを有し、pチャネルSOIトランジスタ20のソース電極21とVdd端子1とが接続され、nチャネルSOIトランジスタ40のソース電極41とVss端子5とが接続されているインバータ回路100であって、pチャネルSOIトランジスタ20のボディ23直下の高抵抗基板6に設けられたn型バックゲート電極28と、nチャネルSOIトランジスタ40のボディ43直下の高抵抗基板6に設けられたp型バックゲート電極48と、を有し、n型バックゲート電極28はVdd端子1に接続され、p型バックゲート電極48はVss端子5に接続されている。

(もっと読む)

高誘電率誘電体層を形成するための方法

本発明は、高誘電率誘電体層を作製する方法を提供する。当該方法は、第1の膜厚を有する高誘電率誘電体材料層を基板上に析出させる工程を含む。当該高誘電率誘電体材料は、バルク密度値を有し、上記第1の膜厚は、上記高誘電率誘電体層が、高誘電率誘電体材料の少なくともバルク密度値マイナス10%の密度を有するように選択する。次の工程においては、本発明に係る方法は、高誘電率誘電体層を第2の膜厚まで薄膜化する工程を含む。本発明はまた本発明の実施の形態に係る方法により作製された高誘電率誘電体層を含む半導体デバイスを提供する。  (もっと読む)

(もっと読む)

半導体装置の形成方法

【目的】SOS基板上への集積回路の製造プロセスにおいて、基板加熱中に発生する基板の反りを抑制する、あるいは反ってしまった基板をいち早く修復する。

【解決手段】SOS基板14、ポリシリコン膜15及びシリコン窒化膜17からなる構造体18の、上側表面の外周から、直径方向に距離を空けた位置に最外側の素子分離領域19aを形成することで、放熱領域21と素子領域23とを区画する。更に、放熱領域上に良熱伝導性を有するゲートポリシリコン膜25及び、タングステンシリサイド膜27を順次形成する。

(もっと読む)

応力変形させた半導体装置およびその製造方法

【課題】応力を調整し、性能向上を図った半導体装置、およびその製造法を提供すること。

【解決手段】ゲート電極104は、半導体基板(バルクシリコン基板、SOI層など)102から電気的に絶縁されている。第1側壁スペーサ110がゲート電極104の側壁に沿って形成される。上記犠牲側壁スペーサが第1側壁スペーサ110と隣接するように形成される。上記犠牲側壁スペーサおよび第1側壁スペーサ110は半導体基板102を覆っている。平坦化層は、該平坦化層の一部が上記犠牲側壁スペーサと隣接するように、半導体基板102を覆って形成されている。上記犠牲側壁スペーサが取り除かれ、エッチングによって半導体基板102内にくぼみが形成される。実質的に、上記くぼみは第1側壁スペーサ110と上記平坦化層の一部との間に配置されている。半導体材料(SiGe、SiCなど)116は上記くぼみに堆積される。

(もっと読む)

2,001 - 2,020 / 2,649

[ Back to top ]