Fターム[5F110GG48]の内容

Fターム[5F110GG48]に分類される特許

1 - 18 / 18

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

表示装置およびその製造方法

【課題】微結晶シリコンを用いたボトムゲート型の薄膜トランジスタのオン電流に対するオフ電流の割合を減少させること。

【解決手段】表示装置に含まれる薄膜トランジスタは、ゲート電極が設けられた導電層と、前記導電層の上に設けられたゲート絶縁層と、前記ゲート絶縁層の上面に接するとともに前記ゲート電極の上方に設けられ、微結晶シリコンを含む第1の半導体膜と、前記第1の半導体膜の上面に接する第2の半導体膜と、前記第2の半導体膜に電気的に接続される第1の電極と、前記第2の半導体膜に電気的に接続される第2の電極と、を含む。前記第1の半導体膜における水素濃度は、前記ゲート絶縁層との界面と前記第2の半導体膜との界面との中間で最小となり、前記第1の半導体膜と前記第2の半導体膜との境界における酸素濃度は、前記第1の半導体膜の中央および前記第2の半導体膜の中央のうち少なくとも一方の酸素濃度以下である。

(もっと読む)

電界効果素子

【課題】高移動度、高オン・オフ比の電界効果素子を提供する。

【解決手段】絶縁膜層、前記絶縁膜層上に積層されたチャネル層、及び電極としてゲート電極、ソース電極及びドレイン電極の3つを有する電界効果素子であって、前記チャネル層は表面粗さ0.2nm以上1.3nm以下であり、前記チャネル層はIn,Ga,Sn及びZnから選択される1以上の元素を含有する非晶質酸化物半導体からなる電界効果素子。

(もっと読む)

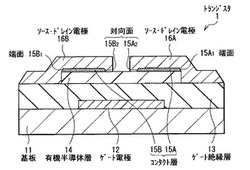

有機半導体素子の製造方法および有機半導体素子

【課題】良好な特性を有する複数の有機トランジスタを備えた有機半導体素子の製造方法を提供する。

【解決手段】有機半導体素子10は、基板11と、基板11上に設けられ、各々が液晶性有機半導体材料を含む有機半導体領域4を有する複数の有機トランジスタ20と、を備えている。このうち有機半導体領域4は、少なくとも基板11を含む支持部材17によって支持されている。そして、有機半導体素子10の製造方法は、支持部材17を準備する工程と、支持部材17上に液晶性有機半導体材料を含む連続的な有機半導体層30を設ける工程と、有機半導体層30をパターニングして複数の有機半導体領域4を形成するパターニング工程と、を備えている。ここで、パターニング工程は、凹部42および凸部41を有する凹凸版40を準備する工程と、凹凸版40の凸部41を支持部材17上の有機半導体層30に当接させることにより有機半導体層30をパターニングする当接工程と、を有している。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】良好な特性を有する複数の有機トランジスタを備えた有機半導体素子の製造方法を提供する。

【解決手段】有機半導体素子10は、基板11と、基板11上に設けられ、各々が有機半導体材料を含む有機半導体領域4を有する複数の有機トランジスタ20と、を備えている。このうち有機半導体領域4は、少なくとも基板11を含む支持部材17によって支持されている。そして、有機半導体素子10の製造方法は、支持部材17を準備する工程と、支持部材17上に有機半導体材料を含む連続的な有機半導体層30を設ける工程と、有機半導体層30をパターニングして複数の有機半導体領域4を形成するパターニング工程と、を備えている。ここで、パターニング工程は、凹部42および凸部41を有する凹凸版40を準備する工程と、凹凸版40の凸部41を支持部材17上の有機半導体層30に当接させることにより有機半導体層30をパターニングする当接工程と、を有している。

(もっと読む)

半導体装置の作製方法、および半導体装置

【課題】低温プロセスを実現する半導体装置の作製方法、及び半導体装置を提供する。

【解決手段】結晶構造を有する半導体層の一部にp型を付与する不純物元素及び水素を同時に添加することによって、一部の上層部分を非晶質化するとともに、一部の下層部分に結晶質を残存させ、加熱処理を行うことによって、一部の中の水素を拡散させる。

(もっと読む)

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

EL表示装置及びその作製方法

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

発光装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にp型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体装置

【課題】電気特性が良好な半導体装置を提供する。または、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜と、ソース配線及びドレイン配線として機能する配線との間に、微結晶シリコン膜及びシリコンカーバイド膜を有し、微結晶シリコン膜はゲート絶縁膜側に形成され、シリコンカーバイド膜は配線側に形成される。電気特性が良好な半導体装置を、生産性高く作製することができる。

(もっと読む)

半導体デバイスおよびそれを備えた表示装置

【課題】高い移動度を有し、かつ製造時に特殊な後処理工程を必要としない微結晶シリコンを用いた半導体デバイスを提供する。

【解決手段】本発明の半導体デバイスは、ナノクラスターシリコンおよびナノクリスタルシリコンを含む半導体を備え、ナノクラスターシリコンの体積が、ナノクリスタルシリコンの体積よりも大きい。

(もっと読む)

シリコンの結晶化方法、接合体、半導体装置の製造方法および半導体装置

【課題】比較的低温下で、結晶粒や成長方向の制御を確実に行うことができ、これにより半導体特性に優れたポリシリコン層を効率よく形成可能なシリコンの結晶化方法、熱処理を施すことにより良好な結晶化がなされる非晶質部を備える接合体、前記結晶化方法により形成された半導体部を備える半導体装置を製造する方法、および、この方法により製造された半導体装置を提供すること。

【解決手段】本発明のシリコンの結晶化方法は、a−Si膜30a(非晶質部)と、c−Siの種結晶30cとを用意する工程と、a−Si膜30aの表面と種結晶30cの表面に、それぞれエネルギーを付与する工程と、a−Si膜30aと種結晶30cとを接合し接合体305を得る工程と、接合体305を加熱することにより、a−Si膜30aを結晶化する工程とを有する。これにより、a−Si膜30aと種結晶30cとの接合界面が成長核となって結晶化が進行する。

(もっと読む)

有機半導体薄膜、有機薄膜トランジスタ、及び有機薄膜トランジスタの製造方法

【課題】本発明の目的は、高移動度、かつ、熱安定性に優れた有機薄膜トランジスタを提供することにある。

【解決手段】低分子有機半導体化合物を用いて形成した膜に、少なくとも1つの処理を施すことで、低分子有機半導体化合物分子の少なくとも2分子が互いに結合して形成した重合体を膜の一部に含有することを特徴とする、有機半導体薄膜。

(もっと読む)

半導体装置の作製方法

【課題】材料や形成されたパターンが異なる複数の層が積層された構造の半導体装置において、CMP法による研磨処理やSOG膜成膜による平坦化処理を行わなくても平坦化でき、さらに基板材料を選ばず、簡便に平坦化を行う方法を提供することを課題とする

【解決手段】異なる層が複数積層されて形成された半導体装置において、絶縁膜に開口部を形成し、その開口部内に配線(電極)または半導体層を形成することにより、絶縁膜および配線(電極)または半導体層上に形成される絶縁膜に対してCMP法による研磨処理またはSOG膜の成膜による平坦化を行わなくても表面の平坦化を行うことができる。

(もっと読む)

半導体装置、半導体装置の製造方法、電気光学装置および電子機器

【課題】ソース部、ドレイン部およびチャネル部が透明酸化物系材料で一体形成された透明酸化物層を有する半導体装置、その製造方法、かかる半導体装置を備える電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置1は、基板8と、基板8の少なくとも一方の面側に設けられたソース部3およびドレイン部4と、ソース部3およびドレイン部4と一体的に形成された、ソース部3およびドレイン部4の厚さより小さい厚さのチャネル部5とを備える透明酸化物層2と、ゲート部7と、ゲート絶縁層6とを有する。

(もっと読む)

半導体素子

【課題】 基板の面方向での熱膨張係数或いは熱収縮係数の異方性により、基板上に形成される半導体素子特性の劣化、及び歩留まり低下を抑える。

【解決手段】 基板の面方向で熱収縮率、または熱膨張係数の異方性を有するプラスチックフィルム基板1上に薄膜トランジスタし、基板の熱収縮率、または熱膨張係数の最も大きい方向7と薄膜トランジスタのチャネルの電流を流す方向8とが非平行となるように、チャネルを形成する。それにより、プラスチックフィルム基板上に安定かつ均一な電気特性を持つ薄膜トランジスタを提供する。

(もっと読む)

結晶性Si層形成基板の製造方法、結晶性Si層形成基板及び結晶性Siデバイス

プラスチック基板上にアモルファスSi層を形成し、前記アモルファスSi層をレーザ照射により結晶化して得られる結晶性Si層形成基板の製造方法において、前記レーザの発振波長の光に対する前記プラスチック基板の透過率が30〜100%であることを特徴とする方法。 (もっと読む)

半導体装置の製造方法

【課題】 優れた特性を有する多結晶シリコン膜を備えた半導体装置を高い歩留まりで製造することが可能な半導体装置の製造方法を提供する。

【解決手段】 石英ガラスや無アルカリガラスなどの基板1上に、非晶質シリコン膜2aを形成する。その非晶質シリコン膜2a上にWシリサイド膜(導電膜)4bを形成する。そして、Wシリサイド膜(導電膜)4bに対し、高周波やYAGレーザービームなどの電磁波を照射することにより、Wシリサイド膜(導電膜)4bを発熱させ、この熱を利用して、非晶質シリコン膜2aを多結晶シリコン膜2に変える。

(もっと読む)

1 - 18 / 18

[ Back to top ]