Fターム[5F110HJ17]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物の導入方法 (4,201) | 拡散 (325) | 気相拡散(雰囲気中) (184)

Fターム[5F110HJ17]の下位に属するFターム

プラズマ雰囲気中 (150)

Fターム[5F110HJ17]に分類される特許

21 - 34 / 34

半導体装置及びその製造方法

【課題】フォトマスクの枚数を低減しながらも、容易且つ高精度に半導体装置を製造する。

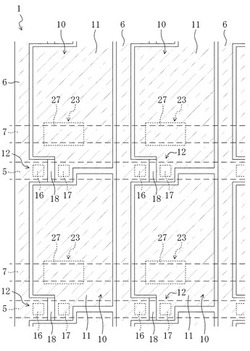

【解決手段】ゲート配線5と、ソース配線6と、ゲート配線5及びソース配線6に接続された薄膜トランジスタ12と、薄膜トランジスタ12に接続された絵素電極11とを備えた半導体装置1を製造する場合に、絵素電極11とソース配線6とを同時にパターン形成する。

(もっと読む)

半導体装置の製造方法

【課題】オフリーク電流を押さえて高い電流駆動力を有し、オフセット電圧が極力低減された微細な半導体装置の製造方法を提供する。

【解決手段】半導体基板に、一対の素子分離絶縁膜を離間して形成し、素子領域を画定する工程と、半導体基板の素子領域におけるチャネル領域の上に、ゲート絶縁膜を介してゲート長30nm以下のゲート電極を形成する工程と、ゲート電極側面にオフセットスペーサーを形成する工程と、オフセットスペーサー及びゲート電極をマスクとしてゲート電極の直下を除く半導体基板に不純物を導入し、フラッシュランプアニールを用いて1000℃以上で100msec以下の極短時間加熱処理を施して不純物を活性化し、ゲート電極の端部から10nm以下の距離で離間した不純物拡散領域を形成する工程と、半導体基板の全面に層間絶縁膜を形成してコンタクトホールを開口し、導電材料で埋め込んで配線を形成する工程とを具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】薄膜のSOI層を持つSOI−MOSFETにおいて、基板浮遊効果を抑制するボディコンタクト構造の半導体装置の製造方法を提供する。

【解決手段】絶縁体上の半導体層上において、素子領域及びボディコンタクト領域を覆うCMPマスクを形成する工程と、全体を前記CMPマスクの材料とは異なる第2の絶縁体で覆い続いてCMPにより第2の絶縁体を平坦化する工程と、CMP工程後により露出した前記CMPマスク材料を除去し、露出した半導体層にはゲート絶縁膜、ゲート電極及び第1導電型のソース/ドレイン領域を持つ電界効果型トランジスタ、およびまたは第2導電型の不純物が高濃度に導入されたボディコンタクト領域を形成することを特徴とする。

(もっと読む)

半導体装置

【課題】ゲート長の微細化に対応し、完全空乏化素子として動作させることができ、ジュール熱に起因した発熱や基板浮遊効果が低減できる半導体装置を提供する。

【解決手段】p型半導体基板11上に形成された基板突起部31Aと、突起部31A上にゲート絶縁膜13を介して形成されたゲート電極14と、ゲート電極14を挟むように突起部31Aに形成されたソース領域15及びドレイン領域16と、基板突起部31Aを挟む半導体基板11上に形成された素子分離絶縁膜12と、素子分離絶縁膜12下の半導体基板11内に形成された第1、第2不純物領域17とを有する。第1及び第2不純物領域17同士が基板突起部31A下の半導体基板11内で接続され、ゲート電極14がその側面上に形成されている基板突起部31Aの高さ及び幅方向の長さは、ソース領域15及びドレイン領域16が形成される基板突起部31Aの高さ及び幅方向の長さよりそれぞれ短い。

(もっと読む)

半導体装置およびその製造方法

【課題】P型およびN型III−V族窒化物半導体層の両方に対して良好に接続される電極を有する半導体装置を提供する。

【解決手段】この電界効果トランジスタは、サファイア基板41上に窒化物半導体積層構造部2を配置して構成されている。窒化物半導体積層構造部2は、N型GaN層5、P型GaN層6、およびN型GaN層7を有している。窒化物化合物半導体積層構造部2には、断面V字形のトレンチ16が形成されており、このトレンチ16の壁面17にゲート絶縁膜が形成され、さらに、このゲート絶縁膜19を挟んで壁面17に対向するようにゲート電極20が形成されている。ソース電極25は、P型GaN層6にオーミック接触する第1電極部251と、N型GaN層7にオーミック接触する第2電極252とを接合して構成されている。第1電極部251と第2電極部252とは異なる金属材料からなる。

(もっと読む)

酸化物膜をチャネルに用いた電界効果型トランジスタ及びその製造方法

【課題】トランジスタの特性(Id−Vg特性)にばらつきが生じる場合があった。

【解決手段】酸化物膜を半導体層11として有する電界効果型トランジスタであって、酸化物膜の中に、水素又は重水素が添加されたソース部位及びドレイン部位を有している。または、酸化物膜の中に、チャンネル部位18とソース部位16とドレイン部位17とを有し、ソース部位とドレイン部位との水素又は重水素の濃度がチャンネル部位の水素又は重水素の濃度よりも大きい。ソース部位とドレイン部位が、ゲート絶縁層を介して配されるゲート電極と自己整合して配され、且つ、コプレーナ構造からなる構成をとることができる。

(もっと読む)

ナノワイヤ・トンネルトランジスタ

トランジスタが、真性または低濃度ドーピング領域(26,28)によって分離されたソース(24)およびドレイン(29)を有するナノワイヤ(22,22’)を備えている。真性または低濃度ドーピング領域(26,28)とソース(24)またはドレイン(29)の一方との間の界面にポテンシャルバリアが形成される。ポテンシャルバリアの付近にゲート電極(32)を設けて、ゲート電極(32)に適切な電圧を印加することによって、ポテンシャルバリアの実効的な高さおよび/または幅を調整することができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】可及的に簡略な構成で、かつ高集積度、高性能の半導体装置を得ることを可能にする。

【解決手段】半導体基板1上に板状に設けられた第1導電型の第1半導体領域3と、第1半導体領域の第1側面に設けられた第1強誘電体絶縁膜4と、第1強誘電体絶縁膜の第1半導体領域と反対側の面に設けられた第1ゲート電極6と、第1半導体領域の第2側面に設けられた第2強誘電体絶縁膜5と、第2強誘電体絶縁膜の第1半導体領域と反対側の面に設けられた第2ゲート電極7と、第1及び第2ゲート電極に挟まれるように第1半導体領域に形成されるチャネル領域と、チャネル領域の両側の第1半導体領域に設けられた第2導電型の第1ソース・ドレイン領域8と、を備え、第1半導体領域の厚さが第1半導体領域の不純物濃度で決まる空乏層の最大厚さの二倍よりも薄い。

(もっと読む)

半導体構造およびその製造方法(相補型金属酸化膜半導体)

【課題】 高いキャリア移動度を有する新規かつ改善された半導体構造およびその製造方法を提供する。

【解決手段】 移動度の向上に関して性能が改善された、(110)面上に形成された半導体(例えば相補型金属酸化膜半導体(CMOS))構造は、単一の引張応力ライナ、圧縮応力のかかった浅いトレンチ分離(STI)領域、および引張応力埋め込みウェルの少なくとも1つを含み、これを(110)基板とともに用いて、nFETおよびpFETの双方のキャリア移動度を向上させる。

(もっと読む)

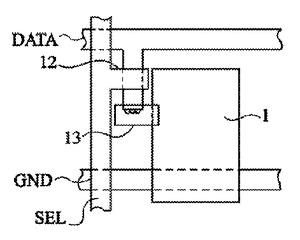

平面ディスプレイアクティブプレート

本発明はマトリクス平面ディスプレイアクティブプレートを製造する方法に関するものであり、各セルが電極プレート(1)を備え、そのプレートはトランジスタ(2)により第1導電ラインに接続されており、各セルの位置にある各第1導電ラインが有している絶縁体に覆われた隆起部(11)を形成するステップと、各隆起部の端部をエッチングまたは多孔質化するステップと、エッチングまたは多孔質化された各端部に、VLS工程を用いてp-i-pまたはn-i-n半導体構造を成長させるステップと、該半導体構造の開放端にコンタクトを設置し、前記半導体構造の中央部分にゲートを形成するステップとを有することを特徴とする。  (もっと読む)

(もっと読む)

結晶性Si層形成基板の製造方法、結晶性Si層形成基板及び結晶性Siデバイス

プラスチック基板上にアモルファスSi層を形成し、前記アモルファスSi層をレーザ照射により結晶化して得られる結晶性Si層形成基板の製造方法において、前記レーザの発振波長の光に対する前記プラスチック基板の透過率が30〜100%であることを特徴とする方法。 (もっと読む)

半導体装置

【課題】 半導体装置に於いて、高い短チャネル効果耐性並びに高い電流駆動能力を保ちつつ、ゲート絶縁膜中の電場の緩和を図る。その結果として高電流駆動能力且つ高信頼性の、高性能な微細半導体装置を提供する。

【解決手段】 チャネルの形成される領域が稜を持つ電界効果トランジスターに於いて、稜の近傍に於いてはゲート絶縁膜が他の領域よりも厚く形成されている、ないしゲート絶縁膜は積層であり、積層を形成する層の内で誘電率の低い層が稜の近傍に於いて他の領域よりも厚く形成されている。それ故、チャネル領域の電位に対するゲート電極の制御性は良好に保たれたままでゲート絶縁膜中に生ずる電場強度の緩和が図られ、その結果として高電流駆動能力且つ高信頼性の高性能微細半導体装置を実現する。

(もっと読む)

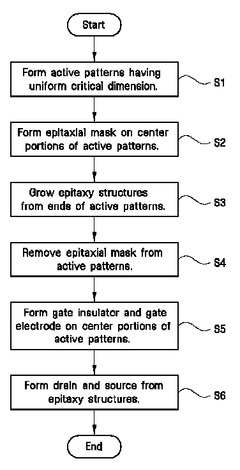

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

MIS型電界効果トランジスタ

下地SiGe層1上に歪みSi層2をエピタキシャル成長させ、ゲート絶縁膜3aとゲート電極4aを形成した後、ゲート電極4aをマスクにして、下地SiGe層1及び歪みSi層2に不純物をイオン注入し(図2(a))、活性化のための熱処理を行ってソース・ドレイン領域6を形成する(図2(b)、(c))。このとき、歪みSi層2の膜厚は、最終的なMISFETのソース・ドレイン領域6の不純物濃度が最大となる深さをTp(=Rp)としたとき、2Tp以下にする。 (もっと読む)

21 - 34 / 34

[ Back to top ]