Fターム[5F110HK04]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 金属 (18,241) | 高融点金属 (4,055)

Fターム[5F110HK04]に分類される特許

2,001 - 2,020 / 4,055

表示装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一とする。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置において、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二種類の酸化物半導体層とを組み合わせて構成され、ゲート電極層と重なるチャネル形成領域となる半導体層上にチャネル保護層が設けられた逆スタガ型薄膜トランジスタが設けられた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続するパッド部が設けられている。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

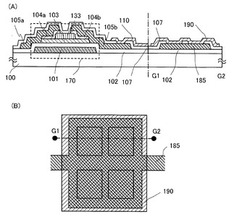

【解決手段】ゲート電極101を被覆するゲート絶縁層102と、ゲート絶縁層102上においてゲート電極101と重畳する第1酸化物半導体層103と、第1酸化物半導体層103上においてゲート電極と端部が重畳し、導電層105aと第2酸化物半導体層104aが積層された一対の第1配線層38及び第2配線層39とを有する非線形素子170aを用いて保護回路を構成する。ゲート絶縁層102上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子170aの特性を向上させることができる。

(もっと読む)

透明薄膜トランジスタ及び画像表示装置

【課題】配線抵抗を低下させて、均一かつ確実に動作させる透明薄膜トランジスタ及び画像表示装置を提供すること。

【解決手段】実質的に透明な基板と、基板上に実質的に透明な導電材料の第1の薄膜と金属材料の第2の薄膜とを2層以上積層して形成されたゲート配線と、ゲート配線上に形成された実質的に透明なゲート絶縁膜と、ゲート絶縁膜上に形成された実質的に透明な半導体活性層と、実質的に透明な半導体活性層を挟んで離間して形成された実質的に透明な導電材料の第5の薄膜と金属材料の第6の薄膜とを2層以上積層して形成されたソース配線と、実質的に透明な半導体活性層を挟み、ソース配線に離間して実質的に透明な導電材料の第7の薄膜で形成されたドレイン電極と、を備えることを特徴とする透明薄膜トランジスタ。

(もっと読む)

表示装置およびその製造方法

【課題】ドレイン電極とソース電極との間に流れるオフ電流を低減する。

【解決手段】表示装置は、ガラス基板101を覆うSiN膜102上に形成されたゲート電極103およびゲート絶縁膜104と、ゲート絶縁膜104上のゲート電極103に対応する領域に形成された、能動層となるpoly−Si層107と、a−Si:H層108と、コンタクト層となるn+Si層109と、がこの順で積層された島状の半導体積層構造と、n+Si層109上に互いに離間して配置されたドレイン電極115aおよびソース電極115bと、少なくとも半導体積層構造110の側面を被覆するSiN膜118と、を有するLTPS−TFT100を含む。n+Si層109は、a−Si:H層108まで達する分離溝によって、ドレイン電極115aに導通するn+Si層109aとソース電極115bに導通するn+Si層109bとに分離されている。

(もっと読む)

半導体装置の製造方法

【課題】安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上にGaN系半導体層を形成する工程と、ALD装置内で、ゲート絶縁膜の成長温度に比べ高い温度で熱処理を実施し、前記GaN系半導体層の表面のフッ素を除去する工程S20と、前記フッ素を除去する工程S20の後、前記ALD装置内で、前記GaN系半導体層の表面に前記ゲート絶縁膜を形成する工程S16と、前記ゲート絶縁膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

表示装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一とする。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置において、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けられた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続するパッド部が設けられている。

(もっと読む)

表示装置およびその作製方法

【課題】表示パネルに設けられる共通接続部として適した構造を提供することを目的の一とする。

【解決手段】画素部の外側領域に設けられる共通接続部は、ゲート絶縁層と同じ層で形成された絶縁層上に、第2酸化物半導体層と同じ層で形成された酸化物半導体層と、導電層と同じ層で形成された導電層(共通電位線とも呼ぶ)とが積層された構成を有し、第1酸化物半導体層上に設けられた層間絶縁層の開口部を介して導電層(共通電位線とも呼ぶ)が共通電極と接続しており、画素電極と対向する電極が導電性粒子を介して共通電極と電気的に接続する。

(もっと読む)

金属酸化物前駆体層の作製方法、金属酸化物層の作製方法及び電子デバイス

【課題】成膜性(造膜性ともいう)の良好な金属酸化物前駆体層の作製方法、作製された該金属酸化物前駆体層を用いた金属酸化物層の作製方法を提供し、且つ、該金属酸化物の作製方法を用いて、移動度が高く、On/Off比が高く、敷電圧が低い電子デバイスを提供する。

【解決手段】基材の上に金属イオンを含む溶液を基材に塗布する金属酸化物前駆体層の作製方法において、該基材の温度(℃)を該溶液の主溶媒の沸点(℃)の50%〜150%の温度範囲に調整して前記溶液を塗布、成膜する工程を有することを特徴とする金属酸化物前駆体層の作製方法。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極101を被覆するゲート絶縁層102と、ゲート絶縁層102上においてゲート電極101と重畳する第1酸化物半導体層103と、第1酸化物半導体層103のチャネル形成領域と重なる領域を覆うチャネル保護層と、チャネル保護層上においてゲート電極と端部が重畳し、導電層105aと第2酸化物半導体層104aが積層された一対の第1配線層38及び第2配線層39とを有する非線形素子170aを用いて保護回路を構成する。ゲート絶縁層102上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子170aの特性を向上させることができる。

(もっと読む)

MIS電界効果トランジスタ及び半導体基板の製造方法

【課題】高温特性を改善した高集積、高速且つ高性能なMISFETを得ること。

【解決手段】半導体基板に絶縁膜を埋め込んだトレンチ素子分離領域を選択的に設け、この絶縁分離された半導体基板上に、半導体基板と同じ第1の半導体を、筒状構造を有して縦方向にエピタキシャル成長させ、この第1の半導体層に自己整合して、格子定数がやや大きい第2の半導体を内側面の横方向にエピタキシャル成長させることにより、第1の半導体層に歪みを加える。この第2の半導体層の上部内側面を除く内側面に接して絶縁膜を設け、この絶縁膜の側面間を空孔となし、この空孔に栓をするように、第2の半導体層の上部内側面間に導電膜を設ける。歪み半導体層の外側面にはゲート絶縁膜を介してゲート電極を設ける。歪み半導体層及び第2の半導体層の上部にはドレイン領域を設け、歪み半導体層及び第2の半導体層の下部且つ半導体基板の表面にはソース領域を設けておき、配線体をそれぞれの領域に接続した縦型のMISFETを構成すること。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜におけるリーク電流を抑制し、安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上10にGaN系半導体層15を形成する工程と、GaN系半導体層上15に、TMAと、O2またはO3とを用い、酸化アルミニウムからなるゲート絶縁膜18をALD法により形成する工程と、ゲート絶縁膜18の上にゲート電極24を形成する工程と、を含む。本半導体装置の製造方法によれば、ゲート絶縁膜中のリーク電流を抑制し、安定なFET特性を得ることができる。

(もっと読む)

有機薄膜トランジスタ

【課題】高い誘電率、架橋性官能基を備えた溶液法が可能なポリマー類、ならびにかかるポリマーにより形成された、一定の厚さ、高い誘電率、および高いキャパシタンスを有するゲート誘電体層を含む薄膜トランジスタを提供することにある。

【解決手段】本発明は、ゲート誘電体層を含む薄膜トランジスタであって、該誘電体層は、ポリ(ヒドロキシアルキルアクリレート−co−アクリロニトリル)系のポリマー、例えばポリ(2−ヒドロキシエチルアクリレート−co−メタアクリロニトリル)コポリマーなどを含む。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】移動度の高い薄膜トランジスタ及び生産効率の高い薄膜トランジスタの製造方法を提供する。

【解決手段】基体の上に、少なくともゲート電極、ゲート絶縁層及び活性層を有する薄膜トランジスタにおいて、該活性層が、複数の孤立した導電性領域と酸化物半導体からなることを特徴とする薄膜トランジスタ。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】本発明の目的は、マイクロ波加熱を用いることによって、塗布膜から形成される酸化物半導体の前駆体の酸化膜への変換を容易として、酸化物半導体膜を活性層とする薄膜トランジスタ素子の生産効率を向上させることにある。

【解決手段】酸化物半導体の前駆体薄膜を加熱して酸化物半導体膜に転化させる薄膜トランジスタの製造方法において、マイクロ波を吸収し発熱する材料を前駆体薄膜の内部、又は前駆体薄膜に接して配置し、この材料にマイクロ波を照射することにより、酸化物半導体膜への転化を行うことを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】インジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含む酸化物半導体膜を用いる薄膜トランジスタにおいて、ソース電極層またはドレイン電極層のコンタクト抵抗を低減した薄膜トランジスタ及びその作製方法を提供することを課題の一つとする。

【解決手段】ソース電極層及びドレイン電極層上にIGZO半導体層を設け、ソース電極層及びドレイン電極層とゲート絶縁層との間に、IGZO半導体層よりも酸素濃度の低いソース領域及びドレイン領域を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、導電層41と第2酸化物半導体層40が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部と第2酸化物半導体層40の側面部及び上面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークを低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

液晶表示装置用アレイ基板及びその製造方法、液晶表示装置

【課題】液晶表示装置用アレイ基板及びその製造方法、これを具備した液晶表示装置を得る。

【解決手段】本発明に係る液晶表示装置用アレイ基板及びその製造方法、これを具備した液晶表示装置は、光漏洩電流を減少させることができる遮断膜(Shielding Metal)を利用して光損失を除去することで、光漏洩電流を最小化して画質を向上させることができる。

(もっと読む)

電極の製造方法、これを用いた薄膜トランジスタ素子及び有機エレクトロルミネッセンス素子

【課題】透明導電性微粒子を含む流動性材料の塗布により、ゲート電極を形成する方法において、従来よりも低抵抗、かつ充分な表面平滑性をもった透明導電膜の製造方法を提供する。

【解決手段】ガラス基板106上に、金属酸化物微粒子(ITO)及び金属酸化物の前駆体を含む薄膜104”を塗布する。この薄膜にマイクロ波を照射することにより、前駆体が発熱体として作用し、焼成され、導電性薄膜を形成する。これをパターンニングしゲート電極104とする。ついで、ゲート絶縁膜105を形成し、半導体前駆体を塗布、乾燥し、半導体前駆体材料薄膜101’を得る。これにマイクロ波を照射することにより、ゲート電極が発熱し、この熱により半導体前駆体材料薄膜が加熱され、酸化物半導体膜に変換され半導体層101が形成される。マスクを介して金を蒸着し、ソース、ドレイン電極102,103を形成し、薄膜トランジスタとする。

(もっと読む)

半導体装置およびその製造方法

【課題】 塗布技術や印刷技術を用いて形成した薄膜トランジスタを微細に形成し、さらに、ホトコンを低減することにより、高性能な薄膜トランジスタ、及びそれを用いた半導体装置を安価に提供すること。

【解決手段】 絶縁基板上に、ソース・ドレイン電極、ゲート絶縁膜、有機半導体層、ゲート電極の各部材が積層された薄膜トランジスタ、およびそのトランジスタを含む表示装置、ICタグ装置、センサー装置において、有機半導体層は塗布法もしくは印刷法で形成されており、ソース・ドレイン電極上の有機半導体層の概略パターン平面形状の少なくとも一部(少なくともチャネル長方向の端部)がソース・ドレイン電極上のパターン形状と自己整合的な形状である構成とした。

(もっと読む)

2,001 - 2,020 / 4,055

[ Back to top ]