Fターム[5F110HK04]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 金属 (18,241) | 高融点金属 (4,055)

Fターム[5F110HK04]に分類される特許

4,041 - 4,055 / 4,055

有機半導体材料、有機トランジスタ、電界効果トランジスタ、スイッチング素子及びチアゾール化合物

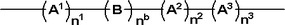

下記一般式で表される部分構造を持つ化合物を含有することを特徴とする有機半導体材料、それを用いた有機トランジスタ及び電界効果トランジスタ、及び該有機トランジスタまたは該電界効果トランジスタを用いるスイッチング素子。

(式中、Bはチアゾール環をもつユニットを表し、A1,A2はそれぞれ独立にアルキルを置換基として持つユニットを表し、A3は二価の連結基を表し、nbは1〜20の整数を表し、n1、n2はそれぞれ独立に0〜20の整数を表し、n3は0〜10の整数を表す。)

(もっと読む)

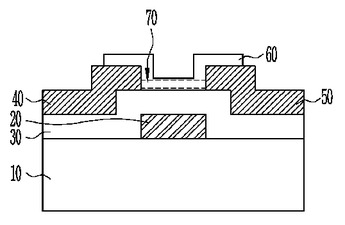

電界効果トランジスタ及びそれを用いた表示装置

有機物を含有する半導体層(15)と、少なくとも互いに電気的に非接触である第一電極(16)、第二電極(12)及び第三電極(14)を含む電界効果トランジスタであって、半導体層(15)の上方に第一電極(16)が配置され、半導体層(15)の下方に第二電極(12)が配置され、半導体層(15)の側方に第三電極(14)が配置され、半導体層(15)は第一電極(16)、第二電極(12)及び第三電極(14)から選ばれるいずれか2つの電極と電気的に接合され、各電極(12,14,16)間には電気的絶縁体層(13,17)を介在させ、第一電極(16)は半導体層(15)の上方を半導体層(15)の外周部より外側にはみ出して覆っている。これにより、有機半導体を用いた電界効果トランジスタであっても、空気や水に強く、かつ長寿命な電界効果トランジスタ及びそれを用いた表示装置を提供する。 (もっと読む)

電界効果トランジスタ及び電気素子アレイ、並びにそれらの製造方法

本発明の電界効果トランジスタ(100)は、基板(101)上に形成されたゲート電極(102)と、ゲート電極(102)上に形成されたゲート絶縁層(103)と、ゲート絶縁層(103)上に形成されたソース電極(106,109)およびドレイン電極(104)と、ソース電極(106,109)およびドレイン電極(104)に接触して、それらの間に形成されたカーボンナノチューブを含むn型半導体層(108)と、n型半導体層(108)上に形成されカーボンナノチューブが本来有するp型をn型に極性転換して固定するためのn型改質ポリマー層(110)とを含む。半導体保護層(110)形成と同時にCNTの半導体特性転化を行うことで、工程を簡便なものとする。これにより、空気中でも安定なCNT−FET回路を提供できる。 (もっと読む)

金属絶縁体相転移スイッチングトランジスタ及びその製造方法

金属絶縁体相転移高速スイッチングトランジスタ及びその製造方法を提供する。金属絶縁体相転移高速スイッチングトランジスタは、シリコン基板上のゲート電極(バックゲート構造)と、電場の変化により絶縁体相から金属相に又はその逆に変化するVO2の金属絶縁体相転移チャネル層とを備える。この製造方法により、高い電流利得特性を有し、熱的に安定した金属絶縁体相転移スイッチングトランジスタを作製することができる。

(もっと読む)

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

薄膜トランジスタの封止方法

ゲート電極と、ゲート誘電体と、ソースおよびドレイン電極と、半導体層とを含む薄膜トランジスタを提供する工程と、封止材料をアパーチャマスクのパターンを通して前記半導体層の少なくとも一部の上に蒸着する工程とを含む、薄膜トランジスタの封止方法。  (もっと読む)

(もっと読む)

アセン−チオフェン半導体

有機半導体として有用であるアセン−チオフェン化合物が開示されている。有機薄膜トランジスタ中の半導体層として本化合物を用いた時、本化合物は、ペンタセンに匹敵する電荷キャリア移動度および電流オン/オフ比のようなデバイス特性を示す。本発明の少なくとも1種の化合物を含む半導体デバイスならびに薄膜トランジスタまたはトランジスタアレーおよびエレクトロルミネセントランプなどの半導体デバイスを含む物品も記載されている。  (もっと読む)

(もっと読む)

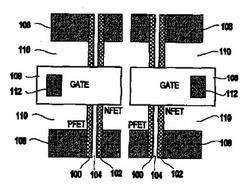

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

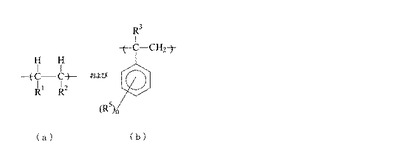

有機高分子、電子デバイス、および方法

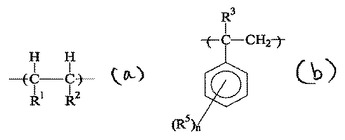

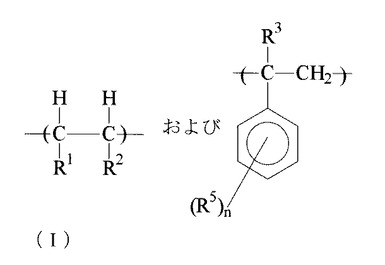

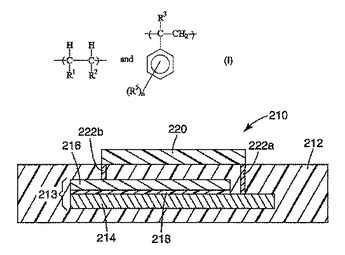

電子デバイスに使用する有機高分子であって、この高分子は、式(a)および(b)の反復単位を含む。式中、高分子内の少なくとも1個の反復単位がR4を含むことを条件として、各R1が、独立してH、アリール基、Cl、Br、I、または架橋可能な基を含む有機基であり、各R2が、独立してH、アリール基、またはR4であり、各R3が、独立してHまたはメチルであり、各R5が、独立してアルキル基、ハロゲン、またはR4であり、各R4が、独立して、少なくとも1個のCN基を含み、CN基あたり約30〜約200の分子量を有する有機基であり、n=0〜3である。これらの高分子は、有機薄膜トランジスタなどの電子デバイスに有用である。

(もっと読む)

(もっと読む)

有機ポリマー、ラミネート、およびコンデンサー

コンデンサーなどのラミネートに使用するための有機ポリマー。このポリマーは、式:

【化1】

で示される反復単位を含む。上記式中、各R1は、独立して、H、アリール基、Cl、Br、I、または架橋性基を含む有機基であり;各R2は、独立して、H、アリール基、またはR4であり;各R3は、独立して、Hまたはメチルであり;各R5は、独立して、アルキル基、ハロゲン、またはR4であり;各R4は、独立して、少なくとも1つのCN基を含みかつCN基1つあたり約30〜約200の分子量を有する有機基であり;そしてnは0〜3に等しく;ただし、ポリマー中の少なくとも1つの反復単位は、R4を含む。

(もっと読む)

(もっと読む)

自己組織化単分子層を含む電子デバイスおよびこれを製造する方法

【課題】 電子特性が向上した分子層を有する電子デバイスを提供すること。

【解決手段】 電子デバイスは、ソース領域およびドレイン領域と、ソース領域およびドレイン領域に隣接して配置され、少なくとも1つの共役分子を含む自己組織化単分子層と、自己組織化単分子層に隣接した導電性基板と、を含む。

(もっと読む)

有機薄膜トランジスタ

【課題】特殊な技術を要せず、簡単な製造方法でキャリア移動度が高い有機薄膜トランジスタを提供すること。

【解決手段】有機半導体層に重量平均分子量2000以上のπ共役系ポリマー及び分子量2000以下のπ共役系オリゴマーを含有することを特徴とする有機薄膜トランジスタ。

(もっと読む)

液晶表示装置およびその作製方法

【課題】 IPS方式の液晶表示装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】 本発明では、チャネル・エッチ型のボトムゲートTFT構造を採用し、ソース領域119及びドレイン領域120のパターニングとソース配線121及び画素電極122のパターニングを同じフォトマスクで行うことを特徴とする。

(もっと読む)

薄膜トランジスタとその製造方法

【課題】 ソース/ドレイン電極材料に銅を用いた場合の加工時のバリアメタル層のアンダーカットに起因する特性不良を防止し、低抵抗配線が充分に実現できるTFTの構造とその製造方法を提供する。

【解決手段】 本発明のTFTの構造は、ガラス基板2上のゲート電極3と、ゲート絶縁膜4と、ゲート絶縁膜4上にゲート電極3に対向配置された半導体能動層5と、半導体能動層5の両端部上に設けられたオーミックコンタクト層6と、各オーミックコンタクト層6を介して半導体能動層5に電気的に接続されたソース電極7、ドレイン電極8とを有している。そして、ソース電極7およびドレイン電極8が銅で形成され、これらソース電極7、ドレイン電極8の下面のうち、各オーミックコンタクト層6の上面上に位置する領域にのみバリアメタル層9が設けられている。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

4,041 - 4,055 / 4,055

[ Back to top ]