Fターム[5F110HK06]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 金属 (18,241) | 合金 (2,248)

Fターム[5F110HK06]に分類される特許

2,001 - 2,020 / 2,248

液晶ディスプレイ用のガラス基板上に、パターン形成された導電層を作成するための方法および装置

【解決手段】液晶ディスプレイ(LCD)の一部にされる金属特徴を定めるための方法およびシステムが提供される。この方法は、ガラス基板に対して施され、ガラス基板は、ガラス基板上にまたはガラス基板の層上に定められたブランケット導電性金属層(例えば障壁層)を有する。ブランケット導電性金属層の上には、反転フォトレジストマスクが塗布される。次いで、反転フォトレジストマスクの上に、めっきメニスカスが形成される。めっきメニスカスは、少なくとも電解液およびめっき化学剤を含み、めっきメニスカスは、ブランケット導電性金属層の上の、反転フォトレジストマスクによって覆われていない領域内に金属特徴を形成する。 (もっと読む)

半導体素子

【課題】結晶性や配向性の高い有機半導体層を有する半導体素子を提供する。

【解決手段】基体上に、一種以上の高分子化合物を含有する層と、該一種以上の高分子化合物を含有する層と接する有機半導体層とを、少なくとも有し、前記高分子化合物のうち少なくとも一種が、1個以上の2級または3級の脂肪族アミノ基を有する高分子化合物であり、前記脂肪族アミノ基を有する高分子化合物のアミノ基が側鎖および/または分岐鎖上に存在し、前記高分子化合物を含有する層がポリシロキサン化合物を含有する半導体素子。

(もっと読む)

表示装置の修理装置及び修理方法

【課題】本発明は、表示装置の修理装置及び修理方法に関する。

【解決手段】複数の信号線が形成されている第1基板を含む表示装置の修理装置は、前記信号線に焦点を合せて所定の波長及びフェムト秒乃至ピコ秒のパルス幅を有するレーザー光750を照射するレーザー装備700を含み、前記所定の波長の範囲は、750nm乃至850nmまたは1000nm乃至1100nmである。このような方式で、適切なパルス幅及び波長を有するレーザー装備700を選択し、特にフェムト秒乃至ピコ秒のパルス幅及び750nm乃至850nmまたは1000nm乃至1100nmの波長範囲のレーザー光を使用すれば、テスト段階別に別途の修理装置を使用せずに一つのレーザー装備を使用して全工程で修理を行うことができる。

(もっと読む)

半導体素子用電極の製造方法、トランジスタの製造方法、PINダイオードの製造方法、回路基板、電気光学装置、電子機器

【課題】ドーパントの影響を回避しつつ、高導電性半導体層に被覆された電極の形成に要する工程数を削減可能な製造技術を提供すること。

【解決手段】半導体素子を構成する電極を製造する方法であって、少なくとも一方面が絶縁性無機物からなる基板(10)上に、所定形状に整形された導電膜(16)形成する第1工程と、上記導電膜の表面にドーパントを含んだ液体シリコン材料(52,54)を塗布する第2工程と、上記液体シリコン材料を熱処理によって固化させることにより上記ドーパントが添加された導電性シリコン膜(18,20)を形成する第3工程と、を含む、半導体素子用電極の製造方法である。

(もっと読む)

トランジスタおよび電子デバイス

【課題】チャネル層として酸化亜鉛を用いたトランジスタにおいて、チャネル層界面における電荷整合性および格子整合性を向上させる。

【解決手段】基板2上に形成したバッファ層3上に、酸化亜鉛をエピタキシャル成長させ、チャネル層4を形成する。さらに、その上に、Mg1-xCaxOをエピタキシャル成長させて界面改質層7を形成し、界面改質層7を介してゲート絶縁層8およびゲート電極9を形成する。

(もっと読む)

パターニング方法および薄膜トランジスタの製造方法

【課題】 フォトマスクの枚数を低減して製造コストの低減が可能なパターニング方法を提供する。

【解決手段】 (a)電極層20およびオーミック接続層30を順に積層形成する工程と、(b)接続層30の表面の所定位置にエッチングマスク層40を形成する工程と、(c)接続層30のa−Si材料のエッチングレートが、電極層20のMo材料およびエッチングマスク層40のレジスト材料のエッチングレートより大きくなる第1エッチングと、(d)電極層20のMo材料およびエッチングマスク層40のレジスト材料のエッチングレートが、接続層30のa−Si材料のエッチングレートより大きくなる第2エッチングとを、繰り返し実施することにより、接続層30および電極層20をパターニングするとともに、電極層20の側面を傾斜面とする工程とを有する。

(もっと読む)

表示装置と表示装置の製造方法{DISPLAYAPPARATUSANDMANUFACTURINGMETHODTHEREOF}

【課題】コーヒーステイン現象により陥没部が発生した有機半導体による薄膜トランジスタを用いても電気的特性が均一な表示装置を提供する。

【解決手段】絶縁基板1上に形成されている有機薄膜トランジスタを用いた表示装置1において、ソース電極31およびドレイン電極32により相互離隔配置されて定義されたチャンネル領域Bを、有機半導体層51の陥没部52を避けるように、有機半導体層51が形成された領域の一側に偏って位置するように形成する。

(もっと読む)

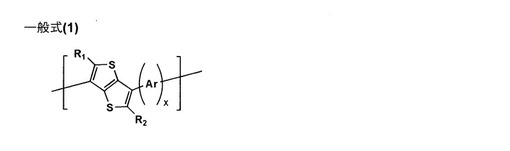

有機半導体材料、有機半導体膜、有機半導体デバイス及び有機薄膜トランジスタ

【課題】 簡単なプロセスで製造され、トランジスタとしての特性が良好であり、さらに経時劣化が抑えられた有機半導体材料、それを用いた有機半導体膜、有機半導体デバイス及び有機薄膜トランジスタを提供することである。

【解決手段】 下記一般式(1)で表される部分構造を有する化合物であることを特徴とする有機半導体材料。

【化1】

(式中、R1及びR2は互いに独立して水素原子または置換基を表す。xは0または1以上の整数を表す。Arは、置換または無置換の1つまたは2つ以上のアリーレン基またはヘテロアリーレン基を有する。)

(もっと読む)

有機半導体材料、該有機半導体材料を用いた有機半導体膜、有機半導体デバイス及び有機薄膜トランジスタ

【課題】 工程適性を有する溶媒に高濃度に溶解し、かつ十分なキャリア移動度、ON/OFF比を有し、さらには酸化に対する高い安定性を有する有機半導体材料、該有機半導体材料を用いた有機半導体膜、有機半導体デバイス及び有機薄膜トランジスタを提供することにある。

【解決手段】 下記一般式(1)で表される部分構造を有するπ共役系化合物であって、分子内にHead−to−Head構造を持たず、数平均分子量が1万以下であることを特徴とする有機半導体材料。

【化1】

(Ar1は芳香族炭化水素環または芳香族複素環を表す。X1及びX4はNR3、S、Oのいずれかを表し、X2及びX3はCR2またはNを表し、同じでも異なっていてもよい。R1〜R3は水素原子または置換基を表し、R1〜R3が同時に水素原子であることはない。)

(もっと読む)

可撓性表示装置用表示板の製造方法

【課題】

本発明は、プラスチック基板が熱によって変形することを防止して正確な薄膜パターンを形成する方法を提供する。

【解決手段】

本発明による表示板を製造する方法は、可撓性基板を形成する段階、前記基板の上にゲート線を形成する段階、前記基板の上にゲート絶縁膜を積層する段階、前記ゲート絶縁膜の上に半導体層を形成する段階、前記半導体層の上にデータ線及びドレーン電極を形成する段階、そして前記ドレーン電極と電気的に連結されている画素電極を形成する段階を含み、前記ゲート線を形成する段階、ゲート絶縁膜を積層する段階、半導体層を形成する段階、ソース電極を含むデータ線及びドレーン電極を形成する段階、そして画素電極を形成する段階のうち、少なくとも一つは温度80℃乃至150℃及び1×10-6乃至9×10-6Torrの真空度でスパッタリングする段階を含む。

(もっと読む)

素子形成基板、アクティブマトリクス基板及びその製造方法

【課題】 サイドエッチやエッチャントの染込みなどによるTFTの不良や、素子形成基板上への素子形成密度の低下や画質の劣化やクラック発生を防止することができるアクティブマトリクス基板の提供。

【解決手段】 基板31と、前記基板31上にマトリクス状に配置されたゲート線32及び信号線33からなる配線と、前記配線の交差領域に対応して配置され、薄膜トランジスタ2と前記薄膜トランジスタ2に接続されたコンタクトパッド7、8、9とを含む素子1を有し、前記素子1は、前記基板31の面内方向で分離された外辺10を備え、前記薄膜トランジスタのチャネル方向が前記基板上にマトリクス状に配置されたゲート線32及び信号線33の配線方向に対して傾きをなすように、前記薄膜トランジスタのチャネルを配置することを特徴とするアクティブマトリクス基板。

(もっと読む)

ソース−ドレイン電極、トランジスタ基板およびその製造方法、並びに表示デバイス

【課題】下部バリアメタル層の省略を可能にすると共に、工程数を増やすことなく簡略化し、Al系合金膜を薄膜トランジスタの半導体層に対し直接かつ確実に接続することができ、しかも、Al合金膜に対して低い熱プロセス温度を適用した場合でも、透明画素電極間の低電気抵抗率化を達成し得るソース−ドレイン電極を提供する。

【解決手段】薄膜トランジスタの半導体層33と、ソース−ドレイン電極34と、透明画素電極5とを有する薄膜トランジスタ基板において、ソース−ドレイン電極34は、合金成分としてNiを0.1〜6原子%含有するAl合金の薄膜からなり、Al合金の薄膜は薄膜トランジスタの半導体層33と直接接続している。

(もっと読む)

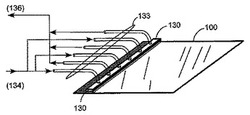

有機薄膜トランジスタおよびその製造方法

【課題】真空プロセスにおけるマスク工程を削減することによって、低分子系の有機半導体の有機薄膜トランジスタを低コストで製造すること。

【解決手段】基板101の表面にゲート電極102を有すると共に、前記ゲート電極102および基板101の表面にゲート絶縁膜103を有する積層体S1を用い、(a)所定パターン形状の開口部を有するマスク108を前記積層体S1から離間して配置する工程と、(b)前記マスク108に対して傾斜方向を含む方向に有機半導体材料を出射することにより前記積層体S1の素子形成領域に有機半導体膜104を形成する工程と、(c)前記マスク108を用い、マスク108に対して略垂直方向に電極材料を出射することにより前記積層体S1の素子形成領域にソース電極105およびドレイン電極106を形成する工程とを有する有機薄膜トランジスタの製造方法およびこれにより製造された有機薄膜トランジスタを提供する。

(もっと読む)

パターン形成体の製造方法、および有機薄膜トランジスタ

【課題】 本発明は、簡易な製造工程で高精細なパターン状に導電性パターン等を効率よく形成可能なパターン形成体の製造方法、およびその方法により形成されたパターン形成体を用いた配線基板の製造方法や有機薄膜トランジスタの製造方法等を提供することを主目的としている。

【解決手段】 上記目的を達成するために、本発明は、光触媒を含有する光触媒含有層および基体を有する光触媒含有層側基板の光触媒含有層と、撥水性を有する樹脂製基材とを対向させて配置し、パターン状にエネルギーを照射することにより、前記樹脂製基材上に水との接触角が低下した濡れ性変化パターンをパターン状に形成するエネルギー照射工程を有することを特徴とするパターン形成体の製造方法を提供する。

(もっと読む)

液晶表示装置

【課題】

配向膜の形成時に発生する有機半導体膜の劣化を防止し、高性能な有機薄膜トランジスタを用いた液晶表示装置を安価に提供すること。

【解決手段】

ゲート電極,ゲート絶縁膜,ソース・ドレイン電極,半導体層から構成される薄膜トランジスタ及び、配線,画素電極の各部材を有する薄膜トランジスタ基板と、この基板との間で液晶層を挟持する対向基板を有する液晶表示装置において、半導体層と液晶層との間に液晶層の分子配向を制御する機能を有する配向膜を介在させない。

(もっと読む)

薄膜トランジスタ

【課題】 トップゲート構造を有し、酸化亜鉛ZnOを主成分とする酸化物半導体薄膜を用いる薄膜トランジスタにおいて、プラズマ化学気相成長(PCVD)法にて成膜可能な窒化珪素膜をゲート絶縁膜に用いつつ、該ゲート絶縁膜を二層構造として、各の絶縁膜の窒素濃度及び水素濃度を調整することによって、酸化亜鉛(ZnO)半導体薄膜を還元から保護し、リーク電流の発生が抑止された、電流駆動能力の高い薄膜トランジスタの提供。

【解決手段】 酸化亜鉛ZnOを主成分とする酸化物からなる半導体薄膜層と、窒化珪素(SiNx)からなるゲート絶縁膜を有するトップゲート型薄膜トランジスタであって、前記ゲート絶縁膜は前記半導体薄膜層の少なくとも上表面を被覆する第一ゲート絶縁膜と、該第一ゲート絶縁膜及び半導体薄膜の側面を少なくとも被覆する第二ゲート絶縁膜とからなり、前記第一ゲート絶縁膜と前記第二ゲート絶縁膜は、組成が異なる窒化珪素(SiNx)からなることを特徴とする薄膜トランジスタ。

(もっと読む)

薄膜トランジスタの製法

【課題】 薄膜トランジスタの構成半導体薄膜(活性層)である酸化亜鉛(ZnO)を主成分とする酸化物半導体薄膜と、該酸化物半導体薄膜に接するゲート絶縁膜とを真空中で連続成膜することによって、これら二層の間に清浄な界面を形成し、良好なTFT特性を示す高性能な薄膜トランジスタを提供することができるとともに、量産化が容易である薄膜トランジスタの製法の提供。

【解決手段】 酸化亜鉛(ZnO)を主成分とする酸化物からなる半導体薄膜と、シリコン系絶縁膜からなり該半導体薄膜に接するゲート絶縁膜を有する薄膜トランジスタの製法において、前記半導体薄膜の形成と前記ゲート絶縁膜の形成が、真空中にて連続した工程で行われることを特徴とする薄膜トランジスタの製法。

(もっと読む)

薄膜トランジスタの製法

【課題】 トップゲート構造を有し、酸化亜鉛ZnOを主成分とする酸化物半導体薄膜を用いる薄膜トランジスタのゲート絶縁膜作製工程において、酸化亜鉛ZnOを主成分とする酸化物半導体薄膜表面に、酸化性ガスによるプラズマ処理を施すことにより、半導体薄膜表面を酸素終端しつつ清浄化しゲート絶縁膜を形成することで、ゲート絶縁膜と半導体薄膜間で良好な界面を形成し、ソース・ドレイン間の短絡やリーク電流の発生を低減した高性能薄膜トランジスタの製法の提供。

【解決手段】 酸化亜鉛ZnOを主成分とする酸化物を半導体薄膜として用いるトップゲート型薄膜トランジスタの製法であって、前記半導体薄膜にパターン加工を施した後、該半導体薄膜の表面全面を被覆するゲート絶縁膜をシリコン系絶縁膜により形成する加工前において、前記半導体薄膜表面全面に酸化性ガスを用いたプラズマ雰囲気にて表面処理を行い、前記表面処理に引き続き、真空中にて連続して前記ゲート絶縁膜を形成することを特徴とする薄膜トランジスタの製法。

(もっと読む)

薄膜トランジスタ

【課題】 酸化亜鉛ZnOを主成分とする酸化物を半導体薄膜層として用いるトップゲート構造のTFTにおいて、半導体薄膜層の少なくとも表面に酸素を構成元素に含む化合物あるいは酸素をドーピングされた化合物による被覆を行うことにより、ZnO成分の還元あるいは脱離を抑制し、半導体薄膜層の低抵抗化によるソース・ドレイン間の短絡やリーク電流の発生を抑制し得る薄膜トランジスタの提供。

【解決手段】 酸化亜鉛ZnOを主成分とする酸化物を半導体薄膜層として用いるトップゲート型薄膜トランジスタにおいて、前記半導体薄膜層全表面を被覆するゲート絶縁膜が形成されている構造を有し、前記ゲート絶縁膜の少なくとも前記半導体薄膜層の表面に接する領域は、酸素を構成元素に含む絶縁膜あるいは酸素をドーピングされた絶縁膜により形成されていることを特徴とする薄膜トランジスタ。

(もっと読む)

薄膜トランジスタ

【課題】 薄膜トランジスタの構成半導体(活性層)である酸化亜鉛を主成分とする酸化物半導体薄膜の表面層を保護する構造を有し、ドレイン・ソース間の低抵抗化などによる特性劣化を防止し得る高性能の薄膜トランジスタの提供。

【解決手段】 絶縁基板上にソース・ドレイン電極が間隔を有して形成され、前記ソース・ドレイン電極の間にチャネルとして形成される酸化亜鉛ZnOを主成分とする酸化物半導体薄膜層と、該酸化物半導体薄膜層の上表面及び側面を被覆してシリコン系絶縁膜にて形成されるゲート絶縁膜を有し、前記ゲート絶縁膜は、前記酸化物半導体薄膜層の上表面を被覆する第一ゲート絶縁膜と、前記第一ゲート絶縁膜の全面及び酸化物半導体薄膜の少なくとも側面を被覆する第二ゲート絶縁膜からなることを特徴とする薄膜トランジスタ。

(もっと読む)

2,001 - 2,020 / 2,248

[ Back to top ]