Fターム[5F110HK42]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 低抵抗層形成後の処理 (709)

Fターム[5F110HK42]に分類される特許

201 - 220 / 709

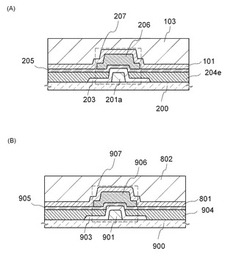

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】通信距離が極端に短い場合においても正常に動作し、且つ通信距離が長い場合においては、保護回路での消費電力を抑え、信頼性の高い半導体装置(RFID)を提供する。

【解決手段】無線によりデータの交信が可能な半導体装置(RFID)を構成する素子を保護するための保護回路107を設けることに特徴を有する。そして、整流回路102において生成された直流電源電位が所定の値(基準値)以上となるときに保護回路107が動作するようにし、生成される直流電源電位の値を小さくする。一方、整流回路102において生成された直流電源電位が所定の値(基準値)以下となるときは、保護回路107が動作しないようにし、生成された直流電源電位の値をそのまま用いる。また、保護回路107のトランジスタ201,202は、酸化物半導体層により構成されており、トランジスタ201,202のオフ電流を下げ、保護回路107での消費電力を抑える。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタの電気的特性のばらつき及び電気的特性の劣化は、半導体装置の信頼性を著しく低下させる。

【解決手段】基板上に形成される酸化物半導体層と、酸化物半導体層と電気的に接続する、端部がテーパー角を有し、かつ上端部が曲面形状を有するソース電極及びドレイン電極と、酸化物半導体層の一部と接し、かつ酸化物半導体層、ソース電極及びドレイン電極を覆うゲート絶縁層と、酸化物半導体層と重畳する、ゲート絶縁層上のゲート電極と、を有する。

(もっと読む)

電子デバイス、電子デバイス製造方法、電子デバイス製造装置、電界効果トランジスタデバイス、有機電界発光素子及び制御方法

【課題】低仕事関数金属の使用や不純物ドーピングなしで伝導特性を制御し得る電子デバイスを提供することを目的とする。

【解決手段】本発明による電子デバイスは、電極層と半導体層とが吸着した吸着部を有する電子デバイスであって、前記吸着部において、前記電極層の原子表面と前記半導体層の原子表面との距離は、前記電極層の前記原子表面と前記半導体層の前記原子表面とが安定して吸着する安定吸着距離より短い。前記吸着部への加重によって、前記距離を前記安定吸着距離より短くする加重部を有する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

ジュール効果の熱活性化による選択的官能基化

【課題】導電性または半導体材料(M)の表面にレセプター分子(R)を共有グラフトさせることによって、導電性または半導体材料(M)を官能基化する方法を提供する。

【解決手段】次のステップにより官能化する。(i)材料(M)の両側に配置したソース電極およびドレイン電極の端子間に、分子(R)のグラフト反応に対して材料(M)を熱活性化するのに十分な電位差を印加するステップ;ならびに(ii)こうして活性化された材料(M)を、レセプター分子(R)を含有する液体またはガス状の媒体に接するように置き、それによって、共有グラフトされたレセプター分子(R)で官能基化された材料(M)を得るステップを含む方法に関する。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性を向上させる。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、第13族元素および酸素を含む材料を用いて酸化物半導体膜と接する絶縁膜を形成することにより、酸化物半導体膜との界面の状態を良好に保つ。さらに該絶縁膜が、化学量論的組成比より酸素が多い領域を含むことにより、酸化物半導体膜に酸素を供給し、酸化物半導体膜中の酸素欠陥を低減する。また、酸化物半導体膜と接する絶縁膜を積層構造として、酸化物半導体膜の上下に、アルミニウムを含む膜を設けることで、酸化物半導体膜への水の侵入を防止する。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を形成した後、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に微結晶半導体膜を積層形成する。第1の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上1333Pa以下とする条件である。第2の条件は、シリコンまたはゲルマニウムを含む堆積性気体と、水素との流量比を周期的に増減させながら処理室に供給し、且つ処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

有機トランジスタ素子用テンプレートおよびその製造方法、並びに有機トランジスタ素子およびその製造方法

【課題】厚みが制御された有機半導体層を形成することが可能であり、トランジスタ特性に優れた有機トランジスタ素子を製造することができる有機トランジスタ素子用テンプレートを提供することを主目的とする。

【解決手段】基板と、上記基板上に形成され、親液化処理によって親液化される親液‐疎液可変性材料からなる下地層と、上記下地層上に形成されたソース電極およびドレイン電極と、上記ソース電極およびドレイン電極の有機半導体層形成領域内の表面上に形成され、親液性材料からなる親液膜と、上記ソース電極およびドレイン電極の有機半導体層形成領域外の表面上に形成され、疎液性材料からなる疎液膜とを有し、上記下地層の表面が上記ソース電極およびドレイン電極間のチャネル領域内において親液性を示しかつ上記チャネル領域外において上記チャネル領域内よりも疎液性を示すことを特徴とする有機トランジスタ素子用テンプレートを提供する。

(もっと読む)

耐透明導電膜ピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記透明導電膜の結晶最大粒径が200nm以下である薄膜トランジスタ基板。

(もっと読む)

固体撮像装置、半導体表示装置

【課題】撮像された画像の品質を向上させる固体撮像装置、或いは半導体表示装置を提供する。

【解決手段】グローバルシャッタ方式で駆動を行うことで、電荷の蓄積動作を制御するための電位を全画素で共有することができる。さらに、出力信号が与えられる一の配線に接続されている複数のフォトセンサを第1のフォトセンサ群とし、出力信号が与えられる他の配線に接続されている複数のフォトセンサを第2のフォトセンサ群とすると、電荷の蓄積動作を制御するための電位または信号を第1のフォトセンサ群に与える配線と、上記電位または信号を第2のフォトセンサ群に与える配線とを、接続する。

(もっと読む)

半導体膜の作製方法、半導体装置の作製方法、及び光電変換装置の作製方法

【課題】抵抗率の低い不純物元素を有する非晶質半導体を形成する。また、電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】プラズマCVD法により不純物元素を有する非晶質半導体を形成する方法において、パッシェンの法則で最小放電開始電圧を満たす圧力及び電極間隔において、パルス変調した放電開始電圧を電極に印加することより、抵抗率の低い不純物元素を有する非晶質半導体を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】n型及びp型の少なくともいずれかの不純物が添加された不純物領域を有する半導体膜と、配線とを有し、配線は、導電性を有する金属酸化物を含む拡散防止膜と、該拡散防止膜上の低抵抗導電膜とを有し、配線と半導体膜とのコンタクト部において、拡散防止膜と不純物領域とが接する。拡散防止膜は、導電膜を酸化性ガス及びハロゲン系ガスの混合ガスから生成されるプラズマに暴露して該導電膜に含まれる金属材料の酸化物を形成し、金属材料の酸化物が形成された導電膜を、水を含む雰囲気に暴露して導電膜を流動化させ、流動化した導電膜を固化することで形成する。

(もっと読む)

液晶表示装置の駆動方法

【課題】画質の低下を防ぎつつ、消費電力の低減を実現することができる、液晶表示装置の駆動方法を提案する。

【解決手段】液晶素子と、当該液晶素子への画像信号の供給を制御するトランジスタとを画素に有する。上記トランジスタは、チャネル形成領域に、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を含み、オフ電流の極めて小さい。そして、画素を反転駆動させる際に、画素電極を間に挟んで配置されている一対の信号線に、互いに逆の極性を有する画像信号を入力する。上記構成により、液晶素子に容量素子を接続しなくても、表示される画質が低下するのを防ぐ。

(もっと読む)

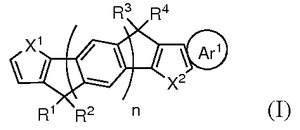

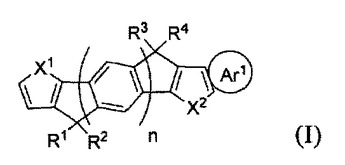

有機半導体

構造:

【化1】

(式中、R1〜R4は独立に、それだけに限らないが、2〜20個(例えば2〜12個)の炭素原子を有する、場合により置換された直鎖、分岐、もしくは環状のアルキル鎖、アルコキシ、アミノ、アミド、シリル、アルキル、アルケニル、アリール、またはヘテロアリールを含み、X1およびX2は独立に、S、O、NR5またはSiR6R7を含み、R5〜R7は独立に、C1〜C5の分岐、直鎖、または環状のアルキル鎖を含み、Ar1は、複素環を含み、nは、1〜4の間の整数である)

を含む半導体化合物。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを有する半導体装置において、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】酸化物半導体を用いたトランジスタにおいて、トップゲート構造の場合は下地絶縁層に、ボトムゲート構造の場合は保護絶縁層に、酸素が過剰な酸化シリコン(SiOX(X>2))を用いる。酸素が過剰な酸化シリコンを用いることにより、絶縁層から酸素が放出され、酸化物半導体層中の酸素欠損及び下地絶縁層もしくは保護絶縁層と酸化物半導体層の界面準位密度を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

DCDCコンバータ、電源回路及び半導体装置

【課題】電力変換効率の向上を実現するDCDCコンバータの提供を目的の一とする。

【解決手段】出力電力を制御するためのスイッチング素子として機能するトランジスタが、通常のゲート電極に加えて、閾値電圧を制御するためのバックゲート電極を備える。そして、DCDCコンバータから出力される出力電力の大きさに従って、バックゲート電極に与える電位の高さを制御するための、バックゲート制御回路を備える。バックゲート制御回路により、バックゲート電極に与える電位を制御することで、出力電力が大きい場合にはオン抵抗が下がるように閾値電圧を調整し、出力電力が小さい場合にはオフ電流が下がるように閾値電圧を調整することができる。さらに、スイッチング素子として機能するトランジスタが、オフ電流の極めて小さい絶縁ゲート電界効果型トランジスタである。

(もっと読む)

アクティブマトリックス基板、及び液晶装置

【課題】低コストに製造することができ、TFTのオフリーク電流を低減することが可能なアクティブマトリックス基板を提供する。

【解決手段】アクティブマトリックス基板201は、基板1上に形成されたゲート電極2及びゲート絶縁膜3と、結晶性半導体膜41及び/又は非晶質半導体膜42からなるチャネル層と、ソース電極5s及びドレイン電極5dとを備えたTFT104と、画素電極9とが複数対アレイ状に配置されたものである。チャネル層はゲート電極2の形成領域内に形成され、ソース電極5s及びドレイン電極5dはチャネル層の形成領域内に形成されており、ゲート絶縁膜3上のゲート電極2より離間した位置にソース配線5aが形成され、ソース配線5aが、ソース電極5sの直上に形成され、さらにソース電極5s上から延設された酸化物導電膜からなる接続配線6aを介してソース電極5sに接続されている。

(もっと読む)

成膜方法及び薄膜トランジスタの作製方法

【課題】3層以上の膜を成膜するに際して、第1の膜の成分が第3の膜に含まれることを防ぐ成膜方法を提供する。

【解決手段】上部電極104と下部電極102が設けられた成膜装置100により3層以上の膜を成膜する多層膜の成膜に際して、下部電極102上に基板110を配して第1の膜112を成膜し、前記第1の膜112の形成時よりも上部電極104と前記基板110の間の距離を長くし、前記第1の膜112上に第2の膜114を成膜し、前記第2の膜114の形成時よりも前記上部電極104と前記基板110の間の前記距離を短くし、前記第2の膜114上に第3の膜116を成膜する。

(もっと読む)

パルス変換回路

【課題】回路面積を低減する。

【解決手段】第1の信号が入力され、第2の信号を出力する論理回路を具備し、論理回路は、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧より高い第2の電圧に設定するか否かを制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キャリア濃度が1×1014/cm3未満である酸化物半導体層を含む。

(もっと読む)

201 - 220 / 709

[ Back to top ]