Fターム[5F110PP03]の内容

Fターム[5F110PP03]の下位に属するFターム

Fターム[5F110PP03]に分類される特許

2,001 - 2,020 / 2,255

表示装置、アレイ基板、及び表示装置の製造方法

【課題】カレントコピー型回路を画素に採用した表示装置で表示ムラが発生するのを防止すること。

【解決手段】本発明の表示装置は、各画素PXが、ソースが電源端子ND1に接続された薄膜トランジスタDR1と、これとは導電型が異なり、ソースがトランジスタDR1のドレインに接続され、ドレインが端子ND1に接続された薄膜トランジスタDR2と、定電位端子ND1’とトランジスタDR1のゲートとの間に接続されたキャパシタC1と、トランジスタDR2のソースとゲートとの間に接続されたキャパシタC2と、スイッチSWc1及びSW2を含み、トランジスタDR1のゲートとドレインと映像信号線DLとの接続を、それらが互いに接続された状態と、各接続が断たれた状態との間で切り替え可能なスイッチ群と、トランジスタDR2のゲートとドレインとの間に接続されたスイッチSWc2と、スイッチSWaと、電源端子ND2とトランジスタDR1のドレインとの間でスイッチSWaと直列に接続された表示素子OLEDとを備えたことを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構成を有する薄膜トランジスタを提供する。またコンタクトホールの形成を、容易かつ確実に実施する方法を提供する。

【解決手段】断面がテーパー形状であるアルミニウムゲイト電極と、前記ゲイト電極上のゲイト絶縁膜と、前記ゲイト絶縁膜上のチャネル形成領域を構成するI型のアモルファスシリコン膜と、前記I型のアモルファスシリコン膜上の保護膜と、前記I型のアモルファスシリコン膜及び保護膜上のn型のアモルファスシリコン膜からなるソース領域及びドレイン領域と、前記ソース領域に電気的に接続されたアルミニウムソース電極と、前記ドレイン領域に電気的に接続されたアルミニウムドレイン電極と、前記ゲイト絶縁膜上の画素電極と、前記ゲイト電極に電気的に接続されたアルミニウムゲイト配線と、を有し、前記ドレイン領域と前記画素電極とはアルミニウムを介して電気的に接続されていることを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】本発明では、基板上に設けられた薄膜トランジスタ等を有する素子形成層を当該基板から剥離することにより半導体装置を作製する方法であって、低コストで信頼性の高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に金属膜を形成し、金属膜にプラズマ処理を行うことによって金属膜の表面に金属酸化膜を形成し、金属酸化膜上に素子形成層を形成し、素子形成層を覆って絶縁膜を形成し、絶縁膜および素子形成層に開口部を形成し、開口部にエッチング剤を導入して金属膜および金属酸化膜を除去し、基板から素子形成層を剥離することを特徴としている。剥離は金属膜および金属酸化膜の一部を除去し、その後物理的手段を用いることによって剥離することも可能である。

(もっと読む)

荷電ビームを用いた液滴吐出装置及び該装置を用いてのパターンの作製方法

液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。本発明は、主に絶縁表面を有する基板上において、液滴吐出法によってレジスト材料或いは配線材料等を直接パターニングを行うに際し、液滴着弾精度を飛躍的に向上させることが可能になる。具体的には、液滴吐出法による液適の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させることを特徴とする。  (もっと読む)

(もっと読む)

レーザアニール方法およびレーザアニール装置

【課題】従来技術の問題点を解決したレーザ加工方法及びレーザ加工装置に製造方法を提供する。

【解決手段】レーザを用いたレーザアニール方法およびレーザアニール装置において、光路中にホモジナイザ5、光変調素子6、受光素子7を配し、受光素子7により、光変調素子6にて発生した回折光を遮光することにより、装置に対するダメージを低減することが出来る。また受光素子7が光強度測定機能、もしくは光電変換機能を具備することにより、光軸3が正常な範囲の光強度を有するかどうかを判断することが出来、また受光した光エネルギーを、再度装置で使用することも可能となる。

(もっと読む)

半導体装置、液晶表示装置、エレクトロルミネッセンス表示装置

【課題】ガラス基板上に低コストで信頼性が高い半導体装置を提供する。

【解決手段】ガラス基板上に形成された下地膜と、下地膜上に形成されたNチャネル型薄膜トランジスタ及びPチャネル型薄膜トランジスタを有し、Nチャネル型薄膜トランジスタはドレイン領域及びチャネル形成領域の間にLDD領域が設けられた第1の結晶性珪素膜を有し、Pチャネル型薄膜トランジスタはチャネル形成領域に接してドレイン領域が設けられた第2の結晶性珪素膜を有し、ガラス基板、下地膜、第1の結晶性珪素膜及び第2の結晶性珪素膜はゲイト絶縁膜に覆われている。

(もっと読む)

半導体装置の作製方法

【課題】好適な形状の配線を有する半導体装置を提供することを課題とする。

【解決手段】素子と接続される第1の導電層と、その上の第2の導電層とを形成し、第2の導電層上にレジストのマスクを形成し、マスクを用いたドライエッチングによって第2の導電層を加工し、マスクを残したままウエットエッチングによって第1の導電層を加工する配線の作製方法であって、ドライエッチングにおいて、第2の導電層のエッチングレートは第1の導電層のエッチングレートより大きく、ウエットエッチングにおいて、第2の導電層のエッチングレートは第1の導電層のエッチングレート以上とする。

(もっと読む)

液晶表示装置及びその駆動方法

本発明は、アクティブマトリクス型の液晶表示装置及びその駆動方法に関し、表示を滑らかに改善するための画素間での画像平均化処理において、フレームメモリを省略できる液晶表示装置及びその駆動方法を提供する。例えば画素P11内に構成される複数のサブ画素S11a、S11b、S11c、S11dのうちサブ画素S11dと、それに隣接する画素P12、P21、P22内の隣接サブ画素S12c、S21b、S22a、との蓄積電荷の平均化を行う蓄積電荷平均化用TFT回路を設けることで、フレームメモリなしに表示画像の平滑化処理を実現する。  (もっと読む)

(もっと読む)

アクティブマトリクス型表示装置及びその製造方法

【課題】製造工程の増加や信頼性の低下を招くことなく、TFT基板と対向基板の接続強度を高め、額縁の幅を狭くすることができるアクティブマトリクス型表示装置及びその製造方法の提供。

【解決手段】少なくとも、薄膜トランジスタのゲート電極を覆う無機系材料からなる第1層間絶縁膜6と、第1層間絶縁膜上の配線及びドライバと接続するための接続配線8aを覆う第2層間絶縁膜9と、アクリル、エポキシ系などの有機系材料からなる平坦化膜10と、スルーホールを介して上記配線に接続される画素電極とを少なくとも備えるTFT基板において、上記スルーホールの形成と同時に、シール領域の接続配線8aを除く領域の一部の平坦化膜10及び第2層間絶縁膜9を除去して凹部14を形成して、該凹部14の底部において無機系材料からなる第1層間絶縁膜9とシール材30とを接触させて接続強度を向上させる。

(もっと読む)

半導体装置、表示装置、及びそれらの作製方法、並びにテレビジョン装置

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な半導体装置、表示装置及びその作製技術を提供することを目的とする。また、それらの半導体装置、表示装置を構成する配線等のパターンを、所望の形状で密着性よく形成できる技術を提供することも目的とする。

【解決手段】第1の導電層と第2の導電層の間に、導電性の有孔バッファ層を形成することによって、第1の導電層と第2の導電層との密着性を高める。有孔バッファ層が有する孔に、粒子状の導電性材料を侵入させ、焼成によって固化し、第2の導電層を形成する。孔内で固化した導電層がくさびのような働きをし、この働く力によって、第2の導電層は、第1の導電層と密着性よく安定して形成される。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程でNiシリサイドを形成する。

【解決手段】基板上に半導体膜を形成し、前記基板を加熱しながら前記半導体膜上にNi膜を成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。また基板上に半導体膜を形成し、前記基板を450℃以上に加熱しながら前記半導体膜上にNi膜を成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。また基板上に半導体膜を形成し、前記基板を450℃以上に加熱しながら前記半導体膜上にNi膜を10nm以上成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。

(もっと読む)

薄膜トランジスタ表示板

【課題】均一な画質を有する薄膜トランジスタ表示板を提供する。

【解決手段】薄膜トランジスタ表示板は、基板と、基板上に形成され、ソース領域、ドレイン領域、及びチャンネル領域を有し、多結晶シリコンからなる複数の半導体と、半導体上に形成されているゲート絶縁膜と、ゲート絶縁膜上に形成され、チャンネル領域と重畳するゲート線と、ゲート絶縁膜上に形成され、ソース領域と接続されているデータ線と、ゲート絶縁膜上に形成され、ドレイン領域と接続されている画素電極とを備え、半導体の表面は複数の突起(P)を有し、半導体の長さ(X)が突起(S)間の距離の整数倍である。

(もっと読む)

電気光学装置、電子機器

【課題】 同一基板上に高速動作可能な周辺駆動回路と高耐圧な画素回路の双方を備えた電気光学装置を提供する。

【解決手段】 本発明の電気光学装置は、同一基板10上に画素回路と周辺駆動回路とを備えた電気光学装置であって、前記画素回路と前記周辺駆動回路はそれぞれ多結晶半導体層30s,32sを備えたトランジスタ30,32を含み、前記画素回路のトランジスタ30はトップゲート型の構造を有し、前記周辺駆動回路用のトランジスタ32はボトムゲート型の構造を有することを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の有機メモリおよび当該有機メモリを有する半導体装置を提供することを目的とする。また、信頼性が高く、安価な半導体装置の提供を課題とする。

【解決手段】第1の方向に延びた複数のビット線と、第1の方向と垂直な第2の方向に延びた複数のワード線と、記憶素子部を備えたメモリセルと、複数のメモリセルからなるメモリセルアレイとを有し、記憶素子部は、ビット線を構成する導電層とワード線を構成する導電層との間に設けられた有機化合物層を有し、当該有機化合物層に、無機化合物と有機化合物とを混合して設けられた層を設けることを特徴としている。

(もっと読む)

レーザ処理装置、レーザ処理方法及び半導体装置の作製方法

【課題】レーザ照射の途中で移動テーブルが異常停止した際に、自動的にレーザの出力を停止させ、火災などの災害を防ぐことを課題とする。

【解決手段】レーザ発振器と、レーザ発振器に設けられたインターロックと、一定の動作周期で移動する移動テーブルと、タイマと、タイマに設けられたインターロックと、移動テーブルの移動を検出できるセンサと、コンピュータとを有し、タイマはセンサが移動テーブルの通過を感知することでカウントをスタートさせ、移動テーブルが動作周期を経過してもセンサを通過しない場合、タイマに設けられたインターロックの接点間の通電が切れることで、レーザ発振器のインターロックを作動させレーザ光の射出を停止させるレーザ処理装置及びそれを用いて行うレーザ処理方法に関する。

(もっと読む)

エッジ領域を最小にするために基板のフィルム領域のレーザ結晶化処理方法及び装置並びにそのようなフィルム領域の構造

薄膜サンプル(170)を処理する方法及び装置を提供する。特に、ビーム発生器(110)を、少なくとも一つのビームパルス(111)を放出するように制御することができる。ビームパルス(111)は、少なくとも一つのマスクビームを生成するようにマスクされ、マスクビームは、薄膜サンプル(170)の少なくとも一部分を照射するのに用いられる。少なくとも一つのマスクビームパルス(164)によって、薄膜サンプル(170)の一部(510)は、そのような部分を後に結晶化するのに十分な強度で照射される。薄膜サンプル(170)のこの部分(510)を、第1領域(518)及び第2領域(515)から構成されるように結晶化することができる。その結晶化に応じて、第1領域(518)は、第1セットの粒子を含み、第2領域(515)は、少なくとも一つの特性が第1セットの粒子の少なくとも一つの特性と異なる第2セットの粒子を含む。第1領域(518)は、第2領域を包囲し、薄膜トランジスタ(TFT)(610)の活性領域を所定の距離で設けることができるように構成される。  (もっと読む)

(もっと読む)

半導体装置及びその作製方法

【課題】新たな方法により基板から薄膜トランジスタ、及び該薄膜トランジスタを有する回路や半導体装置を分離し、可撓性を有する基板へ転置する方法を提供することを課題とする。

【解決手段】絶縁膜に広い、又は複数の開口部を形成し、該開口部に薄膜トランジスタに接続された導電膜を形成し、その後、剥離層を用いて、薄膜トランジスタを有する層を、導電膜等が形成された基板へ転置することを特徴とする。さらに加えて本発明の薄膜トランジスタは、レーザ照射により結晶化された半導体膜を有し、レーザ照射時において、剥離層が露出することを防止し、直接剥離層にレーザ照射されないことを特徴とする。

(もっと読む)

半導体装置およびその作製方法

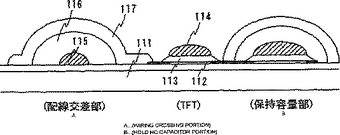

島状の層間絶縁膜をソース線とゲート線が交差する領域に選択的に形成する。例えば、インクジェット法を用いて絶縁材料を含む液体をゲート線とソース線が交差する領域若しくは保持容量が形成される領域に滴下することにより、フォトリソグラフィー工程を削減し、TFT作製プロセス中において使用するマスク枚数を減らすことが可能となる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能の均一性を向上させることが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、ガラス基板1上に非晶質シリコン膜4を形成する工程と、非晶質シリコン膜4上に吸収膜6を形成する工程と、吸収膜6の所定領域上に反射抑制膜7を形成する工程と、反射抑制膜7および吸収膜6にレーザーを照射することにより吸収膜6を発熱させ、その熱を利用して非晶質シリコン膜4を結晶化することによって、複数の柱状結晶が会合することにより形成される連続した結晶粒界帯8の位置が制御された結晶シリコン膜4aを形成する工程とを備えている。

(もっと読む)

半導体装置、半導体記憶装置および半導体装置の製造方法

【課題】 ゲートからソースへの漏洩電流を伴うことなく、しきい値電圧を可変させるとともに、素子面積の増大を抑制する。

【解決手段】 半導体基板101上には絶縁層102が形成され、絶縁層102上には半導体層103が形成され、さらに、半導体層103上には絶縁層104が形成され、絶縁層104上には半導体層105が形成され、半導体層105上には、ゲート絶縁膜106を介してゲート電極107が形成され、ゲート電極107の側方には、ソース層109およびドレイン層110が形成され、ゲート電極107は、配線層を介して半導体層103に接続されている。

(もっと読む)

2,001 - 2,020 / 2,255

[ Back to top ]