Fターム[5F140AA40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 工程の簡略化 (489)

Fターム[5F140AA40]に分類される特許

481 - 489 / 489

埋設導電層を備えた高電圧トランジスタ

【課題】埋設導通層を備えた低オン抵抗値の横方向高電圧電界効果トランジスタ(HVFET)を提供する。

【解決手段】P型基板に形成されたN型ウエル内にP型埋設層領域を設け、これをN型ウエル領域に形成された第1のP型ドレイン拡散領域によってドレイン電極に接続すると共に、PMOSゲート領域の一端で表面から下方に延びる第2のP型ドレイン拡散領域にも接続し、ソース電極に接続されるP型ソース拡散領域でゲート領域の他端を定める。

(もっと読む)

歪み半導体層の製造方法、半導体装置の製造方法、およびそのような方法で使用するのに適した半導体基板

本発明は、半導体歪み層の製造方法と、シリコンの半導体本体(11)に、その表面において、シリコンおよびゲルマニウムの混晶の格子と、格子が実質的に緩和されるような厚さとを有する第1の半導体層(1)が設けられ、かつ第1の半導体層(1)の上に、歪みシリコンを含む第2の半導体層(2)が設けられ、その層(2)内に半導体装置(10)の一部が形成され、半導体装置(10)を形成するのに必要な後続の処理中に、歪みシリコン層(2)の有効厚さの低減を回避するための手段が取られ、前記手段が、シリコンおよびゲルマニウムの混晶の格子を有する第3の層(3)を使用することを含む、半導体装置(10)の製造方法とに関する。本発明によれば、第3の層(3)は、薄く、かつ第1の半導体層(1)および第2の半導体層(2)の境界面に近接して第2の層(2)内に位置付けられる。このようにして、歪みシリコン層(2)の結果として得られる厚さは、後続のMOSFETの形成の後に増加されることができ、その結果、より良好な高周波特性を備えたMOSFETが得られる。本発明は、また、本発明による方法で得られる装置、およびそのような方法で使用するのに適した半導体基板構造を含む。  (もっと読む)

(もっと読む)

トンネル層に量子ドットを有するトランジスタ

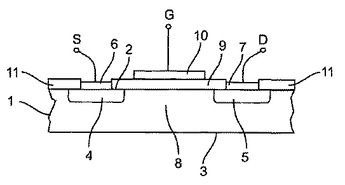

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

半導体構造、二重仕事関数のCMOSデバイス、二重仕事関数のCMOS回路、および基板上に二重仕事関数のCMOSデバイスを形成する方法(炭化金属ゲート構造および形成方法)

【課題】 炭化金属を含むゲート電極を含む少なくとも1つのFETを含む相補型金属酸化膜半導体(CMOS)などの半導体デバイスおよび形成方法を提供することにある。

【解決手段】 このCMOSは、ある金属とある金属の炭化物によって二重仕事関数が与えられる、二重仕事関数の金属ゲート電極を含む。

(もっと読む)

シリサイド成長ドーパント雪かき効果の使用による、デバイス中に階段接合の形成

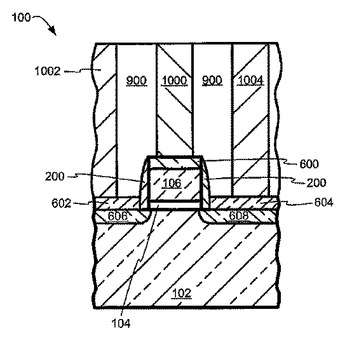

トランジスタ(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に絶縁層(702)をたい積する。その後、絶縁層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

CMOSデバイスのための歪みSiを形成する方法及び構造体

【課題】 チャネルのNFET及びPFETにおいて、それぞれ大きい引張応力及び圧縮応力を生成するように、費用対効果が大きく、簡単化された方法を提供すること。

【解決手段】 n型デバイス及びp型デバイスを含むデバイスの製造方法である。本発明の一態様において、方法は、半導体基板の部分をドープするステップと、半導体基板のドープされた部分の少なくとも一部を除去することによって、該半導体基板内にギャップを形成するステップとを含む。この方法はさらに、半導体基板内のギャップの少なくとも一部に歪み層を成長させるステップをさらに含む。n型デバイスの場合には、歪み層は、少なくともn型デバイスのチャネルのほぼ真下にある部分の上に成長される。p型デバイスの場合には、歪み層は、少なくともp型デバイスのソース領域又はドレイン領域のほぼ真下にあり、p型デバイスのチャネルのほぼ下にはない部分の上に成長される。

(もっと読む)

大量にドープされたエピタキシャルSiGeを選択的に堆積させる方法

一実施形態においては、基板上にシリコン膜又はシリコンゲルマニウム膜を堆積させる方法であって、プロセスチャンバ内に基板を配置するステップと、基板表面を約600℃〜900℃の範囲の温度に、プロセスチャンバ内の圧力を約13Pa(0.1トール)〜約27kPa(200トール)の範囲に維持しつつ、加熱するステップと、を含む前記が提供される。堆積ガスは、プロセスチャンバに供給され、SiH4、任意のゲルマニウム源ガス、エッチング剤、キャリヤガス、任意に少なくとも1つのドーパントガスを含んでいる。シリコン膜又はシリコンゲルマニウム膜は、基板上に選択的且つエピタキシャル的に成長する。一実施形態は、シリコン含有膜とキャリヤガスとして不活性ガスを堆積させる方法を含んでいる。方法は、また、選択的シリコンゲルマニウムエピタキシャル膜を用いる電子デバイスの製造を含んでいる。 (もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

非対称の側壁スペーサの形成方法

集積回路半導体デバイスの製造プロセスに統合可能な非対称スペーサの形成方法が提供される。この方法は、基板上にゲート構造(15)を形成するステップと、ゲート構造および基板の上に側壁層(10)を形成するステップとを含み、側壁層は、ゲート構造の第1の側壁の上に第1の部分を含む。第1の部分に隣接して、フォトレジスト構造(11)が形成され、イオンビームにさらされる。フォトレジスト構造は、第1の部分の少なくとも一部をイオンビームから遮蔽するように働く。照射中、ウェハは、イオンビーム(13、17)の経路と、第1の側壁の表面との間に、非直交傾斜角が存在するように配向される。遮蔽されていない側壁部分への放射ダメージにより、その後に続くエッチングがより高速に進むため、非対称スペーサの形成が可能である。  (もっと読む)

(もっと読む)

481 - 489 / 489

[ Back to top ]