Fターム[5F140AC19]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | BOMOS(埋込み酸化膜MOS) (24)

Fターム[5F140AC19]に分類される特許

1 - 20 / 24

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置

【課題】 スナップバック現象が発生する時のドレイン電流値を大きくすることによって、ESD耐量を改善する。

【解決手段】 半導体装置10は、ソース領域23とボディ領域21の間の少なくとも一部に絶縁領域22を備えている。絶縁領域22は、ソース領域23とボディ領域21とドリフト領域25で構成される寄生のnpnトランジスタのベース・エミッタ間の接合面積を小さくするので、寄生のnpnトランジスタがオンした後にソース領域23から注入される電子量を低減する。これにより、スナップバック現象が発生する時のドレイン電流値を大きくすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生トランジスタによる異常リークの発生を抑制し、正常な電気特性を得ることが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、ボロンイオンが導入されたシリコン基板にLOCOS酸化膜2を形成し、この酸化膜2の内側に位置するアクティブ領域1aにおけるチャネル形成領域を含む端部にボロンイオンを注入することにより、アクティブ領域1aにおける前記端部にP型不純物拡散層3を形成し、シリコン基板のアクティブ領域1a上にゲート絶縁膜を形成し、P型不純物拡散層3及びアクティブ領域1aの上にゲート絶縁膜を介してゲート電極6を形成し、LOCOS酸化膜2及びゲート電極6をマスクとして不純物をイオン注入することにより、アクティブ領域にソース・ドレイン領域の拡散層7を形成することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】SOI層の膜厚が薄膜化してもMOSトランジスタの駆動能力の向上を図ることができる半導体装置及びその製造方法を得る。

【解決手段】NMOS形成領域A1に形成されるNMOSトランジスタQ11において、ソース・ドレイン領域15は埋め込み酸化膜4を貫通して半導体基板1の閾値電圧制御拡散層18に達して形成される。PMOS形成領域A2に形成されるPMOSトランジスタQ21において、ソース・ドレイン領域25は埋め込み酸化膜4を貫通して半導体基板1の閾値電圧制御拡散層28に達して形成される。

(もっと読む)

半導体装置

【課題】高耐圧で、安全動作領域が広く、かつ、熱散逸性がよく、有効コンダクタンスおよび周波数特性が良好なSOIデバイスを提供すること。

【解決手段】半導体装置100において、p-基板101の表面層の一部にはBOX領域102が設けられる。BOX領域102は、ゲート電極110の中心から下ろした垂線Lc付近まで設けられており、ドレイン領域109および拡張ドレイン領域103をp-基板101から分離する。ドレイン領域109の厚さは150nm〜300nmのいずれかであり、BOX領域102の厚さは150nm以上である。

(もっと読む)

半導体装置、その製造方法及び不揮発性半導体記憶装置

【課題】接合容量の低減と基板浮遊効果の抑制とを同時に図り、低コストで製造を可能にする。

【解決手段】半導体基板10は、シリコン基板11と、このシリコン基板11上に形成された薄いシリコンゲルマニウム層12と、このシリコンゲルマニウム層12上に形成されたシリコン層13とを有する。シリコンゲルマニウム層12は、シリコン基板11とシリコン層13とを、ワード線WL方向の中央部でのみ接続し、半導体基板10の中で狭隘部12aを形成している。シリコン層13は、メモリセルM及び選択ゲートトランジスタSGに対応する部分が活性領域を形成している。

(もっと読む)

窒化物半導体結晶成長基板、窒化物半導体素子および窒化物半導体結晶成長基板の製造方法

【課題】パワーデバイスの材料として適したIII族窒化物半導体結晶成長基板およびその製造方法、ならびに、そのIII族窒化物半導体結晶成長基板を用いて形成されるIII族窒化物半導体素子を提供すること。

【解決手段】この電界効果トランジスタは、積層界面がGaN膜2の主面2Aと斜めに交差するように、GaN膜2の主面2A側から順に積層された、N型GaN層6、P型GaN層7およびN型GaN層8を備える窒化物半導体積層構造部5を備えている。また、N型GaN層6、P型GaN層7およびN型GaN層8の各端面は、それぞれGaN膜2の主面2Aに平行な方向に沿って露出する露出面61、露出面71および露出面81となっている。

(もっと読む)

半導体デバイス及びその製造方法

【課題】S−factorを効果的に低減可能は半導体ディバイスを提供すること及び、S−factorを効果的に低減可能は半導体ディバイスの製造方法を提供すること。

【解決手段】本発明は、半導体基板に素子分離領域によって分離されて形成される半導体デバイスにおいて、前記半導体基板に形成されるチャネル部と;前記チャネル部の上に形成されるゲート絶縁膜と;前記ゲート絶縁膜上に形成されるゲート電極と;前記チャネル部の下部にのみ形成される埋め込みシリコン酸化膜とを備える。

(もっと読む)

フィンFETデバイスの構造およびその製造方法

【課題】フィンFET構造およびその製造方法を提供する。

【解決手段】バルク・シリコン基板の上面にシリコンのフィンを形成するステップと、前記フィンの両側の側壁にゲート誘電体を形成するステップと、前記フィンの前記両側の側壁上の前記ゲート誘電体層と直接に物理的にコンタクトするようなゲート電極を形成するステップと、前記チャネル領域の第1の側の前記フィン中に第1のソース/ドレインを形成し、かつ前記チャネル領域の第2の側の前記フィン中に第2のソース/ドレインを形成するステップと、ボイドを生じるために、前記第1および第2のソース/ドレインの少なくとも一部の下方から前記バルク・シリコン基板の一部を除去するステップと、前記ボイドを誘電体材料で以って充填するステップとを含む方法である。構造は、フィンFETのシリコン・ボディとバルク・シリコン基板との間にボディ・コンタクトを含む。

(もっと読む)

改善されたSOI基板およびSOIデバイス、ならびにそれらの形成方法

【課題】パターン形成された埋込み絶縁体層を異なる深さに含む、改善されたセミコンダクタ・オン・インシュレータ(SOI)基板を提供する。

【解決手段】具体的には、SOI基板は、実質的に平坦な上面を有し、さらに、(1)どのような埋込み絶縁体も含まない第1の領域と、(2)パターン形成された埋込み絶縁体層の第1の部分を第1の深さ(すなわち、SOI基板の平坦な上面から測定した深さ)に含む第2の領域と、(3)パターン形成された埋込み絶縁体層の第2の部分を第2の深さに含む第3の領域とを含み、第1の深さは、第2の深さより大きい。1つ以上の電界効果トランジスタ(FET)をSOI基板中に形成することができる。例えば、FETは、SOI基板の第1の領域中のチャネル領域、SOI基板の第2の領域中のソース領域およびドレイン領域、ならびにSOI基板の第3の領域中のソース/ドレイン拡張領域を含み得る。

(もっと読む)

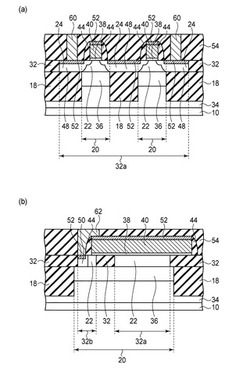

ソース領域とドレイン領域との間にボックス層を有する歪みシリコンMOSデバイス

MOSデバイスは、ゲート誘電体上に配置されたゲート電極を有するゲートスタックと、ゲートスタックの両側面に形成された第1のスペーサ及び第2のスペーサと、第1のスペーサに近接するソース領域と、第2のスペーサに近接するドレイン領域と、ゲートスタックの下に位置し且つソース領域とドレイン領域との間に配置されたチャネル領域とを有する。本発明に従ったMOSデバイスは更に、チャネル領域の下に位置し且つソース領域とドレイン領域との間に配置された埋め込み酸化物(BOX)領域を含む。BOX領域は、サリサイドスパイク不良を防止しながらトランジスタの抵抗及びゲート端部の接合寄生キャパシタンスを低減させるよう、より深いソース及びドレイン領域が形成されることを可能にする。  (もっと読む)

(もっと読む)

半導体装置の製造方法およびこの方法によって得られた半導体装置

本発明は、電界効果トランジスタを有する半導体装置(10)の製造方法に関し、この方法において、シリコン製の基板(11)を有する半導体基体(12)の表面に、埋め込み分離領域(3,4)の上に設置した第1導電型のソース領域(1)およびドレイン領域(2)と、ソース領域とドレイン領域(1,2)との間にあり、第1導電型と反対の第2導電型のチャネル領域(5)と、ゲート誘電体(7)によって半導体基体(12)の表面から離れ、チャネル領域(5)上に設置したゲート領域(6)と、を設け、また、メサ(M)を、チャネル領域(5)を形成する半導体基体(12)内に形成し、ソースおよびドレイン領域(1,2)を、エピタキシャル成長を用いて形成する半導体領域(8)でメサ(M)の両側の側面上に形成し、したがって、ソースおよびドレイン領域(1,2)は、チャネル領域(5)と接触するものとする。本発明によれば、半導体領域(8)は、半導体領域(8)の厚さのほぼ全体にわたりメサ(M)と接触するよう形成し、また、ゲート誘電体のレベルより下方に形成する。この方法は、より用途が広く、したがって、得られた装置(10)は、改善された高周波挙動を有する。  (もっと読む)

(もっと読む)

半導体装置

【課題】トップゲート電極とバックゲート電極とを自己整合的に形成し、バックゲート電極とソース領域及びドレイン領域とのオーバーラップ容量の低減を図る。

【解決手段】半導体装置は、半導体基板11と、半導体基板の上方に設けられたチャネル領域Cと、チャネル領域の上方に第1のゲート絶縁膜18aを介して設けられた第1のゲート電極G1と、チャネル領域の下方に第2のゲート絶縁膜18bを介して設けられ、第1のゲート電極と対向して配置された第2のゲート電極G2と、第2のゲート電極の側面を覆う第1の絶縁膜24と、第2のゲート電極の底面を覆う第2の絶縁膜12と、第1のゲート絶縁膜の上面よりも上方に位置する上面USと第1のゲート電極の側面に対向する側面SSとを有し、ソース領域及びドレイン領域が形成された半導体層26とを具備し、第2のゲート電極の側面SSG2は、半導体層の側面SSと一致する。

(もっと読む)

チップ、FET製造方法(誘電体ストレッサ要素を有するトランジスタ)

【課題】活性半導体領域の中に配置されたチャネル領域、ソース領域およびドレイン領域を有する電界効果トランジスタの特性向上のため、素子分離領域の配置に影響を与えずに効果的な応力を付加する構造の提供。

【解決手段】トレンチ分離領域106により分離された活性半導体領域104の一部分の下に、水平に延びる上面を有する埋め込み誘電体ストレッサ要素102が配置される。この誘電体ストレッサ要素は、多孔質シリコンの酸化による酸化膜で構成され、多孔質化の度合いにより圧縮または引っ張り応力を発生する。

(もっと読む)

半導体装置の製造方法及び、半導体装置

【課題】 特殊な製造装置は不要で、製造時の結晶欠陥の発生を抑えたDSOIトランジスタを有する半導体装置の製造方法及び、半導体装置を提供する。

【解決手段】 まず始めに、Si基板1上にSiGe層3を形成し、SiGe層3のうちのソース形成領域とドレイン形成領域とに挟まれた部分をエッチングして取り除き、トレンチを形成する。次に、このトレンチ内が埋め込まれ且つSiGe層3上が覆われるように、Si基板1上にSi層10を形成する。そして、トランジスタ形成領域の外側にあるSi層10と、当該外側にあるSiGe層3とを順次エッチングして取り除くことにより、トランジスタ形成領域の周囲に沿ってSiGe層3の側面を露出させる。その後、SiGe層3をその露出した側面からエッチングして取り除くことにより、トランジスタ形成領域のSi層10下に空洞部15を形成し、続いて、この空洞部15内にSiO2膜17を形成する。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

本発明は、半導体基材(100)を有する半導体素子に関し、さらに以下の各特徴として、上記半導体基材(100)内にて、第1の伝導型のドリフト領域(2;211)と、上記半導体基材(100)内にて、上記ドリフト領域(2)に対し、少なくとも部分的に隣り合って配置され、半導体材料からなるドリフト制御領域(3;241)と、上記ドリフト領域(2;211)と上記ドリフト制御領域(3;241)との間に配置された蓄積誘電体(4;251)とを含む。  (もっと読む)

(もっと読む)

半導体素子及びその製造方法

【課題】寄生キャパシタンスの低下及びパンチスルー特性の改善により、リフレッシュ特性を向上させた半導体素子及びその製造方法を提供すること。

【解決手段】半導体素子は、半導体基板201上に形成されて活性領域を提供し、側壁下部端に凹部が形成された半導体層203、204と、素子分離用の第1の絶縁膜202Aと、第1の絶縁膜202及び半導体層203、204の側壁に形成された素子分離用の第2の絶縁膜206とを備えている。半導体素子の製造方法は、半導体基板201の一部の領域を露出させた第1の絶縁膜202Aを形成するステップ、第1の半導体層203を形成するステップ、第2の半導体層204Aを形成するステップ、第2の半導体層204A及び第1の絶縁膜202Aを選択的にエッチングするステップ、第1の絶縁膜202Aを除去するステップ及び第2の絶縁膜206を形成するステップを含む。

(もっと読む)

加算素子及びその駆動方法

【課題】共通中間電極109の電位が、いわゆる電界効果型トランジスタのサブスレッショルド領域にある場合が多く発生するので、ソース101とドレイン103の間を流れる電流が大きくなり、結果として消費電力が増加する。

【解決手段】共通中間電極5と、共通中間電極5に複数のキャパシタを介して接続された複数の入力ゲート電極9と、共通中間電極5と接続された閾値素子53とからなる加算素子51であって、入力ゲート電極9の少なくとも一部が電圧発生器31に接続されているので、非使用時の電力消費を抑制することができる。

(もっと読む)

半導体素子及びその製造方法

【課題】接合漏洩電流とキャパシタンスを低減させ短チャンネル効果を改善して素子の特性を向上させる。

【解決手段】本発明に係る半導体素子及びその製造方法は、ソース/ドレーン領域のうちいずれか一つとチャンネル領域の一部は半導体基板の上部に形成された埋込酸化膜の上部に備えられ、ソース/ドレーン領域のうち他の一つとチャンネル領域の残りは半導体基板の上部に形成されたSiエピタキシャル層の上部に備えられる。

(もっと読む)

1 - 20 / 24

[ Back to top ]