Fターム[5F140AC28]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 歪みを利用したもの (848)

Fターム[5F140AC28]に分類される特許

841 - 848 / 848

ストレインド・シリコン電圧制御発振器(VCO)

ストレインド・シリコン電圧制御発振器(VCO)は、ストレインド・シリコン層を有する第1Pチャネル金属酸化膜半導体(PMOS)装置を含み、ストレインド・シリコン層を有する第2PMOS装置に結合される。  (もっと読む)

(もっと読む)

キャリア移動度を増加させた電界効果トランジスタ

ある例示的な実施形態によれば、基板(104)上に位置するFETは、基板(104)中に位置するチャネル(112)を含んでいる。このFETはさらに、チャネル(112)上に位置する第1ゲート絶縁層(116)を含んでいる。この第1ゲート絶縁層(116)は、第1熱膨張係数を有している。FETはさらに、第1ゲート絶縁層(116)上に位置する第1ゲート電極(114)を含んでいる。この第1ゲート電極(114)は、FET中のキャリア移動度を増加させるように、第1熱膨張係数と異なる第2熱膨張係数を有している。この第2熱膨張係数は、例えば第1熱膨張係数よりも大きくされている。キャリア移動度の増加は、例えばチャネル(112)中に生成された引っ張り歪みにより引き起こされる。  (もっと読む)

(もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

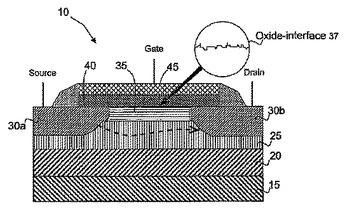

格子不整合のソースおよびドレイン領域を有する歪み半導体CMOSトランジスタを有する集積回路および製作方法

【課題】 p型電界効果トランジスタ(PFET)およびn型電界効果トランジスタ(NFET)を有する集積回路を提供することにある。

【解決手段】 第1の歪みは、NFETではなくPFETのみのソースおよびドレイン領域内に配置されたシリコン・ゲルマニウムなどの格子不整合半導体層を介してNFETではなくPFETのチャネル領域に加えられる。PFETおよびNFETを形成するプロセスが提供される。PFETのソースおよびドレイン領域になるためのエリア内にトレンチがエッチングされ、それに隣接するPFETのチャネル領域に歪みを加えるために、格子不整合シリコン・ゲルマニウム層をそこにエピタキシャル成長させる。シリコン・ゲルマニウム層の上にシリコンの層を成長させ、シリコンの層からサリサイドを形成して、低抵抗ソースおよびドレイン領域を提供することができる。

(もっと読む)

半導体基板におけるドーパントの拡散を低速化する方法およびこれにより製造されたデバイス

【課題】 ひずみSi/Si1-XGeXデバイス基板において、極めて浅い接合を形成する方法およびそれによって得られる半導体構造を提供する。

【解決手段】 半導体デバイスを形成する方法(およびその結果として得られる構造)は、基板上に、ドーパントおよび少なくとも1つの種を注入するステップと、基板をアニールするステップであって、少なくとも1つの種が、基板のアニールの間のトーパントの拡散を遅らせるステップと、を含む。

(もっと読む)

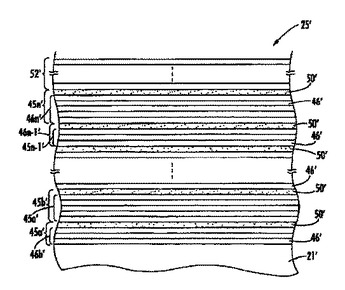

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。  (もっと読む)

(もっと読む)

半導体デバイス並びに量子井戸構造体を製造する方法及び量子井戸構造体を有する半導体デバイス

量子井戸構造体(4)を備える多重層構造体(3)を基板(2)上に得るための半導体デバイス(1)及び方法が開示されている。量子井戸構造体(4)は、絶縁物質(6、6’)によって挟まれる半導体層(5)を有し、絶縁物質(6、6’)の物質は好ましくは、高誘電率を有する。FETにおいて、量子井戸(4、9)はチャネルとして機能し、より高い駆動電流及びより低いオフ電流が可能になる。短チャネル効果が低減される。多重チャネルFETは、サブ35nmゲート長に対してさえも動作するのに適している。本方法において、量子井戸は、好ましくはMBEを用いて、半導体物質及び高誘電率物質のエピタキシャル成長によって互いの上に交互に形成される。

(もっと読む)

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

841 - 848 / 848

[ Back to top ]