Fターム[5F140BF04]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467) | 半導体 (3,081)

Fターム[5F140BF04]に分類される特許

2,001 - 2,020 / 3,081

金属シリサイド形成方法および半導体装置の製造方法

【課題】金属シリサイド層のグレインサイズを均一化することが可能であって、信頼性を向上する。

【解決手段】ソース・ドレイン領域21sdが形成された単結晶シリコンの半導体基板11や、ポリシリコンのゲート電極21gのように、シリコンを含む半導体領域においてシリサイド化が生ずる第1の温度にて、その半導体領域に第1金属を堆積することによって、第1金属層12を形成する。つぎに、その形成された第1金属層12を被覆するように、第1の温度より低い第2の温度にて、その半導体領域に第2金属13を堆積することによって、第2金属層を形成する。つぎに、第2金属層13が第1金属層12を被覆するように形成された半導体領域に対して熱処理を実施することによって、金属シリサイド層21gm,21sdmを形成する。

(もっと読む)

半導体装置の製造方法

【課題】

ポケットとエクステンションを備えたMOSトランジスタのポケットとエクステンションのオフセット距離の精度を向上する。

【解決手段】

半導体基板10の表面に形成したフィールド絶縁膜12の素子孔内にゲート絶縁膜14を形成した後、絶縁膜14及び12の上にドープトポリシリコン等からなるゲート電極16及びキャパシタ用下部電極18をそれぞれ形成する。絶縁膜12及び電極16をマスクとするイオン注入処理によりポケット領域20,22を形成した後、電極16,18を覆って絶縁層26をCVD法等により形成する。絶縁層26を介してのイオン注入処理によりエクステンション領域28,30を形成する。ポケット領域20,22とエクステンション領域28,30との間のオフセット距離Lは、絶縁層26の厚さに対応して精度良く決定される。サイドスペーサ形成処理の後、高濃度ソース/ドレイン領域を形成する。

(もっと読む)

エッチング方法及び半導体装置の製造方法

【課題】Si(シリコン)、SiN、レジスト、NiSi、CoSi、酸化物等に対するSiGe(シリコンゲルマニウム)の選択比をあげることができ、Si(シリコン)とSiGe(シリコンゲルマニウム)のヘテロ構造部分に対する加工精度を高くできるエッチング方法及びこれを用いた半導体装置の製造方法を提供すること。

【解決手段】SiGe(シリコンゲルマニウム)層と、SiGe(シリコンゲルマニウム)層の上に形成されたSi(シリコン)層と、を含むヘテロ構造体をエッチングするマイクロ波プラズマエッチング方法であって、反応ガスとしてフッ化物ガスのみを用い、その流量を10〜800sccm、処理圧力を266Pa以下、マイクロ波パワーを150〜400W、処理温度を5〜25℃として、SiGe(シリコンゲルマニウム)層を選択的に等方性エッチングする。

(もっと読む)

半導体装置およびその製造方法

【課題】凹部の埋め込み性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に互いに並走する導電層1、1が形成されている。各導電層1上には上層絶縁層2と保護絶縁層3とが積層して積層構造が形成されている。この積層構造の側壁を覆うように側壁絶縁層4、5が形成されている。半導体基板10の表面に平行な方向における側壁絶縁層5、5の間隔(凹部7の寸法)が側壁絶縁層5の上部において大きく(寸法W3)、下部において小さく(寸法W4)なるように側壁絶縁層5はその上部と下部との間に段差部Pを有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】STI構造において素子分離絶縁膜を、高密度プラズマCVD法を使って、引張り応力を蓄積するように形成する。

【解決手段】半導体装置の製造方法は、半導体基板表面に、素子分離溝を形成する工程と、前記半導体基板表面にシリコン酸化膜を、高密度プラズマCVD法により、前記シリコン酸化膜が前記素子分離溝を充填するように、また前記シリコン酸化膜中に水分が、前記シリコン酸化膜を脱水処理した場合、前記シリコン酸化膜に収縮が生じるような量で含まれるように堆積する工程と、前記シリコン酸化膜を脱水し、前記シリコン酸化膜に収縮を誘起する工程と、前記シリコン基板上に堆積したシリコン酸化膜を、前記半導体基板表面が露出するまで化学機械研磨により除去する工程とよりなる。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜とゲート電極との間に金属粒子を備えた半導体装置において、ゲート電極の仕事関数の調整(閾値電圧の制御)と空乏化の抑制に加え、さらに金属粒子とこの周囲の膜との密着性を向上させた半導体装置を提供する。

【解決手段】 p型シリコン基板1、埋め込み酸化膜2、及び単結晶シリコン層3から構成されるSOI基板4において、単結晶シリコン層3にソース領域10およびドレイン領域11を備える。ソース領域10とドレイン領域11との間の単結晶シリコン層3の表面側はチャネル層3aとして機能する。チャネル層3aの上にはゲート絶縁膜5が形成される。ゲート絶縁膜5上には、窒化チタンからなる金属粒子6aと多結晶シリコン膜7から構成されるゲート電極8が設けられる。ここで、金属粒子6aと多結晶シリコン膜7との間にはチタンシリサイド反応層6bが形成され、金属粒子6aとゲート絶縁膜5との間には反応層6cが形成される。

(もっと読む)

MOSトランジスタとその製造方法

【課題】 高耐圧を確保し、且つ駆動能力の高い安定した特性をもつLOCOSオフセット型MOSトランジスタを提供する。

【解決手段】 LOCOSオフセット型MOSトランジスタにおいて、オフセット領域に濃度1×1016 〜1×1018 atoms/cm3の低濃度拡散領域を形成し、ドレイン領域に高濃度拡散領域を形成し、高濃度ドレイン領域を囲み、オフセットに用いるLOCOSのドレイン領域側のバーズビーク下部まで達する、濃度が低濃度拡散領域の2〜100倍である中濃度拡散領域を形成することを特徴とするドレイン構造を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】high−k(高誘電率)膜を含むゲート絶縁膜を用いたMISトランジスタの信頼性および特性を向上させる。

【解決手段】ゲート長が10nm以下のMISトランジスタにおいて、シリコン基板11上に形成された酸化シリコン膜4およびその酸化シリコン膜4上に形成されたhigh−k膜5を含んでなるゲート絶縁膜2は、ゲート長方向において中央より側面側で窒素を多く含み、かつ、膜厚方向において下面側より上面側で窒素を多く含む窒素領域21を有している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力印加膜の膜厚の増大が容易な半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置が,半導体基板,ゲート絶縁膜,ゲート電極,ゲート側壁絶縁膜,層間絶縁膜,配線層,層間接続部,応力印加膜と,を具備する。この応力印加膜は,半導体基板と層間絶縁膜との間に配置される第1の部分と,ゲート電極と層間絶縁膜との間に配置される第2の部分と,ゲート側壁絶縁膜と層間絶縁膜との間に配置される第3の部分と,貫通孔の内面と層間接続部との間に配置される第4の部分と,を有し,かつ半導体基板に応力を印加する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体プロセスの微細化に伴い、信頼性の高い微細なゲート電極の形成がより困難なものとなっている。

【解決手段】ゲート電極105の上面に加え、ゲート電極105の側面に対しても金属シリサイド110を形成することで、ゲート電極105を所望の太さの幅に拡大しなくても、信頼性の高いゲート電極105を形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 接合リークを誘起することなく、MOSFETの極性に依存した応力をチャネル部分に効果的に発生させることができ、C−MOSFETの高速化をはかる。

【解決手段】 チャネルを構成する半導体領域に方向によって極性の異なる機械的応力を付与した半導体装置であって、表面内の第1の方向D1に圧縮応力16−1,16−2を有し、表面内の方向D1とは異なる第2の方向D2に引っ張り応力17−1,17−2を有する半導体領域11と、半導体領域11上に形成され、方向D1に沿って対向配置されたソース・ドレイン領域を有する第1導電型の電界効果型トランジスタ21と、半導体領域11上に形成され、方向D2に沿って対向配置されたソース・ドレイン領域を有する第2導電型の電界効果型トランジスタ22を備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パワー用半導体素子のドレイン領域でのシート抵抗値を低減させることが難しいという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板3上に、2層のN型のエピタキシャル層4、5が形成されている。基板3の裏面49からはドレイン領域として用いられるN型の埋込拡散層20が露出している。そして、基板3の裏面49側には、N型の埋込拡散層20とコンタクトする金属層50が形成されている。この構造により、金属層50がドレイン領域として用いられ、ドレイン領域でのシート抵抗値を大幅に低減することができる。

(もっと読む)

不純物ドーピング領域を含む半導体素子及びその形成方法

【課題】高集積化に最適化された、不純物ドーピング領域を含む半導体素子及びその形成方法を提供する。

【解決手段】この方法は、半導体基板にクラスタ型ドーパントイオンを注入して不純物注入領域を形成する段階(S200)と、前記不純物注入領域にレーザアニーリング工程を実行して不純物ドーピング領域を形成する段階(S210)とを含む。

(もっと読む)

半導体装置

【課題】コレクタ・エミッタ電流特性を向上させ、下降時間を短縮し、更に寄生サイリスタのラッチアップ耐量を向上させた半導体装置を提供する。

【解決手段】 半導体装置が、第1導電型の半導体基板と、半導体基板に設けられた第2導電型の半導体領域と、半導体領域中に設けられた第1導電型のコレクタ層と、半導体領域中に、コレクタ層から間隔を隔ててコレクタ層を囲むように設けられた無端状の第1導電型のベース層と、ベース層中に設けられた第2導電型の第1エミッタ層とを備え、第1エミッタ層とコレクタ層との間のキャリアの移動を、ベース層に形成されるチャネル領域で制御する横型の単位半導体素子を含む。第1エミッタ層は、ベース層に沿って設けられた複数の単位エミッタ層からなる。

(もっと読む)

半導体装置およびその製造方法

【目的】同一半導体基板に複数形成されるTLPMのそれぞれの素子を精度よく最適化を図り、また製造コストの低減を図ることができる半導体装置およびその製造方法を提供する。

【解決手段】相補型のTLPMのPchTLPMの第2トレンチ12の深さよりNchTLPMの第1トレンチの深さを浅くすることで、NchTLPMのチャネル長の最適化を図りオン抵抗を小さくすることができる。また第1トレンチと第1nドレイン領域を形成するマスクを同一とし、第2トレンチと第1pドレイン領域を形成するマスクを同一とすることで、フォト工程を減らして低コスト化を図ることができる。また、セルフアラインにより第1nドレイン領域を高精度に形成できる。

(もっと読む)

半導体装置の製造法

【課題】本発明の目的は、ゲート絶縁膜中への不純物混入の抑制と元素欠陥を除去することができ、ゲート絶縁膜の固定電荷フリ−とリ−クの発生等を抑制できる半導体装置の製造法を提供することにある。

【解決手段】本発明は、シリコン単結晶基板上に、ゲート絶縁膜を形成する半導体装置の製造法において、前記ゲート絶縁膜を、水酸化アンモニウムガスと、ハフニウムの化合物ガスとを用いてOH基に交換されたシリコン単結晶基板表面に特定の反応によって形成された金属の酸化−水酸化物を酸化性雰囲気中で熱処理してSiとHfとの複合酸化物からなる膜を形成することを特徴とする。

(もっと読む)

ハイブリッド・チャネル配向を伴うCMOS素子およびその製造方法

【課題】

特定の素子に最適な性能を提供する、異なる表面配向(すなわちハイブリッド表面配向)を有する半導体基板を提供すること。

【解決手段】

本発明は、少なくとも第1および第2の素子領域を備える半導体基板に関し、第1の素子領域は等価結晶面の第1のセットに沿って配向された内部表面を有する第1の凹部を備え、第2の素子領域は等価結晶面の第2の異なるセットに沿って配向された内部表面を有する第2の凹部を備える。半導体素子構造は、こうした半導体基板を使用して形成することができる。具体的に言えば、少なくとも1つのnチャネル電界効果トランジスタ(n−FET)を、第1の凹部の内部表面に沿って延在するチャネルを備えた、第1の素子領域に形成することが可能である。少なくとも1つのpチャネル電界効果トランジスタ(p−FET)を、第2の凹部の内部表面に沿って延在するチャネルを備えた、第2の素子領域に形成することが可能である。

(もっと読む)

半導体素子

【課題】シリコン系基板上に窒化物系半導体層が形成され、漏れ電流を抑制するとともに高速動作を可能にする半導体素子を提供する。

【解決手段】半導体素子1はシリコン系基板2を備えている。シリコン系基板2上には、窒化物系化合物から構成された窒化物系半導体層3が形成されている。窒化物系半導体層3上には、窒化物系半導体層3とショットキー接合を有するアノード電極4と、窒化物系半導体層3とオーミック接触されたカソード電極5とが形成されている。シリコン系基板2の下面には、アノード電極4と電気的に接続された下部電極6が形成されている。下部電極6は、シリコン系基板2とショットキー接合を有し、仕事関数の大きい金属または合金から構成されている。

(もっと読む)

半導体装置の製造方法

【課題】段差部に近接した領域に導電体パターン(例えばゲート電極)が形成される場合に、導電体パターンの寸法精度を高くすることができる半導体装置の製造方法を提供する。

【解決手段】本半導体装置の製造方法は、素子分離膜2上、絶縁膜12上、及びゲート絶縁膜3b〜3d上に導電膜4を形成する工程と、絶縁膜12とゲート絶縁膜3bの間に位置する導電膜4に開口部4eを形成する工程と、導電膜4上及び開口部4e内にフォトレジスト膜51を形成し、その後露光及び現像することにより、ゲート絶縁膜3bから3dそれぞれの上方に位置するレジストパターン51b〜51d、及び絶縁膜12の上方に位置するレジストパターン51aを形成する工程と、レジストパターン51a〜51dをマスクとして導電膜4をエッチングすることにより、ゲート電極4b〜4d及び上部導電膜4aを形成する工程とを具備する。

(もっと読む)

半導体素子及びその製造方法

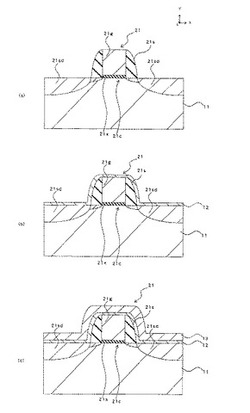

【課題】半導体素子及びその製造方法に関し、特に所定の活性領域とこれと隣接した素子分離構造を露出するアイランド型リセスゲートマスクを利用してリセスチャンネル領域とその下部にフィン型チャンネル領域を形成するよう半導体素子を設計することにより、素子の書込み及び読取り速度を向上させることができ、素子のリフレッシュ特性を改善することができる技術を提供する。

【解決手段】半導体基板110に活性領域を画成する素子分離構造120と、アイランド型リセスゲートマスクにより露出された活性領域とこれと隣接した素子分離構造を所定厚さに食刻して形成されたリセスと、リセス下部の半導体基板に形成されたフィン型チャネル領域155と、フィン型チャネル領域155とリセスを含む活性領域上部に形成されるゲート絶縁膜160と、フィン型チャネル領域とリセスを埋め込み、ゲート領域のゲート絶縁膜上部に形成されるゲート電極197を含む。

(もっと読む)

2,001 - 2,020 / 3,081

[ Back to top ]