Fターム[5F140BG02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ダミーゲートを用いたゲート電極の製造 (506) | ダミーゲート材料(レジスト、ポリイミド) (470)

Fターム[5F140BG02]の下位に属するFターム

無機物 (413)

Fターム[5F140BG02]に分類される特許

41 - 57 / 57

炭化ケイ素半導体装置の製造方法および炭化ケイ素半導体装置

【課題】オーミックコンタクト抵抗が低減できるようなオーミックコンタクト形成のためのアニール処理を施した、炭化ケイ素(000-1)面上に絶縁膜を有する半導体装置の製造方法および半導体装置を提供すること。

【解決手段】炭化ケイ素半導体の(000-1)面8上に、少なくとも酸素と水分を含むガス中で熱酸化し前記炭化ケイ素半導体の(000-1)面8上に接するように絶縁膜18を形成する工程と、絶縁膜18の一部を除去し開口部を形成する工程と、開口部の少なくとも一部にコンタクトメタル20を堆積する工程と、熱処理によりコンタクトメタル20と炭化ケイ素の反応層21を形成する工程とを有する炭化ケイ素半導体装置の製造方法において、前記熱処理を不活性ガスと水素の混合ガス中にて実施することを特徴とする炭化ケイ素半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、バックゲート領域としての拡散層の形成領域がばらつくことで、オン抵抗値が安定しないという問題があった。

【解決手段】本発明の半導体装置では、ドレイン領域は、不純物濃度の異なるN型の拡散層9〜14により構成されている。高不純物濃度であるN型の拡散層11、14の形成領域も広い領域に渡り、N型の拡散層11、14より低不純物濃度のN型の拡散層10、13が形成されている。そして、P型の拡散層5が、N型の拡散層10、13の形成領域に収束している。この構造により、P型の拡散層5がばらついた場合でも、Nチャネル型MOSトランジスタ1のオン抵抗値を安定させることができる。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを用いた半導体装置の製造方法において、RPTの短縮、ゲート寸法の加工精度の向上を図る半導体装置の製造方法を提供する。

【解決手段】半導体基板上にダミーゲートを形成する工程、前記ダミーゲートをマスクとして前記半導体基板に不純物を導入して、ソース・ドレイン拡散領域を形成する工程、前記ダミーゲートの周囲に絶縁膜を形成する工程、前記ダミーゲートを除去して開口部を形成する工程、及び前記開口部にゲート絶縁膜を介してゲート電極を形成する工程を具備する方法である。前記ダミーゲートは、前記半導体基板上に、炭素と水素との原子比(C/H)が1以上であり、かつ炭素の絶対量が50%以上である炭素過剰の組成のポリマーを塗布してポリマー膜を形成する工程、前記ポリマー膜上にフォトレジストパターンを形成する工程、及び前記フォトレジストパターンを前記ポリマー膜に転写する工程により形成されることを特徴とする。

(もっと読む)

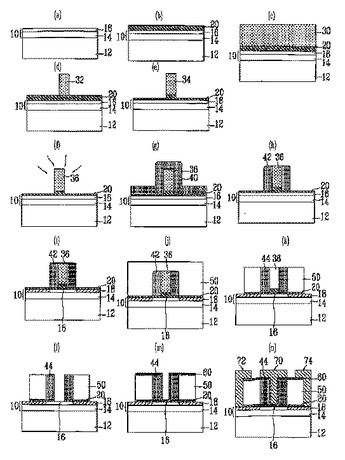

半導体素子の製造方法

本発明は、リソグラフィ工程を経たフォトレジストの特性を変化させてダミー構造物を形成し、これをゲート電極形成工程に適用した半導体素子の製造方法に関することで、半導体基板上の最上部にバッファー層を形成するステップと、前記バッファー層の上部に無機物フォトレジストを塗布してリソグラフィを通じてフォトレジストパターンを形成するステップと、前記形成されたパターンに特定ガスを使用して熱処理を行うステップと、前記熱処理された構造物の上部に均一な厚さの絶縁膜を蒸着した後に前記パターンが露出されるように前記蒸着された膜をエッチングするステップと、前記工程を経た構造物に絶縁膜を蒸着し、前記パターンが露出されるように前記絶縁膜をエッチングするステップと、前記露出されたパターンを除去するステップと、前記パターンが除去された位置にゲート酸化膜を形成するステップと、前記形成されたゲート酸化膜の上部にゲート電極を形成するステップと、を含む。本発明によれば、ナノ素子を製作するための構造を形成する時、リソグラフィを通じて形成された膜の特性が後続熱処理を通じて改善されるので、多様な素子を製作するための構造を容易に形成することができる。  (もっと読む)

(もっと読む)

スペーサレスFET及びデュアル・ライナ法による歪み強化を増加させる構造体及び方法

【課題】 スペースレスFET及びデュアル・ライナ法による歪み強化を増加させる構造体及び方法を提供する。

【解決手段】 歪み強化がnFET及びpFETデバイスの両方に対して達成される半導体構造体及びそれを製造する方法を提供する。特に、本発明は、より強い歪み強化及び欠陥削減のための少なくとも1つのスペーサレスFETを提供する。少なくとも1つのスペーサレスFETは、pFET、nFET又はそれらの組合せとすることができるが、一般に、pFETはnFETよりも大きな幅を有するように製造されるので、スペーサレスpFETが特に好ましい。少なくとも1つのスペーサレスFETは、スペーサを有するFETを含んだ従来技術の構造体よりも、デバイス・チャネルにより接近した応力誘起ライナを設けることを可能にする。スペーサレスFETは、スペーサレスFETの下側に侵入しない、対応するシリサイド化ソース/ドレイン拡散コンタクトの抵抗に悪影響を与えることなく達成される。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート電極の中心に対して対称なMOS電界効果トランジスタの耐圧を劣化させず微細化を可能にするトランジスタ及びその製造方法を提供する。

【解決手段】ゲート電極103と対称的にゲートオーバーラップ構造の電界緩和層107A、107Bとパンチスルーストッパー層108を有するMOS電界効果トランジスタにおいて、N型パンチスルーストッパー層108の表面に、このパンチスルーストッパー層108とは反対導電型のP型層110を設け、しきい値電圧が上昇しないようにしたもの。

(もっと読む)

半導体装置およびその製造方法

【課題】 、耐圧特性が向上された半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置1は、半導体基板11と、半導体基板11表面に形成された一対の低濃度拡散領域17sおよび17dと、半導体基板11表面に形成されたゲート絶縁膜13と、半導体基板11表面にゲート絶縁膜13を介して形成されたゲート電極15とを有する。ゲート電極15のドレイン(17d)側の側面は、ゲート幅方向と平行な第1側面と、第1側面よりもゲート長方向に突出した第2側面と、第2側面の両端で第1側面と第2側面とを結ぶ第3側面とを含んでなる櫛歯状電極部15aを有する。

(もっと読む)

半導体装置の製造方法

【課題】 特性や信頼性に優れた半導体装置を作製することが可能な製造方法を提供する。

【解決手段】 Si基板上のゲート形成予定領域にダミーゲートを形成する工程と、このダミーゲートの両側に対応する領域のSi基板内に不純物を導入し熱処理によってこの不純物を活性化することによりソース・ドレイン領域23、25を形成する工程と、ダミーゲートの側壁を取り囲む絶縁膜24、26を形成する工程と、ダミーゲートを除去して開口部を22a形成する工程と、この開口部が形成された領域又はその下部領域にSiGe層28を形成する工程と、開口部に露出しているSiGe層上にゲート絶縁膜29を介してゲート電極30、31を形成する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を十分に向上することができる半導体装置およびその製造方法を提供する。

【解決手段】MOSFET30は、SiC膜11を備えている。SiC膜11はその表面にファセット形成層11aを有しており、ファセット形成層11aのファセットの一周期の長さP1は100nm以上であり、ファセット形成層11aをチャネル16としている。また、MOSFET30の製造方法は、SiC膜11を形成する工程と、SiC膜11の表面にSiを供給した状態で、SiC膜11を熱処理する熱処理工程と、熱処理工程によってSiC膜11の表面に得られたファセットをチャネル16とする工程とを備えている。

(もっと読む)

厚いエッジゲート絶縁膜パターンを有するMOS電界効果トランジスタ及びその製造方法

【課題】GIDLを防止して耐圧特性が向上したMOS電界効果トランジスタを提供する。

【解決手段】半導体基板の所定領域に配置されて活性領域を限定する素子分離領域を含み、活性領域内でチャンネル領域を介在してソース領域及びドレイン領域が互いに離隔されて形成されており、ソース領域とドレイン領域間の活性領域上にゲート電極が形成されており、活性領域とゲート電極との間にゲート絶縁膜が形成されているトランジスタ。ゲート絶縁膜は、ゲート電極の中央下部に位置する中央ゲート絶縁膜とゲート電極のエッジ下部に位置して底が中央ゲート絶縁膜の底と同じレベルであるが、上部面が中央ゲート絶縁膜の上部面より高く突出されたエッジゲート絶縁膜を含む。

(もっと読む)

高電圧半導体装置及びその製造方法

【課題】高電圧半導体装置及びその製造方法が開示される。

【解決手段】高電圧半導体装置及びその製造方法において、第1深さを有する複数のドリフト領域は、半導体基板に第1不純物をドーピングして、それぞれ互いに離隔してチャンネル領域を限定するように形成される。第1深さに対して浅い第2深さを有するソース/ドレイン領域は、ドリフト領域に第2不純物をドーピングして形成される。第1深さに対して浅い第3深さを有する不純物蓄積領域は、ソース/ドレイン領域と隣接するドリフト領域に第3不純物をドーピングして形成される。ソース/ドレイン領域を部分的に露出させるゲート絶縁膜パターン及びチャンネル領域のゲート絶縁膜パターン上にゲート導電膜パターンが形成される。ゲート絶縁膜パターン及びゲート導電膜パターン上に急激に電流が増加することを顕著に減少させるバッファ膜が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層と半導体基板との間での接合リークを防止することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1上にゲート絶縁膜2を介して形成されたゲート電極3と、ゲート電極3の両側における半導体基板1上に形成され、エクステンション領域となる第1エピタキシャル成長層5と、ゲート電極3の側面および第1エピタキシャル成長層5の一部を被覆するサイドウォール絶縁膜SWと、サイドウォール絶縁膜SWから露出した第1エピタキシャル成長層5上に形成され、ソースあるいはドレインとなる第2エピタキシャル成長層6と、サイドウォール絶縁膜SWから突き出た第2エピタキシャル成長層6の側面に形成され、当該側面におけるシリサイド層7の形成を防止する側壁保護膜13と、第2エピタキシャル成長層6の表面に形成されたシリサイド層7とを有する

(もっと読む)

半導体装置及びその製造方法

【課題】 スパイクや金属配線に含有される析出物による劣化のないゲート絶縁膜と、高い仕事関数を有するゲート電極とを含む半導体装置、及び、少ないレジストマスク形成行程を介して製造可能な該半導体装置の製造方法を提供することを目的とする。

【解決手段】 ゲート酸化膜16上に、ポリシリコン膜17を形成する。ゲート酸化膜16とポリシリコン膜17との積層体に、ソース・ドレインコンタクトを形成する。その後、該ポリシリコン膜17上及びソース・ドレインコンタクト中に金属膜18を形成して、該ポリシリコン膜17と該金属膜18とからなる積層体を形成する。その後、この積層体をパターニングして、各々が、ポリシリコン層と金属層との積層構造体からなるゲート電極と、ソース・ドレインコンタクト配線層とを同時に形成する。更に、フィールド酸化膜の形成に代え、チャネルストッパーを高濃度拡散領域と同時に形成する。

(もっと読む)

半導体基板の埋設分離領域を形成する方法及び埋設分離領域をもつ半導体デバイス

【課題】 半導体基板の埋設分離領域を形成する改善された方法と、埋設分離領域を有する半導体デバイスを形成し、なおかつデバイスの冷却及び本体電位制御を与える方法を提供する。

【解決手段】 半導体構造を形成する半導体構造及び方法である。半導体構造は、ナノ構造を含むか、又はナノ構造を用いて製造される。半導体構造を形成する方法は、ナノマスクを用いてナノ構造を生じさせ、生じさせられたナノ構造を用いて付加的な半導体加工ステップを行うことを含む。

(もっと読む)

半導体装置の製造方法

【課題】 ゲートシリサイドの断線を抑制することができる半導体装置の製造方法を得る。

【解決手段】 半導体基板上に絶縁膜を形成する工程と、絶縁膜に開口を形成する工程と、開口の底部で露出している半導体基板の表面にゲート酸化膜を形成する工程と、全面にポリシリコン膜を形成して開口を埋め込む工程と、開口を含む領域を覆うようにポリシリコン膜上にフォトレジストを形成する工程と、フォトレジストをマスクとしてポリシリコン膜及び絶縁膜を異方性エッチングして、ゲート電極と、ゲート電極の下部の側壁を覆うサイドウォールを形成する工程と、フォトレジストを除去する工程と、ゲート電極及びサイドウォールをマスクとして半導体基板に斜め方向からイオン注入してエクステンション領域を形成し、垂直方向からイオン注入してソース・ドレイン領域を形成する工程と、ゲート電極の表面及び半導体基板の表面に金属シリサイド膜を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート電極と異物の衝突を抑えることができる半導体装置の製造方法を得る。

【解決手段】 本発明に係る半導体装置の製造方法は、ゲート電極を有する半導体装置が表面に形成されたウェハをディスクの周縁内側に並べて、ディスクを回転させながらウェハの表面にイオン注入する半導体装置の製造方法において、異物のゲート電極への衝突角度に応じた高さのダミーのフォトレジストをウェハ内の分離酸化膜、ウェハの周辺部、又はダイシング部の上に形成する。

(もっと読む)

半導体装置の製造方法

【課題】 シリコン基板と絶縁膜の界面を改質して、特性の向上を図ること。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

41 - 57 / 57

[ Back to top ]