Fターム[5F140BG19]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | イオン注入時ゲート保護層(最外レジストを除く) (497) | ゲート保護材料(ゲート電極以外) (478)

Fターム[5F140BG19]の下位に属するFターム

Fターム[5F140BG19]に分類される特許

41 - 60 / 60

半導体装置の製造方法およびシリコン窒化膜またはシリコン酸化膜の表面処理方法

【課題】ハードマスク用として形成されたシリコン窒化膜またはシリコン酸化膜を選択的にエッチングした際の残渣を、下地にダメージを与えず、かつ残存しているハードマスクを大きくエッチングすることなく除去することができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板にエッチング対象膜を形成する工程と、エッチング対象膜の上にシリコン窒化膜またはシリコン酸化膜を形成する工程と、シリコン窒化膜またはシリコン酸化膜の表面に窒素を導入する工程と、シリコン窒化膜またはシリコン酸化膜を選択的にエッチング除去してエッチングマスクとする工程と、シリコン酸化膜またはシリコン酸化膜のエッチング残渣をウェットエッチングにより除去する工程と、エッチングマスクを介してエッチング対象膜をウェットエッチングする工程と、エッチングマスクを除去する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 コンタクトパッドを形成する半導体装置の製造方法において、隣接する半導体素子間のショートを防止する。

【解決手段】 シリコン基板11上に、それぞれが金属層15を含むゲート電極17とゲート電極17を覆うゲート側壁絶縁膜20とを有する複数のゲート電極構造体を形成する工程と、ゲート電極構造体を覆って全面にポリシリコン膜を堆積する工程と、ポリシリコン膜をパターニングし、隣接する2つのゲート電極構造体の間でシリコン基板11に接続するコンタクトパッド22を形成する工程(図3(g))と、ゲート側壁絶縁膜のくぼみ21に残留するポリシリコン24を酸化させて酸化シリコン25に形成する工程(図3(h))とをこの順に有する。

(もっと読む)

応力が加えられたゲート金属シリサイド層を含む高性能MOSFET及びその製造方法

【課題】 応力が加えられたゲート金属シリサイド層を含む高性能の金属酸化物半導体電界効果トランジスタ(MOSFET)及び高性能MOSFETを製造する方法を提供すること。

【解決手段】 本発明は、ソース領域、ドレイン領域、チャネル領域、ゲート誘電体層、ゲート電極及び1つ又は複数のゲート側壁スペーサを備えた少なくとも1つの電界効果トランジスタ(FET)を含む半導体デバイスに関する。このようなFETのゲート電極は、1つ又は複数のゲート側壁スペーサによって横方向に制限され、かつ、FETのチャネル領域内に応力を生じさせるように配置され構成される内因性応力が加えられたゲート金属シリサイド層を含む。半導体デバイスは、少なくとも1つのp−FETを含むことが好ましく、p−チャネルFETは、1つ又は複数のゲート側壁スペーサによって横方向に制限され、かつ、FETのp−チャネル内に圧縮応力を生じさせるように配置され構成される内因性応力が加えられたゲート金属シリサイド層を備えたゲート電極を有することがより好ましい。

(もっと読む)

半導体金属合金への完全変換により得られる金属ゲートMOSFET及びその製造方法

【課題】 MOSFET構造及びその製造方法を提供する。

【解決手段】 本方法は、第一MOSFET型領域(40)では半導体層(22)を完全に半導体金属合金に変換するのに十分な厚さで、第二MOSFET型領域(30)では半導体層(20)を部分的に半導体金属合金に変換するのに十分な厚さで金属含有層(56)を形成する。第一の実施態様では、第一MOSFET型領域(40)のゲートスタックは金属含有層(56)を形成する前に凹化しておくので第一MOSFET半導体スタックの高さは第二MOSFET半導体スタックの高さ未満である。もう一つの実施態様では、変換プロセスの前に第一MOSFET領域(40)よりも第二MOSFET領域(30)の金属含有層(56)を薄く形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極にシリサイドを使用し、ゲート絶縁膜に高誘電率ゲート絶縁膜を使用する半導体装置において、高誘電率ゲート絶縁膜近傍やゲートエッジに高誘電率ゲート絶縁膜/シリコン界面が生じない半導体装置の製造方法を得ること。

【解決手段】基板上にゲート絶縁膜と多結晶シリコン膜の積層体を形成する工程と、積層体の側壁に第1のサイドウォールを形成する工程と、第1のサイドウォールの周囲に第2のサイドウォールを形成する工程と、積層体の下方のチャネル領域を挟んだ領域にソース/ドレイン領域を形成する工程と、第1のサイドウォールを除去して、積層体と第2のサイドウォールとの間に空隙を生成する工程と、多結晶シリコン膜をシリサイド化させるための金属膜を、空隙を満たすように基板上に形成し、該金属膜を多結晶シリコン膜に拡散させて、多結晶シリコン膜全体をシリサイド膜にする工程と、を含む。

(もっと読む)

垂直方向のドーパントプロファイルを適応的に変更することによってシリサイド不均一性を低減するための技法

深いドレイン領域及びソース領域内の垂直方向のドーパント濃度を変更することによって、金属シリサイド領域(217)の形成中の反応作用を制御することができる。この目的を果たすために、金属シリサイド界面のための目標深さ(Xs)の周囲に、増加したドーパント濃度が形成され、それにより反応速度が減速し、結果として生成される金属シリサイド界面の均一性が改善される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 IGFETの微細化を実現することができ、かつIGFETの動作速度の高速化を実現することができる半導体装置を提供する。

【解決手段】 半導体装置1において、半導体活性領域3と、半導体活性領域3に配設されたIGFET4と、半導体活性領域3の側面周囲を取り囲み、IGFET4のチャネル形成領域5に接する側面部分10Cの誘電率kが、中央部分10B及び底面部分10Dの誘電率kに比べて低い素子間分離領域10とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜のリーク電流の発生やゲート酸化膜の耐電圧性の低下を抑制するこ

とができる、信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体シリコン基板と前記半導体シリコン基板上にゲート酸化膜を介して設

けられたゲート配線と、を備えた半導体装置であって、

前記ゲート配線は、ゲート電極、前記ゲート電極に接して設けられたゲート配線上部構

造、ならびに側壁スペーサを有し、

前記側壁スペーサは一種もしくは二種以上の無機化合物絶縁層からなり、

かつ、前記無機化合物絶縁層の少なくとも一種は、窒素含有率が30〜70%の範囲で

あるシリコンオキシナイトライドからなることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート電極の高さが低くなっても、ゲート電極とソース・ドレイン領域間の短絡の防止を図ることができるように改良された半導体装置の製造方法を提供することを主要な目的とする。

【解決手段】 半導体基板1の上に、ゲート絶縁膜3を介在させて、その上面に第1の絶縁層5が形成されたゲート電極10を形成する。ゲート電極10の側壁および第1の絶縁層5の上面を被覆するように、半導体基板1の上に第2の絶縁層7を形成する。第2の絶縁層7をエッチングバックし、ゲート電極10の側壁にサイドウォールスペーサ11を形成するとともに、素子領域の表面を露出させる。第1の絶縁層5をゲート電極10の上面から除去する。ゲート電極10の上面およびソース・ドレイン領域1bの表面を被覆するように、半導体基板1の表面に高融点金属膜8を形成し、その後アニールし、ゲート電極10の上面およびソース・ドレイン領域1bの表面をシリサイド化し、シリサイド化層9を形成する。

(もっと読む)

半導体装置

【課題】 ショットキー型電界効果トランジスターに於いて、殊にソース領域近傍のチャネル領域に対するゲート電極の制御性を高めて、素子の電流駆動能力の向上を図る。

【解決手段】 ゲート絶縁膜を異なる誘電率を持つ膜の積層とすることで、誘電率の高い材料のみで形成した場合と比べてゲート絶縁膜の幾何学的な意味の厚さを薄く形成することを可能とし、ゲート電極から出た電気力線のゲート絶縁膜の側面から外への漏れに起因する、殊にソース領域近傍のチャネル領域の電位に対するゲート電極の制御性の低下を抑制する事が可能となる。また、誘電率の高い材料よりなるゲート側壁絶縁膜12を設ける事に依り、異なる誘電率を持つ物質の界面に於ける電気力線の屈折に依って、ゲート電極から出た電気力線をソース領域近傍のチャネル領域に集める事が可能となり、ソース領域とチャネル領域との間に形成されるショットキー障壁を薄くし、その抵抗を低減する。

(もっと読む)

非対称リセスされたゲートを有する金属酸化膜半導体電界効果トランジスタ及びその製造方法

【課題】DRAMなどの半導体素子のリセスゲート構造においてゲートとソース/ドレーン領域との間のオーバーラップによる非正常的な漏洩電流を減らすことができる非対称リセスされたゲートを有するMOSFET及びその製造方法を提供する。

【解決手段】リセスされたゲートを有するMOSFETは、半導体基板の所定深さに形成されたリセス領域と、前記リセス領域をギャップ充填して前記半導体基板に所定高さに形成され、前記ソース/ドレーン領域の中でいずれかの領域に対応するリセス領域とミスアラインされてリセスされたゲート電極と、前記リセスされたゲート電極の側面に形成されたスペーサーと、前記スペーサーにより露出した前記半導体基板内にドーパント注入されたソース/ドレーン領域とを含む。

(もっと読む)

MOS型半導体装置の製法

【課題】ドレイン側のポケット領域とLDD領域との間のオフセット距離のばらつきを低減できるMOS型半導体装置の製法を提供する。

【解決手段】半導体基板10の表面に形成したフィールド絶縁膜12の素子孔内にゲート絶縁膜14を形成した後、絶縁膜14及び12の上にドープトポリシリコン等からなるゲート電極層16及びキャパシタ用電極層18をそれぞれ形成する。絶縁膜12及び電極層16をマスクとするイオン注入処理によりポケット領域20,22を形成した後、電極層16,18を覆ってキャパシタ用絶縁層26をCVD法等により形成する。絶縁層26を介してのイオン注入処理により低濃度ソース、ドレイン領域28,30を形成する。ポケット領域22とLDD領域30との間のオフセット距離Lは、絶縁層26の厚さに対応して精度良く決定される。サイドスペーサ形成処理の後、高濃度ソース,ドレイン領域を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体措置で発生した熱を放熱しやすくすることによってESD耐圧に優れた半導体装置およびその製造方法を提供する。

【解決手段】 拡散層領域3に形成されたチャネル11の上には、ゲート絶縁膜7を介してゲート電極8が設けられている。また、ゲート電極8の側壁部には、サイドウォール9が形成されている。そして、ゲート電極8上とソース・ドレイン領域5上の一部とに、ゲート電極8およびサイドウォール9を被覆するようにしてシリサイドプロテクション膜10が形成されている。シリサイドプロテクション膜10が設けられていないソース・ドレイン領域の上には、シリサイドプロテクション膜10に隣接して金属シリサイド膜6が形成されている。ここで、シリサイドプロテクション膜10は、SiC膜およびSiOC膜の少なくとも一方からなるものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】 高誘電体材料からなるゲート絶縁膜上に金属材料からなるゲート電極を形成するnチャネル型MISトランジスタおよびpチャネル型MISトランジスタによってCMOS回路を構成する半導体装置の製造工程を簡略化する。

【解決手段】 酸化ハフニウム膜からなるゲート絶縁膜上に堆積したプラチナ膜をパターニングすることによって、nチャネル型MISトランジスタおよびpチャネル型MISトランジスタのゲート電極を同時に形成した後、プラチナ膜の還元触媒効果を利用してnチャネル型MISトランジスタ側のゲート絶縁膜のみを選択的に還元することにより、nチャネル型MISトランジスタのゲート電極の仕事関数を変動させる。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイド技術を用いた半導体装置では、低コストかつ短工程でMIS型トランジスタのゲート電極と拡散領域との短絡を防ぐことが困難であった。

【解決手段】ゲート部とソース・ドレイン部とを有する半導体素子であって、ゲート部は、ゲート電極の側部にサイドウォールを備える。サイドウォールの上端部がゲート電極の上端部よりも高く形成しており、サイドウォールのゲート電極に接する面は、ゲート電極上面に対してほぼ直角である。サリサイド技術を用いても、ゲート電極上に形成されたチタンと、サイドウォールおよびソース・ドレイン部上に形成されたチタンとは離間した状態となっており、シリサイドによるゲート電極とその他の部分との短絡を防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】 電気的特性に優れた半導体装置を提供する。また、低温でゲートリーク電流量を小さくすることのできる半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1の上には、第1の絶縁膜5と、窒素を含む第2の絶縁膜6とからなるゲート絶縁膜が形成されている。また、ゲート絶縁膜の上にはゲート電極8が形成されている。そして、ゲート絶縁膜およびゲート電極8の側壁部には、第2の絶縁膜6に含まれる窒素濃度よりも高濃度の窒素を含むシリコン酸窒化膜11が形成されており、第2の絶縁膜6とシリコン酸窒化膜11が接触するゲート電極8の下端部付近での窒素濃度は周囲の窒素濃度よりも高くなっている。第2の絶縁膜6は5atm%〜20atm%の濃度の窒素を含むことが好ましく、シリコン酸窒化膜11は、第2の絶縁膜6に含まれる窒素濃度の1.1倍〜2.0倍の窒素を含むことが好ましい。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

不透明なゲート層の位置合わせ用マーカ、このようなマーカの製作方法、及びリソグラフィ機器でのこのようなマーカの使用

【課題】順に繰り返して配置されたライン要素及びトレンチ要素を含むマーカ構造を製作する方法を提供すること。

【解決手段】この方法は、トレンチ要素に二酸化シリコンを充填し、マーカ構造を平坦化するステップを含む。半導体表面上で犠牲酸化物層を成長させ、ライン要素の第1サブセットを、ドーパント種を含むイオン注入ビームに露出させて、この第1サブセットをドープし、そのエッチング速度を変化させる。この基板をアニールしてドーパント種を活性化させ、半導体表面をエッチングして犠牲酸化物層を取り除き、第1サブセットを第1レベルの高さにし、第1サブセットが、第1サブセットと異なるマーカ構造表面部分の第2レベルと異なる第1レベルを有するようにトポロジーを生成する。

(もっと読む)

サイドウォールスペーサの形成方法

本発明により、基板(201)上のフィーチャ(206)に隣接するサイドウォールスペーサ(217、218)を形成することができる。フィーチャ(206)は1つ以上の保護層(220、207)に覆われる。スペーサ材料層(211)はフィーチャ(206)上に蒸着され、異方性エッチングされる。異方性エッチングに使用されるエッチング液はスペーサ材料を選択的に除去することに適しており、一方で1つ以上の保護層(220、207)はこのエッチング液による影響を実質的に受けない。その結果、1つ以上の層(220、207)はフィーチャがエッチング液にさらされるのを保護する。  (もっと読む)

(もっと読む)

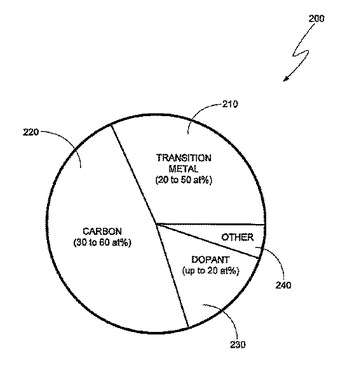

ゲート電極として使用される遷移金属合金およびこれらの合金を取り入れた装置

高温で顕著に変化しないn型またはp型の仕事関数を有する遷移金属合金の実施例を示した。示された遷移金属合金は、トランジスタのゲート電極として使用しても良く、ゲート電極の一部を構成しても良い。これらの遷移金属合金を用いて、ゲート電極を形成する方法についても示した。  (もっと読む)

(もっと読む)

41 - 60 / 60

[ Back to top ]