Fターム[5F140BG19]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | イオン注入時ゲート保護層(最外レジストを除く) (497) | ゲート保護材料(ゲート電極以外) (478)

Fターム[5F140BG19]の下位に属するFターム

Fターム[5F140BG19]に分類される特許

21 - 40 / 60

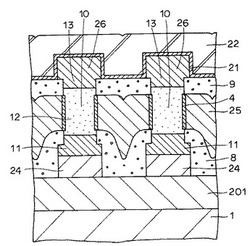

半導体装置

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になる第1の導電層6の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】酸化シリコン膜のエッチングに対するエッチング耐性を有する応力膜を形成することで、応力膜の上記エッチング時の膜減りを低減することを可能にする。

【解決手段】半導体基板11上にゲート電極形成溝23が形成されたサイドウォール絶縁膜21と、ゲート電極形成溝23内の半導体基板11上にゲート絶縁膜24を介して形成されたゲート電極25と、ゲート電極25の側壁にサイドウォール絶縁膜24を介して半導体基板11上に形成されていて応力を有する第1応力膜51と、第1応力膜51の外側の半導体基板11上に形成されていて第1応力膜51と同種の応力を有する第2応力膜52とを有し、第1応力膜51および第2応力膜52は酸化シリコン膜をエッチングするときのエッチング種に対するエッチング耐性を有し、第1応力膜51は第2応力膜52よりも前記エッチング種に対するエッチング耐性が強いことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜とゲート電極を工夫することにより、ゲート空乏化を抑制しつつ実効仕事関数を制御することを可能とする。

【解決手段】P型の絶縁ゲート型電界効果トランジスタの第1トランジスタ2と、N型の絶縁ゲート型電界効果トランジスタの第2トランジスタ3とを有し、前記第1トランジスタ2のゲート絶縁膜21と前記第2トランジスタ3のゲート絶縁膜21は、前記ゲート電極側に金属不純物22が存在していて、前記第1トランジスタ2のゲート電極23NがN型のポリシリコンである、もしくは前記第2トランジスタ3のゲート電極23PがP型のポリシリコンである、もしくは前記第1トランジスタ2のゲート電極23NがP型のポリシリコンであり前記第2トランジスタ3のゲート電極23PがP型のポリシリコンであることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 大幅なプロセスコスト増を伴うことなく、チャネルに歪を発生させることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の一部の表面上に、半導体膜と、該半導体膜よりも密度の高いブロック膜とがこの順番に積層されたゲートパターンを形成する。(b)ゲートパターンをマスクとして、半導体基板の表層部に、ソース及びドレイン用の不純物を注入する。(c)ゲートパターンをマスクとして、半導体基板内に、ソース及びドレイン用の不純物とは異なる歪形成用の不純物を注入する。(d)半導体基板を熱処理し、歪形成用の不純物が注入された領域を再結晶化させる。

(もっと読む)

MOSトランジスタの製造方法、および、これにより製造されたMOSトランジスタ

【課題】MOSトランジスタの製造方法、およびこれにより製造されたMOSトランジスタを提供する。

【解決手段】半導体基板100上にゲートパターン120を形成する工程と、前記ゲートパターンの側壁を覆うスペーサ134を形成する工程と、を含み、前記ゲートパターンを形成する工程は、順に積層されるゲート電極112a、キャッピング膜パターン118、を備えるように形成し、前記キャッピング膜パターンは、順に積層される下部キャッピング膜パターン114b、上部キャッピング膜パターン116a、を備えるように形成し、前記下部キャッピング膜パターンは前記上部キャッピング膜パターンよりも小さい幅を有するように形成する、ことを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 p型チャネルを有する半導体装置において、前記p型チャネル領域に一軸性圧縮応力をSiGe混晶層より印加して、前記チャネル領域におけるホール移動度を向上させる。

【解決手段】 シリコン基板中、ソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層によりエピタキシャルに充填する際に、前記トレンチの側壁面を複数のファセットにより画成し、さらにSiGe混晶層中のGe原子濃度を20%を超えて増大させる。

(もっと読む)

半導体装置およびその製造方法

【課題】 p型チャネルを有する半導体装置において、前記p型チャネル領域に一軸性圧縮応力をSiGe混晶層より印加して、前記チャネル領域におけるホール移動度を向上させる。

【解決手段】 シリコン基板中、ソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層によりエピタキシャルに充填する際に、前記トレンチの側壁面を複数のファセットにより画成し、さらにSiGe混晶層中のGe原子濃度を20%を超えて増大させる。

(もっと読む)

トランジスタのゲート電極のプレアモルファス化のブロッキング

トランジスタのソース/ドレイン領域を選択的にプレアモルファス化する一方で、トランジスタのゲート電極はプレアモルファス化しない技術が提供される。例示的実施形態においては、ゲート電極にわたってプレアモルファス化注入ブロッキング材料が形成される。更に例示的実施形態においては、各種ストレッサを用いてチャネル領域に歪みが誘発される。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】高耐圧MISFETを有する半導体集積回路装置の寄生MOSの閾値電位を上げることができる技術を提供する。

【解決手段】高耐圧MISFET形成領域HN、HPのフィールド酸化膜4上に酸化シリコン膜5cを形成する。その結果、このフィールド酸化膜4上に形成される寄生MOSの閾値電位を上げることができる。また、高耐圧MISFETのゲート電極FG上に低耐圧MIFETのゲート電極となる多結晶シリコン膜111が形成された状態で、低耐圧MISFETの閾値調整用の不純物注入を行う。その結果、前記不純物は、高耐圧MISFETゲート電極FG内に留まり、NBT現象の発生を抑制することができる。

(もっと読む)

CMOS半導体素子及びその製造方法

【課題】デュアルメタルゲートCMOS半導体素子を提供する。

【解決手段】金属窒化物層及び多結晶シリコンキャッピング層を備え、nMOS領域及びpMOS領域の金属窒化物層は同種物質で形成され、相異なる不純物含有量により相異なる仕事関数を持つデュアルメタルゲートCMOS半導体素子。同種の金属窒化物層によりメタルゲートを形成するので、工程が単純化して収率が向上すると共に、高性能のCMOS半導体素子を得ることができる。

(もっと読む)

引張歪みおよび圧縮歪みを生成するための埋め込みSi/Ge材料を含むNMOSトランジスタおよびPMOSトランジスタを有する半導体デバイス

1つの能動領域(105A,205A,305A,405A)に、実質的に連続し、かつ均一な半導体合金(107,207,307,407)を形成する一方で、第2能動領域(105B,205B,305B,405B)の中央部分にベースの半導体材料(113B,213B,313B、401)を提供するために、そこに半導体合金(107,207,307,407)をパターニングすることにより、異種の歪みが誘発されうる。一方、前記ベースの半導体材料(113A,213A,313A,413A)に対応するカバー層を提供した後に、前記ゲート誘電体(122,322,422)を形成するための確立されたプロセス技術が使用されうる。一部の例示的な実施形態では、実質的な自己整合プロセスが提供される。このプロセスでは、前記層(208,308)を基に前記ゲート電極(121,221,321,421)が形成され、前記層(208,308)は、前記能動領域(205B、305B)の一方の前記ベースの半導体材料の前記中央部分(213B、313B)を画定するためも使用されうる。このため、単一の半導体合金(107,207,307,407)を使用することにより、異なる導電型のトランジスタ(120A,120B)の性能が個別に改善されうる。  (もっと読む)

(もっと読む)

高耐圧トランジスタ、これを用いた半導体装置及び高耐圧トランジスタの製造方法

【課題】サージ電圧/電流によってゲート酸化膜が破壊されることを防止する。

【解決手段】高耐圧トランジスタは、半導体基板8に形成されたトレンチに設けられたゲート電極4と、ゲート電極4の両側に、ゲート電極4からそれぞれ所定の間隔を空けて形成されたソース5及びドレイン6と、トレンチのソース5側の側壁とトレンチのドレイン6側の側壁とに沿って形成された電界緩和層2と、ゲート電極4とソース5との間と、ゲート電極4とドレイン6との間とに形成された電界緩和層3とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の微細化に伴うトランジスタのショートチャネル対策として、トレンチゲートTrが開発されている。しかしながら、トレンチゲートTrはゲート電極と基板間の対向面積が増加するため、ゲート電極の寄生容量が大きくなるという問題がある。

【解決手段】 本発明のトレンチゲートTrは、溝の内部に第1のゲート電極と第2のゲート電極とを備えている。Trのチャネルとなる溝下部には、基板との間にゲート酸化膜を介した第1のゲート電極を備える。Trの不純物拡散層と対向する溝部上部には、ゲート酸化膜と溝サイドウォール膜とを介した第2のゲート電極を備える。溝部上部のゲート電極と基板間をゲート酸化膜と溝サイドウォールとの複合膜とすることでゲート電極の寄生容量を小さくできる。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧トランジスタと低電圧駆動トランジスタとが同一の半導体基板に形成された半導体装置において、素子パターンの微細化が進行した場合であっても耐圧低下を生じることなく安定して製造することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上にゲート酸化膜3、4を介して導電膜5と絶縁膜6とが順次形成される。レジストパターン7をマスクとして絶縁膜6および導電膜5が順次エッチングされ、パターニングされた絶縁膜8および高耐圧トランジスタのゲート電極9の積層体が形成される。その積層体をマスクとして半導体基板1と逆導電型の不純物が注入される。

(もっと読む)

半導体装置の製造方法

【課題】 近年の半導体デバイスの微細化に伴って、コンタクトホール開口後に投影飛程距離が浅いイオンを注入し、ソース・ドレイン部のコンタクト抵抗を低下させることが行われている。しかし、このコンタクト抵抗を下げるためのイオン注入により,その飛程位置を中心として格子歪みや欠陥が残留し、欠陥と空乏層とが接触し接合リークが発生するという問題がある。

【解決手段】 本発明の半導体装置の製造方法は、コンタクトホール形成後に直列抵抗を下げるための砒素注入を行い,その後,コンタクトホール側壁部にサイドウォール膜を形成する。このサイドウォール膜をマスクとしてシリコンをエッチングすることにより,このサイドウォール直下の砒素領域を残しつつ,砒素の投影飛程位置を中心とした注入ダメージの多い領域を除去する。注入ダメージの多い2次欠陥領域を除去することで接合リーク電流の発生を防止できる効果がある。

(もっと読む)

不純物ドーピング領域を含む半導体素子及びその形成方法

【課題】高集積化に最適化された、不純物ドーピング領域を含む半導体素子及びその形成方法を提供する。

【解決手段】この方法は、半導体基板にクラスタ型ドーパントイオンを注入して不純物注入領域を形成する段階(S200)と、前記不純物注入領域にレーザアニーリング工程を実行して不純物ドーピング領域を形成する段階(S210)とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長が異なっていても、均一な金属組成比のフルシリサイドゲート電極を備え、かつその金属組成比を容易に制御できる半導体装置及びその製造方法を提供する。

【解決手段】異なるゲート長のポリシリコンゲート電極9,29において、その上端の高さを等しく、かつサイドウオール20よりも低く形成する。そして、ポリシリコンゲート電極9,29を覆うように金属膜8を形成後、熱処理によりシリサイド化する。ポリシリコンゲート電極21の上端の高さが、サイドウオール20の上端の高さよりも低く形成されているので、微細なゲート長であってもシリサイド反応が加速されることなく、一次元的に進む。その結果、ゲート長が異なるポリシリコンゲート電極9,29でも、均一な金属組成比のフルシリサイドゲート電極を安定して形成できる。

(もっと読む)

成膜方法および半導体装置の製造方法

【課題】大気圧でエピタキシャル成長を行うことで、成長速度を低下させることなくヒ素を高濃度にドーピングしたシリコンエピタキシャル成長層を形成することを可能とする。

【解決手段】エピタキシャル成長によりヒ素をドーピングしたシリコン層(シリコンエピタキシャル成長層22)を形成する成膜方法であって、前記エピタキシャル成長雰囲気13を大気圧として前記エピタキシャル成長雰囲気13中にドーピング物質のヒ素を含むガスを供給することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲートとソース・ドレイン拡散層との間にオフセット距離を設けつつ、ソース・ドレイン拡散層とチャネル反転層との離間に起因する寄生容量の増大を回避し得る半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、素子分離された半導体基板上にゲート絶縁膜を形成し、ゲート絶縁膜を介して半導体基板上にゲート下部層材を堆積し、ゲート下部層材上に、ゲート下部層材と異なる材料からなるゲート上部層材を堆積し、ゲート上部層材及びゲート下部層材を選択的に加工することによりゲート上部層及びゲート下部層からなるゲートを形成し、ゲート上部層及びゲート下部層のうちゲート上部層の方が反応速度が大きい化学反応加工処理を行って、半導体基板に対して水平方向におけるゲート上部層の寸法を増加させ、ゲート上部層をマスクとして半導体基板にイオン注入を行って不純物注入領域を形成し、熱拡散処理を行って不純物注入領域からソース・ドレイン拡散層を形成することを含む。

(もっと読む)

半導体装置

【課題】High-k絶縁膜をゲート絶縁膜として使用する電界効果トランジスタを含む半導体装置であって、メタルゲート電極化を行わずに、フェルミレベルピニングに起因するしきい値電圧固定を抑制可能な半導体装置を実現する。

【解決手段】Pチャネル型電界効果トランジスタ4において、High-k絶縁膜たる金属酸化物(好ましくは、ハフニウム酸化物(HfO2やHfSiON、HfSiO4など)またはジルコニウム酸化物(ZrO2やZrSiON、ZrSiO4など))を有するゲート絶縁膜6bと、ポリシリコンゲート電極7との間に窒化チタン(TiN)膜8を形成する。窒化チタン膜は、金属酸化物を有するゲート絶縁膜に接して形成されてもフェルミレベルピニングが起きない。また、ポリシリコンゲート電極の下部が窒化チタン膜との金属膜となっているので、ゲートの空乏化が抑止でき、電流駆動能力向上も図れる。

(もっと読む)

21 - 40 / 60

[ Back to top ]