Fターム[5F140BH42]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | SD近傍領域(SD領域と導電型は除く) (1,891) | 不純物分布 (48)

Fターム[5F140BH42]に分類される特許

1 - 20 / 48

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

半導体装置

【課題】アバランシェ降伏電流が流れている状態において寄生トランジスタのターンオンを抑制することにより、十分なアバランシェ耐量を確保することのできる半導体装置を提供する。

【解決手段】基板の表面ではn型領域とベース領域とが隣接している。エミッタ/ソース領域はベース領域内でn型領域から離れている。ゲート絶縁膜はn型領域とエミッタ/ソース領域との間でベース領域を覆い、その上にゲート電極が形成されている。ドレイン領域とコレクタ領域とはn型領域内でベース領域から離れている。コレクタ接続領域はn型領域内で、ベース領域、ドレイン領域、及びコレクタ領域のいずれからも離れている。ドレイン電極はドレイン領域に接続されている。コレクタ電極はコレクタ領域とコレクタ接続領域とに接続されている。ゲートターンオフ状態でドレイン電極にアバランシェ降伏電流が流れるとき、コレクタ電極の電位がドレイン電極の電位よりも低い。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】 ファセット起因による短チャネル効果を回避すること。

【解決手段】 半導体基板(1)に設けられたMISトランジスタ(4,5,13)からなる半導体デバイス(200)は、半導体基板(1)に設けられた素子分離領域(2)と、素子分離領域(2)によって区画された活性領域(3)と、活性領域(3)に設けられたMISトランジスタのチャネル領域よりも上方へ突出したMISトランジスタのソース/ドレイン領域(13)と、ソース/ドレイン領域(13)の下方に設けられた拡散層(12)と、を備える。ソース/ドレイン領域(13)の導電型に対する拡散層(12)の導電型が逆の極性となっている。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】3次元形の半導体素子において、オン抵抗をより効果的に低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、ドレイン層と、ドレイン層内に選択的に設けられたドリフト領域と、ドリフト領域内に選択的に設けられたベース領域と、ベース領域内に選択的に設けられたソース領域と、ソース領域又はドレイン層の少なくとも一方の内部に、ソース領域又はドレイン層の少なくとも一方に選択的に設けられた第1,第2の金属層と、ドレイン層の表面に対して略平行な方向に、ソース領域の一部から、ソース領域の少なくとも一部に隣接するベース領域を貫通して、ドリフト領域の一部にまで到達するトレンチ状のゲート電極と、第1の金属層に接続されたソース電極と、ドレイン層又は第2の金属層に接続されたドレイン電極と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタにおいて、ホットエレクトロンのゲート絶縁膜へのトラップによるトランジスタ特性の経時劣化を減少させる。

【解決手段】N−−型の半導体層12の表面にボディ層19が配置されている。ボディ層19の表面にはN−型層23を含むソース層が配置されている。N−−型の半導体層12の表面には、N−型のドリフト層21が形成されている。このドリフト層21は、N型不純物濃度のピーク領域P1を有した第1の領域21Aと、この第1の領域21Aに隣接し、N型不純物濃度のピーク領域P1よりも深い位置にN型不純物濃度のピーク領域P2を有した第2の領域21Bとにより構成されている。第2の領域21Bの表面にはN+型のドレイン層25が形成されている。

(もっと読む)

半導体装置および集積回路

【課題】ドレイン端での局所的な電流集中を防止して静電放電に対する耐性を向上させる。

【解決手段】N型高濃度埋め込み領域102の上面にN型低濃度領域103とN型ウエル領域104とN型高濃度埋め込みコンタクト領域105を順次隣接して配置し、N型低濃度領域103の上面にP型低濃度領域106を配置し、ドレイン電極113Dが接続される第1のN型高濃度領域107をN型高濃度埋め込みコンタクト領域105の上面に配置し、ソース電極113Sが接続される第2のN型高濃度領域108とP型高濃度領域109をP型低濃度領域106の上面にチャネル幅方向に並べて配置し、第1のN型高濃度領域107からN型ウエル領域104の上面を経由しP型低濃度領域106の上面に向けて素子分離領域110を配置し、P型低濃度領域106の上面に位置する箇所の上面にゲート酸化膜を介してゲート電極111を配置し、P型低濃度領域106のうちのゲート電極111の下部にチャネルが形成されるようにした。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路(1000)が、中央配置のドレイン拡散領域(1008)及び分散型SCR端子(1010)を備える1つのドレイン構造(1006)と、分散型ドレイン拡散領域(1016)及びSCR端子(1018)を備える別のドレイン構造(1012)とを含むSCRMOSトランジスタを有する。中央配置のドレイン拡散領域とソース拡散領域との間のMOSゲート(1022)がソース拡散領域へ短絡される。SCRMOSトランジスタを有する集積回路を形成するためのプロセスも開示される。  (もっと読む)

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

誘電体分離型半導体装置

【課題】高耐圧かつ、電流駆動能力が高く、かつ電流集中による素子破壊の起こりにくい誘電体分離型半導体装置を提供する。

【解決手段】半導体支持基板の上に、絶縁された第一導電型の半導体領域とを有する誘電分離基板に形成した誘電体分離型半導体装置において、第一導電型の半導体領域と絶縁分離領域の間と、前記第1導電型の半導体領域の基板表面側と、に形成されたドレイン領域と、第一導電型のソースと第二導電型の半導体領域のチャネルからなる複数個の単位ソース領域と、第一導電型の半導体領域の基板表面側に形成されたドレイン領域と前記複数個の単位ソース領域の間を制御する複数個のゲート電極とを、備え、隣接する前記単位ソース領域間に絶縁分離領域が、基板底面側から基板表面側に向けて突き出した形状とされ、この絶縁分離領域上の素子表面領域が前記第一導電型の半導体領域より抵抗値が高い。

(もっと読む)

半導体装置及びその製造方法

【課題】 低いオン抵抗を維持しつつ、従来構成よりも更に耐圧低下を抑制したLDMOSトランジスタ及びその製造方法を提供する。

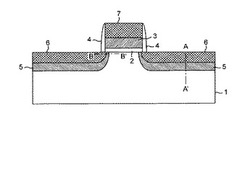

【解決手段】 P型基板1上に形成された、N型ウェル2と、ウェル2内に形成されたP型ボディ領域6と、ウェル2内においてボディ領域6よりも深い位置に形成されたP型の埋め込み拡散領域4と、ボディ領域6内に形成されたN型のソース領域9と、ウェル2内において、素子分離領域を介してボディ領域6と離間して形成したN型のドリフト領域7と、ドリフト領域7内に形成されたN型のドレイン領域10と、少なくとも前記ボディ領域9の一部上方、及びボディ領域9とドレイン領域10に挟まれた位置におけるウェル領域2の上方にわたってゲート絶縁膜を介して形成されたゲート電極7と、有し、ドリフト領域7並びにドレイン領域10が、ボディ領域6を取り囲むようにリング状に形成されている。

(もっと読む)

ソース/ドレインゾーンに沿って調節したポケット部分を具備する非対称的電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられている非対称的絶縁ゲート電界効果トランジスタ(100U又は102U)は、該トランジスタボディ物質のチャンネルゾーン(244又は284)によって横方向に分離された第1及び第2ソース/ドレインゾーン(240及び242又は280及び282)を包含している。

【解決手段】 ゲート電極(262又は302)がチャンネルゾーン上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の横方向に隣接した物質よりも一層高度にドープした該ボディ物質のポケット部分(250又は290)が該S/Dゾーンの内のほぼ第1のもののみに沿って該チャンネルゾーン内に延在している。該ポケット部分の垂直ドーパント分布は、互いに離隔されている夫々の位置(PH−1乃至PH−3)において複数個の局所的最大(316−1乃至316−3)に到達すべく調節されている。該調節は、典型的に、該ポケット部分の垂直方向ドーパント分布が上部半導体表面近くで比較的平坦であるように実施される。その結果、該トランジスタのリーク電流は減少されている。

(もっと読む)

L形状スペーサを使用した非対称的電界効果トランジスタの製造及び構成体

【課題】 非対称的電界効果トランジスタ(102)の製造は、半導体ボディのボディ物質のチャンネルゾーン(284)の上方でそれからゲート誘電体層(300)によって垂直方向に分離されているゲート電極(302)を画定することとなる。

【解決手段】 該ゲート電極をドーパント阻止用シールドとして使用して、半導体ドーパントを該ボディ物質内に導入させて、一層高度にドープしたポケット部分(290)を画定する。該ゲート電極に沿ってスペーサ(304T)を設ける。該スペーサは、(i)該ゲート電極に沿って位置されている誘電体部分、(ii)該半導体ボディに沿って位置されている誘電体部分、及び(iii)該他の2つのスペーサ部分の間の空間をほぼ占有するフィラー部分(SC)、を包含している。該ゲート電極及び該スペーサをドーパント阻止用シールドとして使用して、半導体ドーパントを該半導体ボディ内に導入させて、一対のソース/ドレイン部分(280M及び282M)を画定する。該フィラースペーサ部分を除去して該スペーサをL形状(304)へ変換させる。一対の電気的コンタクト(310及び312)を夫々該主要ソース/ドレイン部分に対して形成する。

(もっと読む)

MISトランジスタ

【課題】ゲート電極とソース/ドレイン電極間で電気的短絡を起こし難いMISトランジスタを得る。

【解決手段】サイドウォール15を二重構造とする。バッファ層13は窒化酸化シリコンで形成され、バッファ層13の上に窒化シリコン層14が形成される。このサイドウォール15をマスクとしてシリサイド膜10を形成する。バッファ層13は窒化酸化シリコンのみならず、酸化シリコンで形成されてもよい。シリサイド膜はコバルトシリサイドでも、ニッケルシリサイドでもよい。窒化シリコン層14はバッファ層13よりも大きい応力を持つ。

(もっと読む)

基板ドレイン接続を有する横型MOSFET

1つの形式として、横型MOSFETは、ソース領域とドレイン領域との間に横方向に配されているアクティブゲートを含み、当該ドレイン領域は、単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張し、横型MOSFETは、ドレイン領域の上に配されている非アクティブゲートをさらに含む。他の形式において、横型MOSFETは、ソース領域とドレイン領域との間に横方向に配されているゲートを含み、ドレイン領域は、単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張し、ソース領域及びドレイン領域は第1の導電タイプであって、横型MOSFETは、ソース領域に接しておりかつソース領域の下方にある第2の導電タイプのヘビーボディ領域をさらに含み、ドレイン領域は、ゲートのエッジに近接しているライトドープドレイン(LDD)領域及び単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張しているシンカーを含んでいる。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法、静電放電保護素子

【課題】製造効率を向上すると共に、内部回路の保護を的確に行うことが容易に可能な半導体装置、半導体装置の製造方法、静電放電保護素子を提供する。

【解決手段】半導体基板20に第1導電型の第1半導体領域21が形成され、その両側に第2導電型の第2及び第3半導体領域(22,23)が形成され、第1半導体領域の上方に絶縁膜を介してゲート電極32が形成され、第1半導体領域と第3半導体領域の接合面をまたいでそれらにかかるように第1導電型の第4半導体領域30が形成され、第2及び第3半導体領域にソース領域26とドレイン領域28が形成され、ゲート電極及びソース領域が接地され、内部回路に接続された入力パッド40がドレイン領域に接続され、入力パッドにサージ電圧が入力された際にドレイン領域と第4半導体領域との間でツェナー降伏が生じて寄生バイポーラトランジスタがオン状態となり、サージ電圧を放電する。

(もっと読む)

リサーフ構造を用いた電界効果トランジスタ

【課題】炭化珪素基板上に、高耐圧で低抵抗なMOS電界効果トランジスタを形成する。

【解決手段】第1の導電型を持つ炭化珪素半導体の活性層(1)と、該活性層の表面部分に形成された第2の導電型のソース領域(4)と、該ソース領域から間隔をおくように形成された第2の導電型のドリフト領域(2)と、該ドリフト領域の表面部分に形成された第1の導電型の電界緩和領域(6)と、第2の導電型のドレイン領域(3)と、ソース領域とドリフト領域とで挟まれた領域の上に形成されたゲート絶縁膜(11)及びゲート電極(12)と、を具備する。電界緩和領域(6)は、互いの投影方向においてゲート電極(12)と重なる部分を持ち、ドリフト領域上のゲート電極(12)の端点の位置(II)から電界緩和領域のドレイン側の端点(IV)までの長さは、電界緩和領域の該端点(IV)からドレイン領域の端点(I)までの長さよりも短い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

埋設導電層を備えた高電圧トランジスタ

【課題】埋設導通層を備えた低オン抵抗値の横方向高電圧FETを提供する。

【解決手段】P−型基板に形成されたN−ウエル内にP−型埋設層領域を設け、これをN−ウエル領域に形成された第1のP−型ドレイン拡散領域によってドレイン電極に接続すると共に、PMOSゲート領域の一端で表面から下方に延びる第2のP−型ドレイン拡散領域にも接続し、ソース電極に接続されるP−型ソース拡散領域でゲート領域の他端を定めるようにする。

(もっと読む)

トランジスタ型保護素子、半導体集積回路およびその製造方法

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、ゲート電極4、ソース領域5、ドレイン領域6および抵抗性降伏領域8を有する。抵抗性降伏領域8はドレイン領域6に接し、ゲート電極4直下のウェル部分と所定の距離だけ離れたN型半導体領域からなる。ドレイン領域6または抵抗性降伏領域8に接合降伏が発生するドレインバイアスの印加時に抵抗性降伏領域8に電気的中性領域(8i)が残るように、抵抗性降伏領域8の冶金学的接合形状と濃度プロファイルが決められている。

(もっと読む)

1 - 20 / 48

[ Back to top ]