Fターム[5F140CB03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 素子分離構造 (5,334) | チャネルストッパ (158) | 不純物分布 (19)

Fターム[5F140CB03]に分類される特許

1 - 19 / 19

化合物半導体装置の製造方法、基板評価装置及び基板評価方法

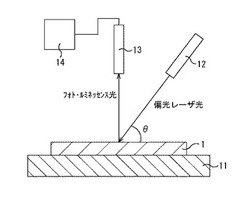

【課題】化合物半導体層を形成する前の基板の状態で非接触のスクリーニングを行うことで、事前に化合物半導体層の不良発生を認識してこれを防止することができ、歩留まりの向上及び製造コストの削減を可能とする信頼性の高い化合物半導体装置を得る。

【解決手段】偏光レーザ12によりSiC基板1の基板面に偏光レーザ光を照射し、検出部13によりSiC基板1からの発光を検出し、表示部14によりSiC基板1の発光強度の面内分布を得て、SiC基板1の窒素混入量を評価した後、SiC基板1の上方に化合物半導体積層構造2を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

半導体装置

【課題】オン抵抗の低減を実現できる、高耐圧のLDMOSトランジスタを有する半導体装置を提供する。

【解決手段】半導体基板上に配置された第2導電型の第1半導体領域と、第1半導体領域の上面の一部に埋め込まれた第1導電型の第2半導体領域と、第2半導体領域の上面の一部に埋め込まれた第2導電型のソース領域と、第2半導体領域と離間して第1半導体領域の上面の一部に埋め込まれた第2の導電型のドレイン領域と、ソース領域とドレイン領域間で第2半導体領域上に配置されたゲート電極と、第2半導体領域とドレイン領域間で第1半導体領域上に配置された絶縁膜と、絶縁膜上に配置されてゲート電極とドレイン領域間の電圧を分圧する分圧素子と、分圧素子とドレイン領域との間に接続された電荷移動制限素子とを備える。

(もっと読む)

横型素子を有する半導体装置

【課題】高速スイッチング動作を行う場合でも、アバランシェブレークダウンを抑制でき、スイッチング損失低減や素子破壊を抑制することが可能な構成とする。

【解決手段】横型FWD7などの横型素子において、SRFP21の全抵抗Rの抵抗値を90kΩ〜90MΩ、好ましくは270kΩ〜27MΩ、より好ましくは900kΩ〜9MΩとすることにより、2ndピーク時のアノード電流IAなどの電流が大きくなることを抑制できる。これにより、高速スイッチング動作を行う場合でもアバランシェブレークダウンを抑制でき、横型FWD7のスイッチング損失低減や素子破壊を抑制することが可能となる。

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

【課題】窒化ガリウム材料デバイスおよびその形成方法を提供する。

【解決手段】該デバイスは、電極規定層24を包含する。電極規定層は典型的にはその内部に形成されたビア26を有し、該ビア内に電極18が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。

(もっと読む)

半導体装置

【課題】チップの占有面積を有効に活用する。

【解決手段】P型半導体基板11上にN型エピタキシャル層12が形成され、LDMOSとJFETに共通なドレイン領域121を規定するP型素子分離領域13が形成される。ドレイン領域121内にボディ領域15が形成され、ボディ領域15内にN型ソース領域16が形成され、ドレイン領域121とソース領域16間のチャネル領域上にゲート電極20が配置され、LDMOSが形成される。ボディ領域15とP型素子分離領域13との間にJFETのソースとなるN型領域が形成される。ドレインに正のドレイン電圧が印加されると、PN接合が逆バイアスされ、ボディ領域15と分離領域13と半導体基板11とから空乏層が延び、JFETのチャネルを制御する。

(もっと読む)

半導体装置

【課題】高耐圧素子の耐圧の降伏が生じても、他の素子に生じるダメージを最小限に抑えることのできる半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置100は、第1導電型の半導体基板10と、半導体基板10に設けられた、第2導電型のウェル20と、ウェル20に設けられた、第1導電型の第1不純物領域30と、ウェル20に設けられ、かつ、第1不純物領域30の周囲に、第1不純物領域30と離間して設けられた第2導電型の第2不純物領域40と、ウェル20の周囲に設けられ、かつ、第2不純物領域40と離間して設けられた第1導電型の第3不純物領域50と、を有し、ウェル20は、第2不純物領域40よりも不純物濃度が小さく、かつ、第1不純物領域30、第2不純物領域40、および第3不純物領域50よりも半導体基板10の厚み方向に深く形成され、第1不純物領域30および第2不純物領域40の間の最小の間隔は、第2不純物領域40および第3不純物領域50の間の最小の間隔よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】素子領域を耐酸化膜で覆い、ドレイン領域をレジストマスクで覆ってイオン注入し、チャネルストッパ及び素子領域に低濃度チャネルストッパを形成すると、チャネル領域に低濃度チャネルストッパが形成され、しきい値のばらつきを生ずる。

【解決手段】ソース領域4を素子領域2より狭幅にする。そして、ドレイン領域3、チャネル領域35及びソース領域4を覆う凸字形パターンのレジストマスクを用いてイオン注入し、チャネルストッパ7を形成する。このとき、チャネルストッパ7とソース領域4の間に、チャネル35の中間地点(線分30)まで延在する低濃度チャネルストッパ8が形成される。このため、素子領域周辺に形成される寄生トランジスタのしきい値が高くなる。一方、残りのチャネル領域内には低濃度チャネルストッパが形成されないので、電界効果トランジスタのしきい値が安定する。

(もっと読む)

半導体装置

【課題】ドリフト領域に設けられたトレンチ内に抵抗性フィールドプレートを有し、トレンチ底部近傍の電界強度がトレンチ開口部近傍の電界強度に近く、高耐圧で駆動が可能であり、オン電圧の増加を抑制することができる安価な半導体装置を提供すること。

【解決手段】nドリフト領域3の表面層のpボディ領域4およびnバッファ領域7に挟まれた部分に設けられたトレンチ11に、酸化膜12を介して、抵抗性薄膜13が設けられている。この抵抗性薄膜13に、コレクタ(ドレイン)電極17と、ゲート電極16もしくはエミッタ(ソース)電極15と、を接続させることで抵抗性フィールドプレートとする。これによって、トレンチ11の開口部近傍の電界強度と、トレンチ11の底部近傍の電界強度と、がほぼ同等となるため、nドリフト領域3の電流経路が短くなり、デバイスを高耐圧で駆動する場合にも、オン電圧の増加を抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】化合物半導体領域の表面における化学的な安定性の向上と、絶縁膜自体の良好な絶縁性という、保護絶縁膜に求められる相反する要求を共に満たし、高性能で信頼性に優れた半導体装置を実現する。

【解決手段】化合物半導体領域2の表面を覆う保護絶縁膜10を性質の異なる第1の絶縁膜11と第2の絶縁膜12との2層構造を有するように形成する。第1の絶縁膜11は非ストイキオメトリのシリコン窒化膜、第2の絶縁膜12はほぼストイキオメトリの状態とされたシリコン窒化膜とする。

(もっと読む)

半導体装置

【課題】ゲート電極に電圧が印加されないときにも、ゲート電極とドレイン領域との間の電界を緩和し、ゲート絶縁膜に電界集中が発生するのを抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置100は、互いに所定の間隔を隔てて形成されたソース領域7およびドレイン領域9と、ソース領域7に接するように形成され、チャネル領域5aを含むボディ領域5と、電界緩和層3と、ボディ領域5と電界緩和層3との表面上に形成されたゲート絶縁膜13と、ゲート絶縁膜13の表面上に形成され、不純物領域14と不純物領域15とが接触するように形成されたポリシリコン層32を含むゲート電極16とを備えている。そして、不純物領域15は、ゲート電極16のドレイン領域9側に形成されている。

(もっと読む)

半導体装置

【課題】ソース−ドレイン間の耐圧を確保しつつ、その間隔の微細化を可能にした半導体装置を提供する。

【解決手段】半導体装置は、P型シリコン基板1上に形成したN型エピタキシャルシリコン層5および両者の界面に埋設したN型埋込拡散層3からなる半導体基板と、N型エピタキシャルシリコン層5の主表面SからN型埋込拡散層3に達するトレンチ17と、トレンチ17内の側面を被覆するシリコン酸化膜18と、このシリコン酸化膜18を介してトレンチ17内を埋め込むとともにN型埋込拡散層3に接続する引き出し層19と、同主表面Sに設けたトレンチ9と、このトレンチ9内にシリコン酸化膜10aを介して設けたゲート電極11と、トレンチ9の両側面に設けたN型ソース拡散層13と、同主表面Sにおいてトレンチ17とN型ソース拡散層13との間に設けたトレンチ17aと、このトレンチ17a内に充填したシリコン酸化膜18aと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極間の寸法を低減し得る半導体装置を提供する。

【解決手段】半導体装置は、半導体基板(5)と、半導体基板(5)に埋設された複数のゲート電極11a〜11cと、複数のゲート電極11a〜11cの各々の上に設けられた第1の絶縁層(12a〜12c)と、半導体基板(5)の表面に形成された導電層(13)と、導電層(13)上に設けられた導体層15とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】DMOSトランジスタを含む半導体装置において、チップ面積を小さくすること、及びオン抵抗が低く、電流駆動能力の高いDMOSトランジスタを提供することを目的とする。

【解決手段】N型のエピタキシャル層2の表面に逆導電型(P型)のP+W層4を形成し、当該P+W層4内にDMOSトランジスタ70を形成する。エピタキシャル層2とドレイン領域とは、P+W層4によって絶縁される。そのため、絶縁分離層15で囲まれた一つの領域内に、DMOSトランジスタと他のデバイス素子を混載できる。また、ゲート電極6の下方におけるP+W層4の表面領域にN型のFN層20を形成する。ゲート電極6のドレイン層12側の端部に隣接したN+D層23を形成する。また、ドレイン層12のコンタクト領域の下方に、ドレイン層12よりも深いP型不純物層(P+D層22,FP層24)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】接合領域の耐圧性能を高めた素子分離領域を備える半導体装置及びその製造方法を提供する。

【解決手段】半導体基板100における素子分離絶縁膜106下に形成された第1導電型の第1の不純物領域107と、半導体基板における素子形成領域に形成された第2導電型の第2の不純物領域114と、半導体基板における第1の不純物領域と第2の不純物領域との間に位置する領域に、第1の不純物領域に隣接して形成された第1導電型の第3の不純物領域108と、半導体基板における第2の不純物領域と第3の不純物領域との間に位置する領域に、第2の不純物領域及び第3の不純物領域に隣接して形成された第2導電型の第4の不純物領域115とを備え、第3の不純物領域108は、第1の不純物領域107に比べて第1導電型不純物の不純物濃度が低く、第4の不純物領域115は、第2の不純物領域114に比べて第2導電型不純物の不純物濃度が低い。

(もっと読む)

半導体装置およびその製造方法

【課題】リサーフ構造を採用しながら基板電位とソース電位とを異ならせることができる半導体装置およびその製造方法を提供すること。

【解決手段】P−型半導体基板1上には、N−型エピタキシャル層2が形成され、このN−型エピタキシャル層2には、環状のP型ボディ拡散領域4が形成されている。P型ボディ拡散領域4には、N+型ソース拡散領域5とP+型ボディコンタクト領域6とが形成されている。N−型エピタキシャル層2には、N+型ドレイン拡散領域8が形成されている。ゲート電極10は、N+型ソース拡散領域5とN+型ドレイン拡散領域8との間のP型ボディ拡散領域4上に配置されている。P−型半導体基板1とN−型エピタキシャル層2とに跨って、N+型埋め込み拡散層14が形成され、N+型埋め込み拡散層14とP型ボディ拡散領域4との間には、P型埋め込み拡散層15がそれらに接して形成されている。

(もっと読む)

高電圧MOSFET用リサーフ拡散の方法

高電圧半導体装置用のウエハーが、先ず砒素をP型シリコン基板ウエハーの上面に約0.1ミクロンの深さまで注入することによって形成される。次にN型の非傾斜エピタキシャル層が、砒素が意図的に動かされないように、どんな拡散工程も無しに基板上に成長させられる。次に装置の接合がエピタキシャル成長層中に拡散させられる。 (もっと読む)

半導体デバイス・チャネル終端

半導体デバイスは、フィールド酸化膜(32)で充填されたトレンチ(30)、およびトレンチの下に、トレンチ(30)の外縁(36)に沿って第1の主面(8)からp−ウェル(6)を通って延び、トレンチの内縁(34)を過ぎて延びるチャネル・ストッパ・リング(18)を使用するためのチャネル終端領域を有する。この非対称チャネル・ストッパ・リングは、トレンチ(30)と同じ距離に延びることができるチャネル(10)に対する有効な終端を提供する。  (もっと読む)

(もっと読む)

1 - 19 / 19

[ Back to top ]