Fターム[5F152CF25]の内容

再結晶化技術 (53,633) | 被結晶化層の上方の層 (1,379) | 形状(結晶化直前の状態) (155) | 孔、溝 (32)

Fターム[5F152CF25]に分類される特許

1 - 20 / 32

半導体装置

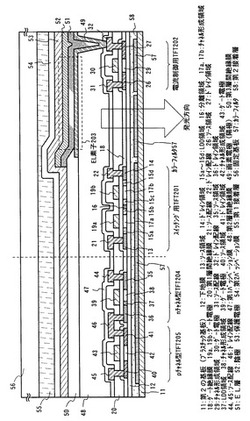

【課題】プラスチック支持体を用いた半導体装置を提供する。

【解決手段】プラスチック支持体上に形成されたカラーフィルタと、前記カラーフィルタ

上に形成された接着層と、前記接着層上に形成された絶縁膜と、前記絶縁膜上に形成され

た薄膜トランジスタと、前記薄膜トランジスタ上に形成された発光素子とを有する。また

は、プラスチック支持体と、前記プラスチック支持体に対向する対向基板と、前記プラス

チック支持体と前記対向基板との間に保持された液晶とを有し、前記プラスチック支持体

上に形成されたカラーフィルタと、前記カラーフィルタ上に形成された接着層と、前記接

着層上に形成された絶縁膜と、前記絶縁膜上に形成された薄膜トランジスタとを有する。

(もっと読む)

半導体膜の形成方法、並びに、その半導体膜を用いた半導体装置、ディスプレイ装置。

【課題】結晶欠陥が低減されて結晶性が良好な半導体膜の形成方法及びその成方法を用いて製造された半導体装置並びにディスプレイ装置を提供する。

【解決手段】ガラス基板11上に非晶質シリコン膜12を形成する工程と、非晶質シリコン膜12の表面に、結晶化を促進する触媒物質であるニッケルを含むニッケル薄膜13を形成する工程と、非晶質シリコン膜12を熱処理して、非晶質シリコン膜12を結晶性シリコン膜12に結晶化する工程と、結晶性シリコン膜12に、隣接する各結晶粒の結晶方位角度差が、概略10°以下あるいは58°〜62°を保持する最も高い値になるようなエネルギー密度を有するエキシマレーザーを照射して、結晶性シリコン膜12の結晶性をさらに向上させて多結晶半導体膜とする工程とを包含する。

(もっと読む)

半導体装置

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】製造工程を簡略化しつつソース電極及びドレイン電極の導電性を向上させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、基板101上にゲート電極103を形成する工程と、ゲート電極103上にゲート絶縁層104を形成する工程と、ゲート絶縁層104上にアモルファスシリコン層105を形成する工程と、アモルファスシリコン層105上にアルミニウム層111を形成し、アルミニウム層111上にモリブデンタングステン層112を形成し、アルミニウム層111及びモリブデンタングステン層112を少なくとも含む積層体から構成されるソース電極109及びドレイン電極110を形成する工程と、ソース電極109及びドレイン電極110をマスクとしアモルファスシリコン層105にレーザを照射することでアモルファスシリコン層105の一部を結晶化させチャネル領域を形成する工程とを含む。

(もっと読む)

半導体装置の作製方法

【課題】高集積化を妨げずに、多結晶TFTのオン電流及び移動度を高めることができる半導体装置の作製方法と、それによって得られる半導体装置の提供を課題とする。

【解決手段】半導体膜に触媒元素を添加して加熱することで、結晶性が高められた第1の領域と、第1の領域と比較して結晶性が劣っている第2の領域とを形成し、第1の領域に第1のレーザー光を照射することで、第1の領域よりも結晶性が高められた第3の領域を形成し、第2の領域に第2のレーザー光を照射することで、第2の領域よりも結晶性が高められた第4の領域を形成し、第3の領域と第4の領域をパターニングして、第1の島状の半導体膜と、第2の島状の半導体膜をそれぞれ形成し、第1と第2のレーザー光は、互いにエネルギー密度が同じであり、第1のレーザー光の走査速度は第2のレーザー光の走査速度より速い半導体装置の作製方法。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、及びそれらの製造方法、並びに表示装置

【課題】歩留まり向上が可能で、かつ品質向上につながる薄膜トランジスタ、薄膜トランジスタアレイ基板、及びそれらの製造方法、並びに表示装置を提供すること。

【解決手段】本発明に係る薄膜トランジスタの製造方法は、基板1上にゲート電極2を形成する工程と、ゲート電極2上にゲート絶縁膜3を形成する工程と、ゲート絶縁膜3上に、ゲート電極2の少なくとも一部と対向配置する半導体層10のパターン形成する工程と、半導体層10上にソース電極5、及びドレイン電極6を形成する工程と、ソース電極5、及びドレイン電極6をマスクとして、チャネル領域10Cに相当する半導体層10を所望の膜厚までエッチングする工程と、露出した半導体層10にレーザ光を照射する工程とを備える。

(もっと読む)

半導体装置の製造方法、電気光学装置、および電子機器

【課題】結晶面方位が一定であり、相対的に高密度に集積が可能であり、かつ、比較的簡単なプロセスを有する半導体装置の製造方法を提供する。

【解決手段】半導体層に金属原子を導入して熱処理をすることにより半導体層の結晶配向を制御する半導体装置の製造方法(MILC法)において、半導体層の一定形状を有する領域(114)に金属原子を導入する工程を備えることにより、半導体層に応力を生じさせ応力により半導体層の結晶面方位を制御するものである。この一定形状は、熱処理時に半導体層に応力を生じさせることが可能な角部(P)を有することを特徴とする。

(もっと読む)

多結晶半導体薄膜の製造方法、多結晶半導体薄膜、半導体装置及び表示装置

【課題】薄膜トランジスタのチャネル領域に用いた場合にそのキャリア移動度を高め、且つ、特性ばらつきを小さくする多結晶半導体薄膜の製造方法、多結晶半導体薄膜、半導体装置及び表示装置を提供する。

【解決手段】多結晶半導体薄膜の製造方法は、特定のエネルギー密度の結晶化エネルギーを特定方向に走査しながら付与することにより、所定領域の非晶質珪素膜の膜面に平行に{101}面が優先配向し、結晶化エネルギーの走査方向に{100}面が優先配向し、結晶化エネルギーの走査方向に対して直交する方向に{101}面が優先配向した結晶面を有する多結晶珪素の結晶核を形成する結晶核形成工程と、優先配向した結晶面に対応する領域以外の領域に非晶質珪素膜を形成する結晶核制御工程と、非晶質珪素膜に珪素膜の結晶化を助長する触媒物質を導入して膜面と略平行な方向に結晶成長させる結晶粒成長工程と、を備える。

(もっと読む)

薄膜トランジスタ

【課題】薄膜トランジスタ及びその製造方法を供給する。

【解決手段】薄膜トランジスタは基板と、該基板上に形成され、チャンネル層にシード及び結晶粒境界が存在しない半導体層パターンと、該半導体層パターン上に形成されたゲート絶縁膜及び該ゲート絶縁膜上に形成されたゲート電極とを含む。この方法は、基板上に非晶質シリコン層を形成する段階と、該非晶質シリコン層を結晶化し、パターニングしてチャンネル層にシード及び結晶粒境界が存在しない半導体層パターンを形成する段階と、前記半導体層パターン上にゲート絶縁膜を形成する段階及び前記ゲート絶縁膜上にゲート電極を形成する段階とを含む。結晶化触媒の均一な低濃度制御及び結晶化位置を調節することによって、薄膜トランジスタのチャンネル層内にシード及び結晶粒境界が存在しないようにしたり、結晶粒境界が一つ存在するように調節して素子特性及び均一度を良くする。

(もっと読む)

半導体膜の形成方法、並びに、その半導体膜を用いた半導体装置、ディスプレイ装置。

【課題】結晶欠陥が低減されて結晶性が良好な半導体膜の形成方法及びその成方法を用いて製造された半導体装置並びにディスプレイ装置を提供する。

【解決手段】ガラス基板11上に非晶質シリコン膜12を形成する工程と、非晶質シリコン膜12の表面に、結晶化を促進する触媒物質であるニッケルを含むニッケル薄膜13を形成する工程と、非晶質シリコン膜12を熱処理して、非晶質シリコン膜12を結晶性シリコン膜12に結晶化する工程と、結晶性シリコン膜12に、隣接する各結晶粒の結晶方位角度差が、概略10°以下あるいは58°〜62°を保持する最も高い値になるようなエネルギー密度を有するエキシマレーザーを照射して、結晶性シリコン膜12の結晶性をさらに向上させて多結晶半導体膜とする工程とを包含する。

(もっと読む)

有機電界発光表示装置及びその製造方法

【課題】非表示領域にアラインマークを形成して結晶化工程中に多結晶シリコンの形成位置を正確に制御及び最適特性のアクティブ層を形成する。

【解決手段】表示領域211と非表示領域212とを有する基板210と、バッファ層220と、非表示領域212に対応するバッファ層220に形成されたアラインマーク230と、表示領域211に対応するバッファ層220に形成されたアクティブ層240と、ゲート絶縁膜250と、アクティブ層240に対応するゲート絶縁膜250に形成されたゲート電極260と、ゲート電極260に形成された層間絶縁膜270と、層間絶縁膜270に形成され、アクティブ層240と電気的に連結されるソース/ドレイン電極280と、ソース/ドレイン電極280に形成された絶縁膜290と、絶縁膜290に形成され、ソース/ドレイン電極280に電気的に接続される有機電界発光素子300と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】簡便な製造プロセスにより、量産対象である大型のガラス基板に、信

頼性が高く、集積度の高い高性能半導体装置を得る。

【解決手段】結晶化を促進する微量の触媒元素であるニッケル105が導入さ

れたa−Si膜103を加熱処理して結晶化された結晶性のケイ素膜108の一

部の領域(高濃度不純物領域)108bに選択的に5族Bから選択された不純物

であるリン117を導入し、第2の加熱処理を行って、結晶性のケイ素膜108

のリン117が導入されていない領域(能動領域)108aに含まれるニッケル

105を高濃度不純物領域に移動させる。この第2の加熱処理は、能動領域10

8aに含まれるニッケル105の濃度と高濃度不純物領域108bに含まれるニ

ッケル105の濃度とが少なくとも熱平衡状態の偏析状態に達しないように行う

。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法の1形態として、多結晶半導体を用いて薄膜トランジスタ(TFT)を形成する工程で、TFT内部にあるチャネル領域に、異なる結晶粒径を有する構造を形成することは困難であった。そのため、チャネル領域に電流駆動能力の大きい結晶粒の大きいTFTを形成すると寄生バイポーラ効果により電気的な動作が不安定になる。又寄生バイポーラ効果を抑制可能な微細結晶を用いた場合には、電流駆動能力が小さくなるという課題がある。

【解決手段】チャネル部分に半透過マスクを用いたパターンを形成し、レーザーアニールを行う場合に、チャネル近傍でのアニール後の結晶粒の分布を制御する。例えばチャネル中央領域に強いレーザーアニールを行い、ゲート端部に弱いレーザーアニールを施すことで寄生バイポーラ動作の発生を抑制し、且つ高い電流駆動能力を持つ半導体装置としてのTFTの製造方法を提供することができる。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】本発明は、薄膜トランジスタの半導体に含まれている金属による漏洩電流を最少化して薄膜トランジスタの特性及び信頼度を向上させる。

【解決手段】本発明による薄膜トランジスタ表示板の製造方法は、絶縁基板上に非晶質シリコン膜を形成する段階と、非晶質シリコン膜上に凹凸を有する犠牲膜を形成する段階と、犠牲膜上に金属板を接触させた後、熱処理することによって非晶質シリコン膜を結晶化して多結晶シリコン膜を形成する段階と、金属板及び犠牲膜を除去する段階と、多結晶シリコン膜をパターニングして島状部材を形成する段階と、島状部材を覆うようにゲート絶縁膜を形成する段階と、ゲート絶縁膜上に島状部材と一部分が重なるゲート線を形成する段階と、島状部材の所定領域に導電型不純物を高濃度にドーピングしてソース/ドレイン領域を形成する段階と、ゲート線及び島状部材を覆うように層間絶縁膜を形成する段階と、層間絶縁膜上にソース/ドレイン領域と連結されるデータ線及び出力電極を形成する段階と、を含む。

(もっと読む)

半導体装置の作製方法

【課題】触媒元素のスピン添加法は、対角線の長さが500mm以上の大型基板を用いる際、触媒元素添加量の基板内均一性が良くないという問題が顕著となる。触媒元素添加量の基板内不均一性は、熱結晶化後の結晶質半導体膜に於ける結晶性のバラツキに影響し最終的に当該結晶質半導体膜で構成されたTFTの電気特性に悪影響を及ぼすことが考えられる。本発明は、上記問題点を解決することを課題とする。

【解決手段】触媒元素のスピン添加工程に於いて、絶縁性基板の中央部と、端部とにおける触媒元素の濃度比が2倍以内となるように添加するために、「触媒元素溶液の滴下」処理から「高速スピンによるスピン乾燥」処理に移行する間のスピン回転加速度を低くし、触媒元素添加量の基板内不均一性を改善する。

(もっと読む)

半導体装置

【課題】金属元素を用いて結晶化させた珪素膜を活性層として用いた半導体装置において、金属元素による半導体装置の特性への悪影響を排除する。

【解決手段】 珪素の結晶性を助長する金属元素を用いて結晶化させた結晶性珪素膜を活性層とする半導体装置において、ソース領域またはドレイン領域が形成される領域114、116に燐をドーピングし、加熱処理を施す。その際、領域115に存在する金属元素が、120、121で示されるように、燐がドーピングされた領域にゲッタリングされる。その結果、チャネル領域または低濃度不純物領域が形成される領域117乃至119における金属元素の濃度を低くすることができる。

(もっと読む)

半導体装置

【課題】金属元素を利用して得られた結晶性珪素膜中の当該金属元素の影響を抑え、優れた性能を備えた半導体装置を得ることを目的とする。

【解決手段】結晶化を助長する金属元素を利用して得た結晶性珪素膜で構成された活性層と、前記活性層上に形成されたゲイト絶縁膜と、を有し、前記ゲイト絶縁膜は、ハロゲン元素を含有する絶縁膜を有する。ハロゲン元素を含有する絶縁膜によって、結晶化を助長する金属元素を固定化し、ゲイト絶縁膜の機能低下を防止する。

(もっと読む)

半導体装置

【課題】他の半導体装置と一体形成が可能な不揮発性メモリを提供する。

【解決手段】不揮発性メモリを構成するメモリ素子、スイッチング素子,および他の周辺回路をTFTでもって基板上に一体形成する。メモリ素子TFTの半導体活性層の厚さが、他のTFTの半導体活性層の厚さよりも薄いので、メモリ素子TFTのチャネル領域でインパクトイオン化が起こりやすくなる。こうすることによって、メモリ素子の低電圧書込み/消去を実現することができ、劣化が起こりにくく、小型化が可能な不揮発性メモリが提供される。

(もっと読む)

半導体装置の作製方法

【課題】極めて結晶性に優れた半導体薄膜及びそれを用いた高性能な半導体装置を提供する。

【解決手段】絶縁表面を有する基板上にプラズマCVD法によってフッ化水素酸とフッ化アンモニウムと界面活性剤の混合物に対するエッチングレートが150〜200nm/minである二酸化珪素膜からなる下地膜を形成し、下地膜上に非晶質珪素膜を形成し、非晶質珪素膜を結晶化することによって面方位が概略{111}配向の結晶性珪素膜を形成し、結晶性珪素膜をエッチングすることによって島状半導体層を形成し、島状半導体層上にゲイト絶縁膜を形成し、ゲイト絶縁膜上にゲイト電極を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】信頼性を向上させることが可能な薄膜トランジスタの作製方法を提供する。

【解決手段】nチャネル型TFTとpチャネル型TFT各々は、半導体層と、半導体層上に接して形成されたゲート絶縁膜と、ゲート絶縁膜を挟んで半導体層と重なるゲート電極とを有し、nチャネル型TFTのゲート電極とpチャネル型TFTのゲート電極は同一の導電層からなり、nチャネル型TFTのゲート電極は端部がテーパー状であって、側面とゲート絶縁膜の表面のなす角度が3度以上60度以下の範囲にあり、pチャネル型TFTのゲート電極は端部がテーパー状であって、側面とゲート絶縁膜の表面のなす角度が70度以上85度以下の範囲にある。

(もっと読む)

1 - 20 / 32

[ Back to top ]