Fターム[5F152LN03]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 目的 (706) | 歪みによる悪影響防止 (524) | 転位、クラック等の低減又は抑制 (334)

Fターム[5F152LN03]に分類される特許

1 - 20 / 334

シリコン基板、これを採用したエピ構造体及びシリコン基板の製造方法

エピタキシャルウェーハとその製造方法

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

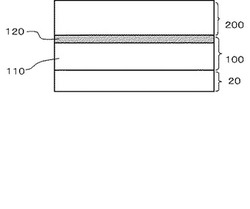

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

III族窒化物複合基板

【課題】支持基板と酸化物膜との接合強度および酸化物膜とIII族窒化物層との接合強度が高いIII族窒化物複合基板を提供する。

【解決手段】本III族窒化物複合基板1は、支持基板10と酸化物膜20とIII族窒化物層30aとを含み、支持基板10は多結晶で形成され、III族窒化物層30aは少なくともc軸方向に配向しているIII族窒化物結晶で形成され、酸化物膜20は不純物が添加され、不純物の濃度は、酸化物膜20において支持基板10側の第1主面20sからIII族窒化物層30a側の第2主面20tにかけて膜厚方向で変化し、第1主面20sにおける不純物の濃度は第2主面20tにおける不純物の濃度よりも高い。

(もっと読む)

窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法

【課題】シリコン基板上に形成した、転位及びクラックの少ない窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法を提供する。

【解決手段】実施形態によれば、シリコン基板と、その上に順次設けられた、下側歪緩和層、中間層、上側歪緩和層及び機能層と、を有する窒化物半導体ウェーハが提供される。中間層は、第1下側層と、第1ドープ層と、第1上側層と、を含む。第1下側層は、下側歪緩和層の上に設けられ下側歪緩和層の格子定数よりも大きい格子定数を有する。第1ドープ層は、第1下側層の上に設けられ第1下側層の格子定数以上の格子定数を有し1×1018cm−3以上1×1021cm−3未満の濃度であり第1下側層よりも高い濃度で不純物を含有する。第1上側層は、第1ドープ層の上に設けられ第1ドープ層の格子定数以上で第1下側層の格子定数よりも大きい格子定数を有する。

(もっと読む)

複合基板の製造方法

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成するステップと、犠牲層の一部が露出するように半導体結晶層をエッチングし、半導体結晶層を複数の分割体に分割するステップと、転写先基板に接することとなる半導体結晶層形成基板側の第1表面と、第1表面に接することとなる転写先基板側の第2表面と、が向かい合うように、半導体結晶層形成基板と転写先基板とを貼り合わせるステップと、半導体結晶層形成基板および転写先基板をエッチング液に浸漬して犠牲層をエッチングし、半導体結晶層を転写先基板側に残した状態で、転写先基板と半導体結晶層形成基板とを分離するステップと、を有し、前記半導体結晶層が、GexSi1−x(0<x≦1)からなる、複合基板の製造方法を提供する。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板であって、前記バッファ層が、第1結晶層と第2結晶層が交互に複数積層された積層構造体であり、前記第1結晶層が、AlmGa1−mN、(但し0≦m≦1)で表される結晶からなり、前記第2結晶層が、AlnGa1−nN、(但し0≦n≦1、m>n)で表される結晶からなり、前記第1結晶層の格子緩和度が、前記第2結晶層の格子緩和度より大きい半導体基板を提供する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後に、前記ベース基板の温度を1000℃以上に維持しつつ前記ベース基板の表面をアンモニアガスとキャリアガスとの混合ガスに暴露するアンモニアガス暴露工程と、前記アンモニアガス暴露工程の後に、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、前記ベース基板の温度を1000℃以上1150℃以下に維持しつつ前記ベース基板の表面を水素ガスに暴露する水素ガス暴露工程と、前記水素ガス暴露工程の後、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

エピタキシャルウェーハとその製造方法

【課題】歪み層形成に供されるウェーハで転位発生に対して耐性が高いエピタキシャルウェーハを提供する。

【解決手段】シリコンエピタキシャル層表面の酸素濃度が1.0×1017〜12×1017atoms/cm3とされてなるエピタキシャルウェーハの製造方法であって、酸素濃度設定熱処理の処理温度Xと処理時間Yとが、処理温度Xが800℃〜1400℃の範囲、処理時間Yが180min以下で、かつ、

Y ≧ 1.21×1010 exp(−0.0176X)

の関係を満たすように設定される。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、ベース基板の上に、接着層、バッファ層および活性層をエピタキシャル成長法により順次形成する層形成工程を有し、接着層形成工程が、第1結晶層を形成する工程と第2結晶層を形成する工程と、を有し、第1結晶層の形成後であって第2結晶層の形成前の第1の段階、および、第2結晶層の形成後であってバッファ層の形成前の第2の段階、からなる群から選択された少なくとも1つの段階において、3族原料ガスの供給を停止するとともに成長室の内部を、アンモニアを含むガスの雰囲気に一定時間だけ維持する雰囲気維持工程を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板を洗浄装置の洗浄室に設置し、前記ベース基板の表面をHF水溶液により洗浄する第1洗浄工程と、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体結晶基板、半導体結晶基板の製造方法、半導体装置の製造方法、電源装置及び増幅器

【課題】基板の外周部においてクラックの発生が抑制される半導体結晶基板を提供する。

【解決手段】半導体結晶基板110と、基板110の表面に窒化物により形成された保護層120と、を有し、保護層120は、基板110の外周部となる周辺領域120aはアモルファス状態であり、基板110の周辺領域よりも内側の内部領域120bは結晶化している。

(もっと読む)

窒化物系化合物半導体結晶及びその製造方法並びにIII族窒化物半導体デバイス用基板

【課題】GaN結晶インゴットを含む窒化物系化合物半導体結晶から自立基板を切り出す際のクラックの発生を抑制した窒化物系化合物半導体結晶及びその製造方法並びにIII族窒化物半導体デバイス用基板を提供する。

【解決手段】窒化物系化合物半導体結晶としてのGaN結晶インゴット100は、厚さ方向に沿って外周領域100aとその内側の中心領域100bとを有し、外周領域100aの厚さ方向に垂直な面(Ga極性のc面101)の転位密度の最大値が、中心領域100bの厚さ方向に垂直な面(Ga極性のc面101)の転位密度の最小値の2.0倍以上20倍以下となる転位密度分布を有する。

(もっと読む)

半導体装置、電気光学装置、電力変換装置及び電子機器

【課題】素子特性の低下を抑制することが可能な半導体装置を提供する。

【解決手段】シリコン基板11と、シリコン基板11の表面に形成された炭化シリコン膜12と、炭化シリコン膜12の表面に形成された、開口部13hを有するマスク材13と、開口部13hにおいて露出した炭化シリコン膜12を基点としてエピタキシャル成長された、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14と、単結晶炭化シリコン膜14の表面に形成された半導体素子20と、を含み、マスク材13の上には、単結晶炭化シリコン膜14が会合して形成された会合部12Sbが存在しており、半導体素子20はボディコンタクト領域21を有しており、ボディコンタクト領域21は、シリコン基板11の表面と直交する方向から見て会合部12Sbと重なる位置に配置されている。

(もっと読む)

単結晶炭化シリコン膜の製造方法及び単結晶炭化シリコン膜付き基板の製造方法

【課題】結晶欠陥の少ない高品質なエピタキシャル膜を得ることが可能な単結晶炭化シリコン膜の製造方法及び単結晶炭化シリコン膜付き基板の製造方法を提供する。

【解決手段】シリコン基板11上に単結晶炭化シリコン膜14を形成する単結晶炭化シリコン膜14の製造方法であって、シリコン基板11の表面に炭化シリコン膜12を形成する第1の工程と、炭化シリコン膜12の表面にマスク材13を形成する第2の工程と、マスク材13に開口部13hを形成し、炭化シリコン膜12の一部を露出させる第3の工程と、原料ガスを含むガス雰囲気中でシリコン基板11を加熱し、炭化シリコン膜12を基点として単結晶炭化シリコンをエピタキシャル成長させ、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14を形成する第4の工程と、を含み、原料ガスを含むガス雰囲気の圧力は、5.0×10−4Pa以上かつ0.5Pa以下である。

(もっと読む)

複合基板およびその製造方法、ならびに複合ウエハ

【課題】III族窒化物とは化学組成の異なる異組成基板とIII族窒化物層とが貼り合わされた複合基板であっても、反りおよびクラックを発生させることなくその複合基板上にIII族窒化物エピタキシャル層を形成することができる複合基板およびその製造方法を提供する。

【解決手段】本複合基板2Dは、III族窒化物以外の化学組成を有する異組成基板10と、異組成基板10に貼り合わされたIII族窒化物層21と、含み、III族窒化物層21は、平面充填が可能な少なくとも1種類の平面形状を有する複数のIII族窒化物タイル21pに分離している。

(もっと読む)

III族窒化物エピタキシャル基板およびその製造方法

【課題】デバイス化の工程で割れが発生することを抑制することが可能なIII族窒化物エピタキシャル基板およびその製造方法を提供する。

【解決手段】本発明のIII族窒化物エピタキシャル基板10は、Si基板11と、該Si基板11と接する初期層14と、該初期層14上に形成され、Al組成比が0.5超え1以下のAlGaNからなる第1層15A1(15B1)およびAl組成比が0超え0.5以下のAlGaNからなる第2層15A2(15B2)を順次有する積層体を複数組有する超格子積層体15と、を有し、前記第2層のAl組成比が、前記基板から離れるほど漸減することを特徴とする。

(もっと読む)

窒化物半導体エピタキシャル基板及び窒化物半導体デバイス

【課題】低転位であり、クラック発生を抑制できるIII族窒化物半導体層を有する窒化物

半導体エピタキシャル基板及び窒化物半導体デバイスを提供する。

【解決手段】基板上にAlを含むIII族窒化物半導体のバッファ層を介して成長した、C

面を表面とするIII族窒化物半導体層を有する窒化物半導体エピタキシャル基板であって

、前記バッファ層が、その表面にインバージョンドメインを有する。

(もっと読む)

半導体装置の製造方法

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18を形成した後、In含有ガスを供給しつつ、基板10を昇温させる工程と、昇温が終了した後、InAlN電子供給層18上にGaN層20を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

1 - 20 / 334

[ Back to top ]