Fターム[5F152LN23]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 熱処理 (195) | 熱サイクル (21)

Fターム[5F152LN23]に分類される特許

1 - 20 / 21

エピタキシャル成長用基板およびエピタキシャル成長用基板の製造方法

【課題】平坦性、結晶性および配向性に優れ、厚さ方向の熱伝導率が高く放熱性に優れたエピタキシャル成長用基板およびその製造方法を提供する。

【解決手段】炭素基板の少なくとも一方の主表面に、算術平均表面粗さRaが0.05μm以下で、表面粗さの最大値Ryが0.5μm以下であり、X線回折法による(0002)面のロッキングカーブの半値幅が1.5度以下であり、ラマンスペクトルにおけるGバンドのピーク強度に対するDバンドのピーク強度の比が0.01以下である高結晶グラファイト層を形成してなることを特徴とするエピタキシャル成長用基板である。

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】中間層としてGe結晶を用いる場合の化合物半導体へのGe原子の混入を抑制する。

【解決手段】ベース基板と、ベース基板上に形成された第1結晶層と、第1結晶層を被覆する第2結晶層と、第2結晶層に接して形成された第3結晶層とを備え、第1結晶層が、ベース基板における第1結晶層と接する面と面方位が等しい第1結晶面、及び、第1結晶面と異なる面方位を有する第2結晶面を有し、第2結晶層が、第1結晶面と面方位が等しい第3結晶面、及び、第2結晶面と面方位が等しい第4結晶面を有し、第3結晶層が、第3結晶面及び第4結晶面のそれぞれの少なくとも一部に接しており、第1結晶面に接する領域における第2結晶層の厚みに対する第2結晶面に接する領域における第2結晶層の厚みの比が、第3結晶面に接する領域における第3結晶層の厚みに対する第4結晶面に接する領域における第3結晶層の厚みの比よりも大きい半導体基板を提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】基板と当該基板に形成される化合物半導体とを電気的に絶縁しつつ、結晶性に優れた化合物半導体を備えた半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられたシード結晶と、シード結晶の上方に設けられた化合物半導体と、シード結晶と化合物半導体との間に設けられ、シード結晶よりも大きな抵抗率を有する高抵抗層とを備え、シード結晶と化合物半導体とが格子整合または擬格子整合している半導体基板を提供する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板上に結晶成長され、孤立した島状に形成されたGe層と、Ge層上に結晶成長された機能層と、を備える半導体基板を提供する。Ge層は、アニールした場合に、アニールの温度および時間において結晶欠陥が移動する距離の2倍を越えない大きさの島状に形成する。あるいはGe層は、アニールした場合に、アニールの温度において基板であるSiとの熱膨張係数の相違によるストレスが剥離を発生させない大きさの島状に形成する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板上に結晶成長され、孤立した島状に形成されたGe層と、Ge層の上に結晶成長され、Pを含む3−5族化合物半導体層からなるバッファ層と、バッファ層の上に結晶成長された機能層と、を備える半導体基板を提供する。Ge層は、アニールした場合に、アニールの温度および時間において結晶欠陥が移動する距離の2倍を越えない大きさの島状に形成する。あるいはGe層は、アニールした場合に、アニールの温度において基板であるSiとの熱膨張係数の相違によるストレスが剥離を発生させない大きさの島状に形成する。

(もっと読む)

半導体基板およびその製造方法、ならびに半導体装置

【課題】圧縮歪層と引張歪層とを利用して、InP系半導体デバイスを成長させるメタモルフィック基板の欠陥(例えば転位)の低減を可能にする。

【解決手段】ガリウムヒ素基板100と、前記ガリウムヒ素基板100上に形成されたバッファ層101と、前記バッファ層101上に、前記バッファ層101よりも面内方向の格子定数が小さい材料からなる引張歪層105aと、前記バッファ層101よりも面内方向の格子定数大きい材料からなる圧縮歪層105bとを積層して形成された歪補償構造層105とを有することを特徴とする。

(もっと読む)

SiGeオンインシュレータ基板材料

【課題】 向上された緩和、かなり低い欠陥密度、および改善された表面品質を有する

緩和されたSiGeオンインシュレータ基板を形成する方法を提供すること。

【解決手段】 方法が、第1の単結晶Si層の表面上にSiGe合金層を形成するステ

ップを含む。第1の単結晶Si層は、Ge拡散に対する耐性がある下の障壁層との界面を

有する。次に、界面での、または界面付近での機械的な分断を可能にする欠陥を形成する

ことができるイオンが構造内に注入され、その後、注入されたイオンを含む構造に、第1

の単結晶Si層およびSiGe層を通るGeの相互拡散を可能にする加熱ステップを施し

て、障壁層の上に、実質的に緩和された単結晶であり均質のSiGe層を形成する。改善

された性質を有するSiGeオンインシュレータ、およびそれを含むヘテロ構造も提供さ

れる。

(もっと読む)

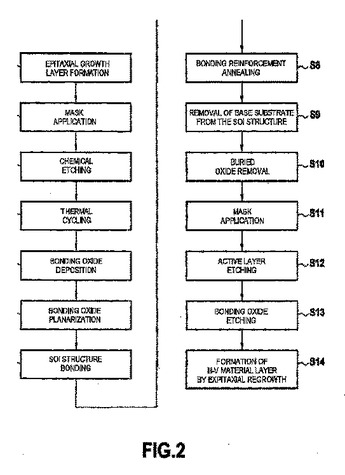

多層構造及びその製造プロセス

本発明は、多層構造を製造するためのプロセスであって、a)シリコン基板上で成長層をエピタキシャル成長するステップ(S1)と、b)成長層において少なくとも1つのパターンを形成するステップ(S2、S3)と、c)シリコン基板上に酸化層を堆積するステップ(S5)と、d)シリコン活性層を酸化層上へ転移するステップ(S7−S10)と、e)各パターンの上のシリコン活性層及び酸化層内にキャビティを形成するステップ(S11、S12)と、f)III−V族の物質のキャビティを成長層の各々の暴露されたパターンから成長させるステップ(S14)とを少なくとも備えることを特徴とするプロセスに関する。  (もっと読む)

(もっと読む)

AlN系III族窒化物単結晶厚膜の作製方法

【課題】結晶品質に優れ、かつクラックのないAlN系III族窒化物単結晶厚膜を作製する方法を提供する。

【解決手段】エピタキシャル基板上に、HVPE法によってAlN系III族窒化物厚膜を得る場合に、通常の成長条件で厚膜層の形成を行う第1の工程と、その時点で形成されている厚膜層を第1の工程における厚膜層の形成温度T1以上の高温状態T2で保持することを主目的とする第2の工程とを適宜のタイミングで切り替えつつ繰り返し行うようにする。これにより、それぞれの第1の工程において厚膜層に内在する歪を第2の工程で逐次に緩和させつつ厚膜層を形成することができる。厚膜層の形成後に面内方向に作用する引張応力を、あらかじめ緩和させた状態の厚膜層を形成することができるので、厚膜層におけるクラックの発生を抑制することができる。

(もっと読む)

半導体基板及びその製造方法

【課題】 量産性の高い、欠陥の充分少ない高品質なSSOI基板を提供する。

【解決手段】 半導体基板の製造方法は、支持基板とは格子定数の異なるヘテロエピタキシャル層、絶縁層、Si層が順に積層された構造を少なくとも含む支持基板に、前記Si層の歪みを変化させるために、前記ヘテロエピタキシャル層の応力を変化させる工程を行なう。

(もっと読む)

シリコン上に欠陥の少ない歪みエピタキシャルゲルマニウム膜を製造する方法

【課題】シリコン基板上に欠陥の少ない歪みゲルマニウム膜を製造する方法を提供すること。

【解決手段】本発明の方法は、シリコン基板を準備すること(12)と、第1のゲルマニウム膜を堆積し、シリコン基板上に連続したゲルマニウム膜を形成すること(14)と、シリコン基板およびゲルマニウム膜を第1のアニールプロセスでアニールし、ゲルマニウム膜を緩和すること(16)と、第1のゲルマニウム膜の上に第2のゲルマニウム膜を堆積し、ゲルマニウム層を形成すること(18)と、ゲルマニウム層をパターニングおよびエッチングすること(22)と、ゲルマニウム層の上に誘電体材料を堆積すること(24)と、ゲルマニウム層および誘電体材料を有するシリコン基板をサイクリックアニールすること(26)と、シリコン基板およびゲルマニウム膜を含むデバイスを完成すること(28)と、を含む。

(もっと読む)

窒化物半導体成長用基板

高品質の窒化物半導体結晶層を得ることができる窒化物半導体成長用基板を提供する。本発明の一実施形態に係る、サファイア基板(1)上に窒化物半導体層を成長させるための窒化物半導体成長用基板は、サファイア基板(1)上に別途に設けたAl2O3層(2)と、第1の層であるAlON層(3)と、第2の層であるAlN層(4)とを備える。第1の層および第2の層については、AlON層(3)とAlN層(4)との順序でAl2O3層(2)上に積層させる。  (もっと読む)

(もっと読む)

ヘテロ集積型歪みシリコンn型MOSFET及びp型MOSFET及びその製造方法

【課題】 n型及びp型MOSFETデバイスに使用するための半導体構造体と、その製造方法とを提供する。

【解決手段】 半導体構造体は、n型MOSFETが製造されるウェハ領域の層構造が、p型MOSFETが製造されるウェハ領域の層構造とは異なるものとなるように製造される。この構造体は、まず、Heなどの軽原子のイオン注入によりSi含有基板の表面に損傷領域を形成することによって、製造される。次いで、損傷領域を含むSi含有基板の上に、歪みSiGe合金が形成される。次いで、アニール・ステップを使用し、欠陥に起因する歪み緩和によって歪みSiGe合金を実質的に緩和させる。次に、緩和したSiGe合金の上に、歪みSiなどの歪み半導体キャップが形成される。

(もっと読む)

半導体基板及びその製造方法

【課題】ヘテロエピタキシャル成長膜の、応力の緩和と、緩和に伴って発生し表面へ貫通する結晶欠陥の密度の抑制を両立させるために要求される、膜厚に対する制限を低減し、プロセス設計の自由度を向上させる。

【解決手段】半導体基板の製造方法は、第1単結晶半導体10の上に第2単結晶半導体12を成長させる成長工程と、第2単結晶半導体12に阻止層12aを形成する阻止層形成工程と、阻止層12aよりも深い部分に結晶欠陥15を発生させて第2単結晶半導体12に作用する応力を緩和する緩和工程とを含む。阻止層12aは、例えば多孔質層で構成され、阻止層12aよりも深い部分の結晶欠陥が第2単結晶半導体12の表面に伝播することを防止する。

(もっと読む)

ホウ素またはヘリウムと、水素とともにシリコンを注入することによって、Ge含有量が高い緩和Si1−XGeX(0<x<1)層を形成する方法

【課題】 水素注入ドーズおよび/またはアニーリング温度および時間を低減させることによって、費用を削減し、かつ、膜の性質を向上させることができる緩和Si1−XGeX(0<x<1)層の形成方法を提供する。

【解決手段】 本発明による、半導体デバイスにおいて、ゲルマニウム含有量が高い緩和Si1−XGeX(0<x<1)層を形成する方法は、シリコン基板を準備することと(12)、歪Si1−XGeX(0<x<1)層を堆積することと(14)、歪SiGe層内にイオンを注入することであって、イオンは、シリコンイオンと、ホウ素およびヘリウムからなるイオンの群から選択されるイオンとを含み、H+イオンを注入することをさらに包含する、ことと(16、18)、アニーリングすること(20)により歪SiGe層を緩和し、それにより、第1の緩和SiGe層を形成することと、半導体デバイスを完成することとを包含する。

(もっと読む)

半導体基板を作製する方法

【課題】絶縁体上歪み半導体(SSOI)基板を作製する方法が提供される。

【解決手段】この方法で、歪み半導体は、あらかじめ形成された絶縁体上半導体基板の絶縁体層の上に直接配置された50nm未満の厚さを有する薄い半導体層である。本発明のSSOI基板を形成する際に、ウエハボンディングは使用されない。

(もっと読む)

1 - 20 / 21

[ Back to top ]