Fターム[5H740AA04]の内容

Fターム[5H740AA04]に分類される特許

441 - 444 / 444

貫通防止機能検査方法

【課題】同期整流機能を有する半導体集積回路の同期整流開始時及び終了時の貫通防止機能の測定結果を選択可能にし、貫通防止機能の検査を誤りなく実施する。

【解決手段】同期整流機能を有する出力回路の出力部に電源Vcc1よりも高い電圧で駆動する電流源9と、測定器8と、測定電圧と予め設定の電圧VRとを比較するコンパレータ10を接続する。コンパレータ10の出力は遅延時間を設定できる遅延回路11と演算器12の入力に接続され、演算器12は測定器8へトリガセット信号を出力する。遅延回路11の遅延時間を制御することにより、任意区間における貫通防止機能を選択して検査を実施する。

(もっと読む)

トライアックのトリガを制御するシステムおよび方法

この発明は、トライアックのゲートへの単一の短い期間のパルスであらゆる力率の負荷を動作させることにより、トライアックを制御しトリガするシステムに関する。単一のコンパレータ(CP1)を使用するために、また、電流レベル(Ic)で制限することなく動作させるために、トライアックを制御しトリガするシステムが予見され、前記トライアックはゲートを備え、かつ、負荷に接続され、ゲートは、制御ユニット4に接続され、 制御ユニットは、回路電圧Vacを負荷に印加して電流Icを流すためにトライアックを動作させ、システムは、ゲート電圧検出ユニット(1)、制御ユニット(4)、制御ユニット(4)に接続のゲート電圧検出ユニット(1)を備え、制御ユニットはゲート電圧限界値(+LIMIT,−LIMIT)を確立し、トライアックの導通を維持するためゲートにパルスを発生させ、ゲートでのパルスは、前記電圧限界値と、ゲート測定電圧との比較から発生され、制御ユニットは、Icを測定し、Icに比例して電圧限界値を調節する。

(もっと読む)

(もっと読む)

ダイナミックバックゲートバイアスを伴うブートストラップダイオードエミュレータ

【解決手段】ハーフブリッジスイッチング回路で使用するためのブートストラップダイオードエミュレータ回路が提供される。スイッチング回路は、負荷ノードにおいてトーテムポール構造の形で互いに繋がれているトランジスタと、これらのトランジスタを駆動するための駆動回路と、高圧側駆動回路に電力を供給するためのブートストラップコンデンサとを含む。ブートストラップダイオードエミュレータ回路は、ゲート、バックゲート、ソース、およびドレインを有し、そのドレインを高圧側供給ノードに結合され、そのソースを低圧側供給ノードに結合されているLDMOSトランジスタと、LDMOSトランジスタのゲートに電気的に結合されているゲート制御回路と、LDMOSトランジスタのバックゲートに電気的に結合されているダイナミックバックゲートバイアス回路とを備える。ダイナミックバックゲートバイアス回路は、LDMOSがオンにされたときに、LDMOSトランジスタのドレインの電圧に近いけれども同電圧よりも僅かに低い電圧をLDMOSトランジスタのバックゲートに印加することによって、LDMOSトランジスタのバックゲートを動的にバイアスするように動作可能である。 (もっと読む)

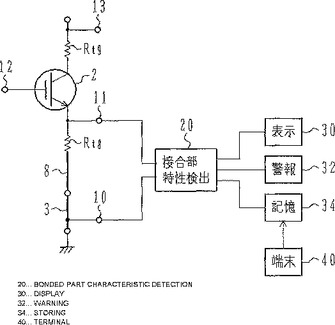

パワー半導体モジュール及びそれを用いた電力変換装置並びに移動体

本発明の目的は、小型で、しかも、金属接合部の劣化を精度良く検知できる半導体素子を用いたパワー半導体モジュール及びそれを用いた電力変換装置並びに移動体を提供することにある。パワー半導体素子(2)の表面電極と電極用の金属板(3)は、金属ワイヤ(8)により金属接合される。接合部特性検出回路(20)は、金属接合の接合部の特性を検出し、接合部の劣化による抵抗RT8の上昇と寿命の関係から決定したしきい値VLを用いて、接合部の劣化を予測する。  (もっと読む)

(もっと読む)

441 - 444 / 444

[ Back to top ]