Fターム[5J039AB03]の内容

パルスの操作 (9,993) | エッジ(トランジェント)の検出 (82) | 遅延出力との比較又は演算操作 (15)

Fターム[5J039AB03]に分類される特許

1 - 15 / 15

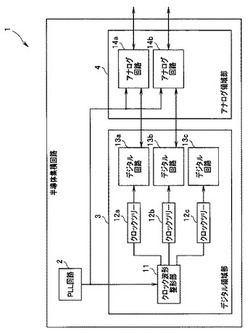

半導体集積回路

【課題】クロック信号の立ち下がりエッジで発生する消費電力を低減することができる半導体集積回路を提供することである。

【解決手段】実施の形態の半導体集積回路は、クロック信号生成部と、クロック波形整形部と、複数の機能ブロックとを有する。クロック信号生成部は、所定の周波数のクロック信号を生成する。クロック波形整形部は、クロック信号生成部で生成されたクロック信号と立ち上がりエッジの位相が同一で、かつ立ち下がりエッジの位相が異なる複数のクロック信号を生成する。複数の機能ブロックは、それぞれがクロック波形整形部で生成された複数のクロック信号のいずれかで動作する複数のフリップフロップを有する。

(もっと読む)

スイッチングドライバ回路

【課題】ディスクリート部品を用いることなく、パルス時間が長く、しかも、電圧変動が大きいノイズを確実に除去可能とする。

【解決手段】

入力信号の立ち上がり、立ち下がりを検出し、エッジ検出信号を出力するエッジ検出回路101と、入力信号を所定シフト時間t1シフトして出力するシフトレジスタ回路106と、エッジ検出回路101のエッジ検出信号の入力時点から所定入力時間t2経過後にカウントアップ信号を出力するカウンタ回路102と、シフトレジスタ回路106の出力信号を、カウンタ回路102のカウントアップ信号に同期して出力するDFF回路103と、DFF回路103の出力信号を外部へ出力する出力回路104と、シフトレジスタ回路106とカウンタ回路101のクロック信号を生成、出力する発振回路105とを具備してなり、所定入力時間t2に満たない入力信号が出力されないようになっている。

(もっと読む)

同期信号発生回路

【課題】 PWM信号からその同期信号を発生する。

【解決手段】 三角波発生回路101は、PWM信号PWMINの立ち上がりエッジおよび立ち下がりエッジの各々を検出する度に、先行して開始した三角波信号の発生と並行して三角波信号を発生する手段であり、立ち上がりエッジまたは立ち下がりエッジの検出後、三角波信号を基準レベルから一定の時間勾配で変化させ、その後、同種のエッジが検出された以降、同じ大きさの逆方向の時間勾配で三角波信号を変化させる。同期信号発生部160は、三角波発生回路101が発生する三角波信号TRIA、TRIB、TRICに基づいてPWM信号PWMINに同期した同期信号SYNCを発生する手段であり、相前後して発生を開始した2個の三角波信号の大小関係が逆転したとき、同期信号SYNCのレベルを反転させ、先行して発生を開始した三角波信号を基準レベルに初期化する。

(もっと読む)

クロック再生装置および電子機器

【課題】受信データ信号のエッジ位置変動が生じたとしても的確にエッジ検出を行うことが可能で、転送レートの高速化および低消費電力化を実現することが可能なクロック再生装置および電子機器を提供する。

【解決手段】ゲーティング信号生成部130Bは、位相判定部120Bの位相判定信号に応じて、エッジ検出部110の検出結果により立ち上がりエッジ検出を示す信号または立ち下がりエッジ検出を示す信号のいずれか一方の信号を第1のゲーティング信号として、他方の信号を受信データ信号の周期の半周期分を遅延させて上記第2のゲーティング信号として生成し、発振器140Bは、位相が第1のゲーティング信号SGT10および第2のゲーティング信号SGT11によって制御され、受信データ信号RDTに同期したクロック信号CLKを出力する。

(もっと読む)

半導体集積回路装置及び電源システム

【課題】パワースイッチをオンとする際に発生する電源ノイズが許容値を超えないようにし、かつ、内部回路に与える電源電圧の立ち上がり時間を短縮することができるようにした半導体集積回路装置を提供する。

【解決手段】信号処理回路15に対する電源投入時に、パワースイッチをなすNMOSトランジスタ21−1〜21−4、22−1〜22−4のうち、まず、NMOSトランジスタ21−1〜21−4をオンとする。その後、信号処理回路15が出力端子20−1に出力する出力信号OUTの電圧変化を検出し、電源ノイズがピーク値に達したことが検出されると、NMOSトランジスタ22−1〜22−4をオンとする。

(もっと読む)

プログラマブルデュアルエッジトリガードカウンター

【課題】出力クロック信号のジッターを低減し、デューティサイクル分解能を改善するための回路の提供。

【解決手段】最小のジッターを備えたクロック信号を合成するためのカウンターは、出力クロックの立ち上がりエッジを入力クロック信号の立ち上がりエッジまたは立ち下がりエッジによりトリガーしなければならないかどうかを決定するために、さらに、出力クロックの立ち下りは、入力クロック信号の立ち下りの立ち上がりエッジまたは立ち下りによりトリガーしなければならないかどうかを決定するために進行中のカウントを分析する。カウンターはM/N:Dカウンターとして実施してもよい。このカウンターにおいて、位相アキュムレーターは所定の値と比較され、出力クロック信号の立ち上がりエッジおよび立ち下りを選択する。

(もっと読む)

半導体装置

【課題】高速なクロックを必要とせずに、時間分解能を向上させたデジタルPWM制御を実現できる半導体装置を提供する。

【解決手段】複数段の第1遅延素子を有し、これら第1遅延素子に印加される制御電圧に応じて発振周波数が制御される電圧制御型クロック発生回路と、直列に接続された複数段の第2遅延素子を有する遅延回路と、複数段の第2遅延素子がそれぞれ出力するパルス信号の中から1つを選択する選択回路と、を備え、第1遅延素子と第2遅延素子とは同じ半導体基板に形成された同じ構成の遅延素子であり、第2遅延素子の遅延量は制御電圧に応じて調整される。

(もっと読む)

モニタ回路及び電力低減システム

【課題】LSIテスト時においても選別用のモニタリングを行うことができると共に、小さな面積で簡便な構成によりモニタ可能なモニタ回路を提供すること。

【解決手段】モニタ回路は、クロック信号39に同期して入力信号を取り込むフリップフロップ回路32と、クロック信号40に同期して入力信号を取り込むフリップフロップ回路34と、フリップフロップ回路34の出力信号を受ける論理回路37と、クロック信号40に同期して論理回路37の出力信号を取り込むフリップフロップ回路35とを含み、クロック信号40の立ち上がりエッジ位置を調整し、フリップフロップ回路32の出力信号とフリップフロップ回路35の出力信号とが所定の組合せとなったときの、調整したクロック信号40の立ち上がりエッジ位置とクロック信号39の立ち上がりエッジ位置とに基づいてチップの性能を判別する。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】クロックのデューティ検出において、半導体メモリ装置内のプロセス、電圧レベル、及び温度などによる環境変数の変化によって発生するオフセットを除去するための初期測定動作を行うことができる回路を提供すること。

【解決手段】本発明に係る半導体メモリ装置は、初期測定動作時、共通クロックの遷移時点に対応する2つの検出パルスを生成するクロックエッジ検出部100Bと、前記2つの検出パルスを比較し、その結果を出力するデューティ検出部200Bと、前記初期測定動作時、デューティ検出部200Bから出力された比較結果に基づいて、デューティ検出部200Bを制御するコードカウンタ300とを備える。

(もっと読む)

信号生成装置、フィルタ装置、信号生成方法およびフィルタ方法

【課題】信号生成装置、フィルタ装置、信号生成方法およびフィルタ方法を提供すること。

【解決手段】信号レベルが第1のレベルと第2のレベルの間で遷移し、各々が同一の周波数および所定の位相の差分を有する複数の基礎信号であって、任意の基礎信号の信号レベルが第1のレベルである期間、および該任意の基礎信号に対して前記所定の位相遅れを有する次の基礎信号の信号レベルが第1のレベルである期間が重複する複数の基礎信号を生成する多相発振部と、前記各基礎信号の第1のレベルから第2のレベルへの遷移時点を、前記各基礎信号の前記次の基礎信号の第2のレベルから第1のレベルへの遷移時点以前に変化させてパルス信号を生成する遷移時点可変部300と、を備える信号生成装置。

(もっと読む)

半導体集積回路

【課題】消費電流をあまり増加させることなく、トリミング用保持回路の内容を適時にリフレッシュすることができる半導体集積回路を提供する。

【解決手段】この半導体集積回路は、製造後にトリミングを必要とする回路ブロックを内蔵した半導体集積回路であって、回路ブロックをトリミングするために用いられるトリミングデータを格納する格納回路と、格納回路から読み出されたトリミングデータを保持する保持回路と、保持回路に保持されているトリミングデータの変化を検出して検出信号の論理レベルを変化させる検出回路と、検出回路から出力される検出信号の論理レベルが変化したときに、格納回路から読み出されるトリミングデータによって、保持回路に保持されているトリミングデータを更新するリフレッシュ回路とを具備する。

(もっと読む)

半導体集積回路装置及び制御システム

【課題】パルス波形の立ち上がり時間と立ち下がり時間とを独立して測定することが可能な半導体集積回路装置を提供することを目的とする。

【解決手段】被測定セルMCと波形整形セルWCとが直列に接続された回路部が複数リング状に接続されたリングオシレータを備え、各々の波形整形セルは同一のリセットノードNDに共通接続されており、リセットノードが第1のレベルにあるとき全ての波形整形セルはリセット状態になり、リセットノードが第2のレベルにあるとき波形整形セルはそれぞれ前段の被測定セルからの出力を後段に伝播する伝播状態になり、リセット状態と伝播状態とが交互に切り替わることを特徴とする。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

パルス発生回路

【課題】dv/dt過渡信号による誤動作を防止したパワーデバイスの駆動回路を実現する半導体装置において、試験用にオン信号とオフ信号とを同時に発生させることのできるパルス発生回路を実現する。

【解決手段】第1の論理値および上記第1の論理値と排他的関係にある第2の論理値の間でレベル遷移する第1の入力信号が入力され、さらに第2の入力信号または上記第2の入力信号に加えて第3の入力信号も入力され、上記第1の入力信号が上記第1の論理値から上記第2の論理値へとレベル遷移する際に第1のパルス(オン信号)を出力し、上記第1の入力信号が上記第2の論理値から上記第1の論理値へとレベル遷移する際に第2のパルス(オフ信号)を出力し、上記第2または第3の入力信号が入力された場合には、上記第1および第2のパルスを同時に出力する。

(もっと読む)

エッジパルス生成回路

【課題】 入力信号が劣化していても正常動作を行い、エッジパルス幅の変動が小さく、実装基板の面積やレイアウトに影響を与えないエッジパルス生成回路を提供する。

【解決手段】 入力端子と、出力端子と、入力信号の1ビット以下の遅延値をもつ遅延素子1aと、差動増幅器3とを備え、入力端子を遅延素子1aの入力側と差動増幅器3の正側入力に接続し、遅延素子1aの出力側を差動増幅器3の負側入力に接続する。前記遅延素子1aはインダクタ素子Lと容量素子CのL型回路のn段直列接続により構成し、かつ該遅延素子1aは差動増幅器3と同じ集積回路上に形成する。

(もっと読む)

1 - 15 / 15

[ Back to top ]