Fターム[5J039HH17]の内容

パルスの操作 (9,993) | パターン監視(パルス列) (332) | 時間計測 (83) | 双安定回路によるもの (12)

Fターム[5J039HH17]に分類される特許

1 - 12 / 12

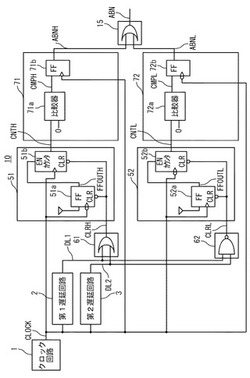

クロック異常検出回路

【課題】クロック異常を検出する精度を向上させる技術を提供する。

【解決手段】被検査クロックを遅延させる第1の遅延回路の出力と第2の遅延回路の出力よりLow期間を決める。定められたLow期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。第1の遅延回路の出力と第2の遅延回路の出力よりHigh期間を決める。定められたHigh期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。Low期間の異常とHigh期間の異常を統合する。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

パルス検出装置及びパルス検出方法

【課題】パルス信号を高精度に検出すること。

【解決手段】パルス検出装置1は、所定期間に中間電位を含むパルス信号を検出する。また、パルス検出装置1は、パルス信号の中間電位を、ローレベル又はハイレベルに固定する信号固定手段を備えている。さらに、信号固定手段は、パルス信号が入力される入力信号線に接続されたプルダウン抵抗9又はプルアップ抵抗であるのが好ましい。なお、パルス検出方法は、パルス信号の中間電位を、ローレベル又はハイレベルに固定する信号固定工程を含んでいる。

(もっと読む)

電子回路、情報再生装置

【課題】 セットアップ違反に対するより一般的な検出技術を提供する。

【解決手段】 外部からの入力データを受ける第1のフリップフロップと、前記入力データを受けるラッチと、このラッチの出力と前記第1のフリップフロップの出力との排他的論理和を入力する第2のフリップフロップとを備えた電子回路。また前記第1のフリップフロップの出力を入力とし前記第2のフリップフロップの出力に基づく通知信号を抑制信号入力として用いる電子回路を具備した情報再生装置。

(もっと読む)

速度判定方法、速度判定回路および速度判定装置

【課題】伝送速度の判定を高速に行う。

【解決手段】入力端子1への入力信号に含まれるプリアンブル信号のパターン周期の整数倍に相当する遅延差をもつ2つの信号を生成する遅延素子2,3と、該遅延素子2,3から出力する前記2つの信号の論理を比較する一致検出回路4と、該一致検出回路4の出力信号を積分する積分回路6と、該積分回路6で得られた信号を閾値Vrefと比較して判定結果を出力する比較回路7とを備える。

(もっと読む)

モニタ回路及び電力低減システム

【課題】LSIテスト時においても選別用のモニタリングを行うことができると共に、小さな面積で簡便な構成によりモニタ可能なモニタ回路を提供すること。

【解決手段】モニタ回路は、クロック信号39に同期して入力信号を取り込むフリップフロップ回路32と、クロック信号40に同期して入力信号を取り込むフリップフロップ回路34と、フリップフロップ回路34の出力信号を受ける論理回路37と、クロック信号40に同期して論理回路37の出力信号を取り込むフリップフロップ回路35とを含み、クロック信号40の立ち上がりエッジ位置を調整し、フリップフロップ回路32の出力信号とフリップフロップ回路35の出力信号とが所定の組合せとなったときの、調整したクロック信号40の立ち上がりエッジ位置とクロック信号39の立ち上がりエッジ位置とに基づいてチップの性能を判別する。

(もっと読む)

グリッチに備えるセルフタイマ回路の強化

グリッチに対する自己クロック回路を強化するための複数の技術が開示されている。グリッチフィルタが、デジタル設計の同じ場所に設けられている。ある実施例では、グリッチフィルタが動的に同調可能である。一実施例では、入力が出力によってロックアウトされる。差動信号のための回路のように、コード符号を見積もるための方法が与えられている。 (もっと読む)

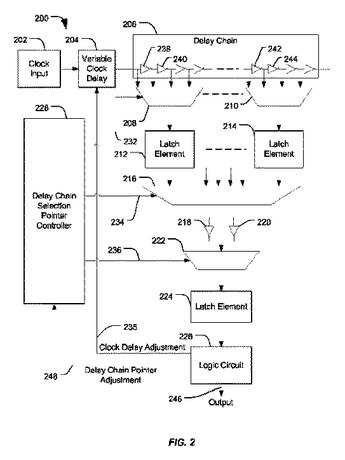

クロック・ジッタを測定する回路装置および方法

一実施形態では、回路装置の遅延チェーンにおいてクロック信号を受信すること、及び、該遅延チェーン内の選択される点において該クロック信号の値を決定すること、を含む方法が開示される。該方法は又、該値が該クロック信号のエッジの検出を示さない場合には、該選択される点を調整することを含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】第三者による不正な攻撃によって故障動作を引き起こされた場合でも、故障動作を検出し、回路動作を停止することが可能となるような半導体装置を提供する。

【解決手段】複数のフリップフロップを含む信号処理回路を有する半導体装置において、前記信号処理回路は、フリップフロップの入力信号を入力としパリティデータを生成する第1のパリティ生成回路と、前記第1のパリティ生成回路の出力をラッチするための、パリティ格納回路と、フリップフロップの出力信号を入力としパリティデータを生成する第2のパリティ生成回路と、前記パリティ格納回路の出力と第2のパリティ生成回路の出力とを比較し、不一致の場合に異常検出信号を出力するパリティ比較回路を備える。

(もっと読む)

デューティ検出回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】入力データDinと、該入力データDinと周波数および位相が同期したクロックCKとを入力とし、前記入力データDinのデューティの100%からの差分δを表す信号Errを、前記入力データDinに遷移が生じた時だけ出力する。前記信号Errは、前記入力データDinのデューティの100%からの差分δに対応する時間を単位時間Tに対して増減した時間幅のパルス信号である。

(もっと読む)

クロック生成回路、クロック選択回路、及び半導体集積回路

【課題】 PLL回路から出力される異常波形のクロックにより他の機能回路が誤動作すること。

【解決手段】 クロック生成回路50は、クロックCL1に同期したクロックCL2を出力するPLL回路11と、クロックCL1又はクロックCL2を出力するセレクタ14と、PLL回路11からのクロックCL2で異常波形のパルスが検出されたとき、クロックCL2に代えてクロックCL1を出力させる切替信号をセレクタ14に出力する切替信号生成回路13と、切替信号に基づいてセレクタ14がクロックCL2からクロックCL1に出力クロックを切り替えた後、異常波形のパルスがセレクタ14に入力されるように、PLL回路11からのクロックCL2を遅延させる遅延回路12と、を備える。

(もっと読む)

半導体記憶装置の同期モード検出回路及び方法

【課題】半導体記憶装置の同期モード検出回路及び方法に関するものであり、クロックが入力されれば同期モード信号をイネーブルにし、クロックが入力されなければ同期モードをディセーブルにすることによって、同期モードと非同期モードとを区分することができる半導体記憶装置の同期モード検出回路及び方法を提供する。

【解決手段】半導体記憶装置の同期モード検出回路は、有効アドレス信号とクロックを組み合わせて基準信号を生成する第1信号組合部と、前記基準信号をラッチする第1ラッチ部と、前記第1ラッチ部の出力信号と前記クロックを組み合わせて検出パルス信号を生成する第2信号組合部と、前記有効アドレス信号のイネーブル有無に応じて前記検出パルス信号の駆動を制御する制御部と、前記制御部の制御により前記検出パルス信号を駆動する駆動部と、前記駆動部で駆動された信号をラッチし、同期モード信号を出力するラッチ部とを含む。

(もっと読む)

1 - 12 / 12

[ Back to top ]