Fターム[5J055AX51]の内容

Fターム[5J055AX51]の下位に属するFターム

スイッチがオフしている時 (34)

スイッチがオンしている時 (89)

スイッチが信号を受け変化するまで (42)

オフからオン方向に変化するとき (148)

オンからオフ方向に変化するとき (105)

電源の立ち上がり (113)

電源の不安定時、瞬断時、遮断時 (54)

状態切り換え時、電源切り換え時 (38)

初期化時、再設定時 (11)

Fターム[5J055AX51]に分類される特許

1 - 4 / 4

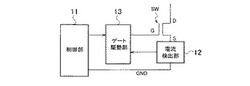

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

パルス発生回路

【課題】電源オフした直後に電源を再投入しても正常にパルス生成動作を再開できるようにすること。

【解決手段】このパルス発生回路は、第1のDフリップフロップ回路11のセット端子及びリセット端子をそれぞれコンデンサC11,C12を介してグラウンド又は電源に接続し、第1のDフリップフロップ回路11のQ出力端子とセット端子間及びQバー出力端子とリセット端子間にそれぞれ第1の抵抗R11,R12を接続し、前記セット端子、リセット端子、Q出力端子又はQバー出力端子のうちのいずれかの端子とグラウンド間に第2の抵抗RGを接続している。また、第1のDフリップフロップ回路11のQ出力端子を第2のDフリップフロップ回路20のクロック端子に接続し、第2のDフリップフロップ回路20のデータ端子及びセット端子を電源に接続し、第2のDフリップフロップ回路20のQバー出力端子とリセット端子間に第3の抵抗R2を接続した。

(もっと読む)

半導体装置

【課題】複数電源で動作する半導体装置のパワーオンリセットに際して、セット部品のコスト低減と誤動作防止を図る。

【解決手段】ADコンバータ2は、AD変換制御信号Scのアサートにより第2の電源電圧VbのAD変換を行い、AD変換値が設定値に達したときに一致信号Seをアサートする一方、AD変換制御信号Scのネゲートにより通常動作モードで入力信号SinのAD変換を行う。リセット制御回路4は、リセット入力端子電圧Vrの上昇に伴うリセット入力信号Srのアサートに同期してAD変換制御信号Scをアサートし、一致信号Seのアサートに同期してAD変換制御信号Scをネゲートしかつ内部リセット信号Snをアサートして、第2の電源電圧Vbより高電位の第1の電源電圧Vaで駆動される第1の内部回路10aと第2の電源電圧Vbで駆動される第2の内部回路10bをリセット解除する。

(もっと読む)

リセット回路

【課題】 パワーダウン時のパワーダウンリセット信号のタイミング制御を容易にし、繰り返し電源をオン/オフした時の起動不良を防ぐことを課題とする。

【解決手段】 リセット回路は、電源検出回路とパワーダウン検出回路と出力回路とを有する。電源検出回路は、パワーオン及びパワーダウン時に電源電圧(VDD)に応じた第1の電圧が第1のしきい値より大きいと第1の信号を出力し、低いと第2の信号を出力する。パワーダウン検出回路は、パワーダウン時に第2の信号が出力された後、電源電圧(VDD)に応じた第2の電圧が第2のしきい値より小さくなると第3の信号を出力する。出力回路は、パワーオン時に第1の信号が出力されるとローレベルからハイレベルに変化するパワーオンリセット信号(POR)を出力し、パワーダウン時に第3の信号が出力されるとハイレベルからローレベルに変化するパワーダウンリセット信号(POR)を出力する。

(もっと読む)

1 - 4 / 4

[ Back to top ]