Fターム[5J055AX52]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | 課題の発生する時、注目している時 (638) | スイッチがオフしている時 (34)

Fターム[5J055AX52]に分類される特許

1 - 20 / 34

スイッチ

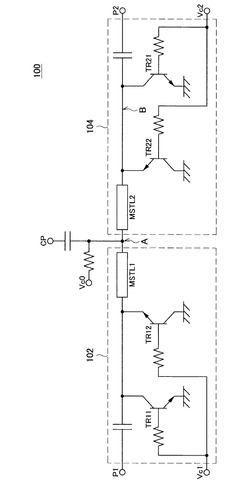

【課題】高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することが可能なスイッチを提供する。

【解決手段】高周波信号が入力される入力端子と、高周波信号が出力される第1出力端子との間に接続され、入力される高周波信号を第1出力端子から選択的に出力させる第1スイッチング部と、入力端子と、入力された高周波信号が出力される第2出力端子との間に接続され、入力端子に入力される高周波信号を第2出力端子から選択的に出力させる第2スイッチング部とを備え、第1スイッチング部、第2スイッチング部それぞれは、信号線上に設けられるインピーダンス変成器と、エミッタが接地され、コレクタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタと、コレクタが接地され、エミッタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタとを備えるスイッチが提供される。

(もっと読む)

駆動回路および宅側装置

【課題】光信号を送信するための発光素子の駆動に寄与しない無効電流を低減することが可能な駆動回路および宅側装置を提供する。

【解決手段】駆動回路52は、光信号を送信するための発光素子LDを含む発光回路75における発光素子LDにバイアス電流を供給するためのバイアス電流供給回路68と、送信すべきデータの論理値に応じた大きさの変調電流を発光素子LDに供給するための変調電流供給回路63とを備える。変調電流供給回路63は、データの論理値に応じて、発光素子LDに電流を供給するか否かを切り替えるための差動駆動回路41と、差動駆動回路41の差動出力間に接続された終端抵抗とを含む。差動駆動回路41および発光回路75は直流結合されており、差動駆動回路41が発光素子LDに供給する上記電流の電源は発光回路75から供給される。

(もっと読む)

2線式交流スイッチ

【課題】2線式交流スイッチの低消費電力化を実現する。

【解決手段】

交流電源と負荷とを結ぶ電路に挿入される2線式交流スイッチであって、スイッチ端子S1、S2と、スイッチ端子間のオンオフを制御するためのゲート端子G1、G2と、基板端子Subとを有し、スイッチ端子間に双方向に電流を流すことができ、スイッチ端子S1が交流電源1に接続され、スイッチ端子S2が負荷2に接続される半導体スイッチからなるメインスイッチ3と、メインスイッチの基板端子Subを接地するかフローティングにするかを切り替えるサブスイッチ9と、を備える。

(もっと読む)

半導体素子制御装置

【課題】駆動用半導体素子が意図せずに導通することを防止できる半導体素子制御装置を提供する。

【解決手段】駆動用トランジスタTr11は、一対の直流電源線13、14間に直流モータ12とともに直列に接続される。抵抗素子R13は、直流電源線13と駆動用トランジスタTr11のゲート端子との間に接続される。コンデンサC11および開路用トランジスタTr14の直列回路は、駆動用トランジスタTr11のゲート端子と直流電源線14との間に接続される。駆動制御回路15は、通常状態に設定されると、開路用トランジスタTr14をオンし、制御用トランジスタTr12、Tr13を通じて駆動用トランジスタTr11の導通状態を制御する。駆動制御回路15は、制御用トランジスタTr12、Tr13の双方がオフのとき、開路用トランジスタTr14をオフする。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

ゲートドライブ回路

【課題】簡単な構成で、ワイドバンドギャップ半導体からなるスイッチ素子を駆動するゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体からなるスイッチ素子Q1であって、ドレインとソースとゲートとを有し、ゲートをドライブする信号とゲートとの間にコンデンサと抵抗の並列接続回路を介して接続され、オフ信号期間は、スイッチ素子Q1のゲート・ソース間を短絡するスイッチSW1とを備えることを特徴とするゲートドライブ回路。

(もっと読む)

アナログスイッチ回路

【課題】高位電源の電位より高い又は低位電源の電位より低い伝送信号を、MOSトランジスタを用いたアナログスイッチにより好適に阻止可能なアナログスイッチ回路を提供する。

【解決手段】第1のアナログスイッチ11と、第1のアナログスイッチ11の制御端子11cに至る制御信号経路21上に設けられた第2のアナログスイッチ12と、伝送信号の電位が所定の高電位レベルより高い場合又は伝送信号の電位が所定の低電位レベルより低い場合に第1のアナログスイッチ11の一方の入出力端子11aと制御端子11cとを短絡するよう構成された第3のアナログスイッチ13と、を備え、第2のアナログスイッチ12は、少なくとも第3のアナログスイッチ13が第1のアナログスイッチ11の一方の入出力端子11aと制御端子11cとを短絡する場合に、所定のレベルの電位が印加されてオフするようMOSトランジスタを用いて構成される。

(もっと読む)

スイッチング駆動回路

【課題】オンオフ動作させる外部機器のEMIによる誤作動を確実に防ぐスイッチング駆動回路を提供する。

【解決手段】スイッチング駆動回路1は、LED4をオンオフ動作させるスイッチ素子であるpMOSトランジスタT1と、pMOSトランジスタT1のゲートソース間の抵抗10と、抵抗10に制御電流を供給するnpnトランジスタT4を含むカレントミラー回路と、抵抗10及びnpnトランジスタT4との間に設けられる遮断回路としてのnMOSトランジスタT5とを備える。制御信号がLED4を消灯制御するローレベルLのときにnMOSトランジスタT5を同時にオフすることで、EMIの影響により抵抗10から流れ込出す電流を遮断する。これにより、LED4の誤点灯を確実に防ぐ。

(もっと読む)

電子回路

【課題】 スイッチ回路におけるリーク電流を低減すること。

【解決手段】 本電子回路は、一端がそれぞれの入力端子AN1〜ANnに接続され、他端が共通の出力端子OUTに接続された複数のスイッチ回路SW1〜SWnであって、入力端子ANiと出力端子OUTとの間に直列に接続された第1スイッチSWia及び第2スイッチSWibを含む複数のスイッチ回路SW1〜SWnと、第1スイッチSWiaと第2スイッチSWibとの中間に位置する中間ノードMiに対し、出力端子OUTの電圧を供給する電圧供給回路20と、を備えることを特徴とする。

(もっと読む)

外部アダプター

【課題】 消費電力の少ない回路によって2線式電子スイッチのON/OFF状態を的確に検出できる外部アダプターを提供する。

【解決手段】 外部アダプター11は、電子スイッチ1に接続される2つの入力端子12,13を備える。分圧抵抗器R1,R2は入力電圧を分圧し、分圧抵抗器R2の両端電圧に基づいて、フォトカプラー14が電子スイッチ1のON/OFF状態を検出する。インピーダンス調整回路19は、入力端子12,13間に介装された調整抵抗器R3、フォトカプラー14の出力に応答して調整抵抗器R3への通電/遮断を切り替えるトランジスタQ1およびフォトMOSリレー18を備え、アダプター11の入力インピーダンスを電子スイッチ1の接点導通状態で相対的に高く、接点非導通状態で相対的に低く調整する。

(もっと読む)

スイッチ回路

【課題】リーク電流がスイッチ回路に接続される回路に影響を与えることを抑制することが可能なスイッチ回路の提供。

【解決手段】第1の電位と第2の電位の間の接続状態をオンオフする第1のトランジスタと、該第1のトランジスタのドレインにソースが接続され、前記第1のトランジスタと略同一の特性を有する第2のトランジスタとを備え、前記第1のトランジスタをオフした時に、前記第1のトランジスタのゲート−ソース間電圧VGS1と、前記前記第2のトランジスタのゲート−ソース間電圧VGS2が略等しくなることを特徴とするスイッチ回路。

(もっと読む)

半導体集積回路

【課題】 ゲート酸化膜の信頼性を維持しながら、待機時のリーク電流を抑制でき、回路面積の増加を最小限にでき、欠陥を確実に検出することができる半導体集積回路を実現する。

【解決手段】 論理回路10と電源電圧Vddの供給端子との間にスイッチング回路20を設ける。動作時に、スイッチング回路20のトランジスタMP0のゲートに0Vの電圧を印加し、チャネル領域に電源電圧Vddと同じかまたは僅かに低いバイアス電圧VBを印加することで、トランジスタMP0のしきい値電圧を低くし、その電流駆動能力を大きくする。待機時にトランジスタMP0のゲートに電源電圧Vddと同じ電圧を印加し、ソースに電源電圧より低い電圧を印可し、チャネル領域に電源電圧Vddと同じかまたはそれより高いバルクバイアス電圧VBを印加し、トランジスタMP0のドレイン電流を最少化することにより、論理回路10の電流経路を遮断し、リーク電流の発生を抑制する。

(もっと読む)

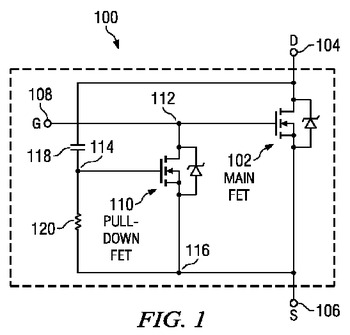

ゲート・プルダウンを備えたMOSFET

スイッチングタイプのDC−DCパワー・コンバータのMOSFETメインスイッチ・トランジスタ(102)のドレインとゲートとの間にプルダウンMOSFET(110)が結合される。プルダウンMOSFET(110)のゲートは、キャパシタ118によってメインスイッチ・トランジスタ(102)のドレインに結合され、抵抗(120)によってメインスイッチ・トランジスタ(102)のソースに接続される。プルダウンMOSFET(110)は、メインスイッチ・トランジスタ(102)にわたる電圧降下への容量性結合によって動作され、ミラー効果によるメインスイッチ・トランジスタ(102)の意図しないターンオンを避ける又は低減するため、メインスイッチ・トランジスタ(102)のゲートをそのソース電位にまたはその近辺に保持するために用いられ得る。

(もっと読む)

(もっと読む)

スイッチ回路

【課題】オン時の信号歪みが少なく、かつオフ時の抵抗を高くして確実に信号を遮断することができるスイッチ回路を提供する。

【解決手段】第1の端子から入力された電圧信号と切替電圧が入力される増幅器の入力端子と出力端子を結ぶ経路の途中およびこの増幅器の出力側に第1、第2のダイオードを配置し、また第2の端子が接続される経路で、第2のダイオードが接続されていない経路中にスイッチ素子を配置して、このスイッチ素子のオンオフを、第2のダイオードと同じように制御するようにした。信号歪みが少なく、かつスイッチ素子を用いて信号を遮断するので、確実に信号を遮断できる。

(もっと読む)

半導体集積回路およびそれを内蔵した高周波モジュール

【課題】アンテナスイッチの電圧生成回路へのRF送信信号の供給に際し、RF送信出力信号の高調波成分のレベルの増大を軽減する。

【解決手段】半導体集積回路200は、電圧生成回路100と送信スイッチ101と受信スイッチ102を有するアンテナスイッチを含む。送信端子203と入出力端子201の間の送信スイッチ101のトランジスタ211のオン・オフは送信制御電圧V_Txcにより制御され、入出力端子201と受信端子205の間の受信スイッチ102のトランジスタ215a〜dのオン・オフは受信制御電圧V_Rxcによって制御される。電圧生成回路100の高周波信号入力端子10は送信端子203に接続され、DC出力端子104から生成される負電圧のDC出力電圧Voutが受信スイッチ102のトランジスタ215a〜dのゲート制御端子に供給可能とされる。

(もっと読む)

マルチプレクサ

【課題】マルチプレクサの出力信号波形の歪みを低減する。また、大型化を抑制する。

【解決手段】マルチプレクサ1は、第1の容量素子を介して第1の入力信号を受けるCMOSスイッチ101と、第2の容量素子を介して第2の入力信号を受けるCMOSスイッチ102と、クランプ回路30と、クランプ回路40と、を備える。クランプ回路30は、CMOSスイッチ101を導通させる場合には、第1の入力信号に同期してVclp1で第1の入力信号をクランプし、CMOSスイッチ102を導通させる場合には、第2の入力信号に同期してVclp1で第2の入力信号をクランプする。クランプ回路40は、CMOSスイッチ101を導通させる場合には、第2の入力信号を検出しつつ検出された第2の入力信号をVclp2に近づけるようクランプし、CMOSスイッチ102を導通させる場合には、第1の入力信号を検出しつつ検出された第1の入力信号をVclp2に近づけるようクランプする。

(もっと読む)

スイッチ回路

【課題】シリーズラインの電子スイッチがオフのときのアイソレーション特性を向上させることができ、かつ、高速動作するスイッチ回路を提供する。

【解決手段】入力端子1と出力端子2との間に接続される第1電子スイッチ4と、第1電子スイッチ4がオンするときに互いにオフし、第1電子スイッチ4がオフするときに互いにオンする第2電子スイッチ8と機械スイッチ9とが並列接続されたものであり、入力端子1と出力端子2との間とグランド5との間に接続されるシャント回路7とを有する構成とする。これにより、第1電子スイッチ4がオフしている間、シャント回路7の第2電子スイッチ8および機械スイッチ9をオンすることでリーク電流をグランド5に流す。また、第1電子スイッチ4を高速スイッチングすることでスイッチ回路を高速動作させる。

(もっと読む)

トランジスタスイッチ回路、サンプルホールド回路

【課題】オンオフの特性変化の確実性を向上することができるトランジスタスイッチ回路およびこれを用いたサンプルホールド回路を提供すること。

【解決手段】ゲート・ソース間電圧がゼロのときにチャネルが形成されているMOSトランジスタと、このMOSトランジスタのゲートに接続された、該ゲートにMOSトランジスタをオフ状態に移行させる電圧を供給する電圧供給部とを具備する。

(もっと読む)

半導体スイッチ回路

【課題】 半導体スイッチ回路に要求される挿入損失特性、ハンドリングパワー特性、歪み特性を損なわず、高いアイソレーション特性を実現することができる半導体スイッチ回路を提供する。

【解決手段】 2つの入出力端子間に、直列接続した複数の電界効果トランジスタで構成される第1のスイッチ素子と、一方の入出力端子と接地との間に、直列接続した複数の電界効果トランジスタで構成される第2のスイッチ素子とを備え、第1のスイッチ素子及び第2のスイッチ素子の接続点と第2の入出力端子との間に、1つの電界効果トランジスタで構成される第3のスイッチ素子を備える。

(もっと読む)

電流検出装置

【課題】負荷に対する電圧を制御するために電界効果トランジスタを使用した場合に、電界効果トランジスタのドレイン−ソース間のドレイン電流を高精度で検出する。

【解決手段】増幅アンプ15の入力端子15aおよび15bと、ワイドギャップ半導体HFET11のドレインおよびソースとの間に、それぞれスイッチング素子としてFET16および17が設けられている。ワイドギャップ半導体のHFET11がオンしたのち、一定時間経過後、FET16および17のゲートをオンし、増幅アンプ15の入力端子間の電圧差で電流値を検出する。これにより、電流検出が必要な時のみスイッチング素子を制御して、HFET11ドレインおよびソースを増幅アンプへ接続することで、常時接続している場合と異なり、増幅アンプで発生する熱を抑制し、それに伴うオフセット電圧を抑制し、精度良く電流を検出できる。

(もっと読む)

1 - 20 / 34

[ Back to top ]