Fターム[5J055AX57]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | 課題の発生する時、注目している時 (638) | 電源の立ち上がり (113)

Fターム[5J055AX57]に分類される特許

1 - 20 / 113

電圧検出回路

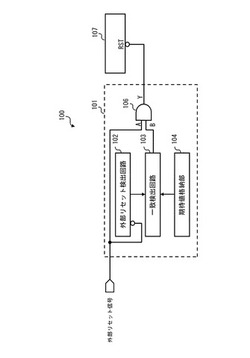

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】電源投入後から外部リセット信号が最初にアクティブになるまでの期間にリセット信号をアクティブにすることが可能なリセット信号生成回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路101は、外部リセット信号が最初にアクティブになったことを検出する外部リセット検出回路102と、外部リセット検出回路102の検出結果が、外部リセット信号が最初にアクティブになる前であることを示す場合、外部リセット信号に関わらずリセット信号をアクティブにする制御回路と、を備える。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

バンドギャップ基準電圧回路及びこれを用いたパワーオンリセット回路

【課題】バンドギャップ基準電圧回路100を確実に起動させることができる。

【解決手段】電源電圧がpMOSトランジスタP1のゲート電圧の閾値に到達する前には、pMOSトランジスタP6により電源VddとpMOSトランジスタP4のソース端子との間を開放させている。このため、電源電圧がpMOSトランジスタP1のゲート電圧の閾値に到達する前に、抵抗素子R3aによってコンデンサC1から電荷を放出させて、コンデンサC1のプラス電極の電位をpMOSトランジスタP4のゲート端子の電位の閾値よりも低くすることができる。電源電圧が上昇してpMOSトランジスタP6が電源VddとpMOSトランジスタP4のソース端子との間を接続すると、pMOSトランジスタP4がオンして、電源VddからpMOSトランジスタP6、P4を通してスタートアップ電流をnMOSトランジスタN1、N2のゲート端子に流すことができる。

(もっと読む)

リセット回路

【課題】マイコンのリセット端子をトランジスタによってグランドに接続することによりマイコンにリセットをかけるリセット回路において、リセット動作不能な電源電圧の領域を無くす。

【解決手段】リセット回路10は、マイコン11のリセット端子13を電源電圧(以下、VM)にプルアップする抵抗R1と、VMが所定値未満のときにトランジスタT1をオンしてリセット端子13を0Vにするリセット信号出力回路15とに加え、オンすることで抵抗R1の上流側にVMを供給するトランジスタT2と、抵抗R1の上流側とグランドとの間に接続された抵抗R2と、トランジスタT1がオン可能なVMの最低値(Vbe)より高く、上記所定値よりは低い電圧(Vbe+ダイオードD1のVf)を動作閾値電圧とし、VMがその動作閾値電圧未満である場合にトランジスタT2をオフさせておいて、マイコン11のリセットを確保する回路T3,D1,R3,R4とを備える。

(もっと読む)

スタートアップ回路

【課題】イネーブル等の制御信号を用いず、且つスタートアップ動作が完了した後は消費電流が極少なるスタートアップ回路を提供する。

【解決手段】2つの電流ルートの電流が0値で且つノードN11が高電位になる第1安定状態と、前記2つの電流ルートの電流が0値以外で同値になり且つノードN11が前記高電位よりも低い第1所定値になる第2安定状態をもつ対象回路のためのスタートアップ回路において、ノードN11の電位が第1所定値を超えているとき検出出力を出力するトランジスタMN21と、MN21が検出出力を出力するときバイアス電圧を生成するトランジスタMN23と、MN23でバイアス電圧が生成されるとノードN11の電位を低下させるトランジスタMN22とを備える。ノードN11の電圧が第1所定値に達すると、MN21が検出出力の出力を停止し、MN23がバイアス電圧の生成を停止し、MN22が動作を停止する。

(もっと読む)

半導体装置

【課題】電源投入時に、ノイズの影響により誤ってリセット信号が出力されることを防止できる半導体装置を提供すること。

【解決手段】半導体装置100は、レギュレータ11、第1のパワーオンリセット回路12、第2のパワーオンリセット回路13及び制御回路14を有する。レギュレータ11は、電源線VL11を介して電源VS11から供給される第1の電圧に基づいて、第1の電圧よりも小さい第2の電圧を生成する。第1のパワーオンリセット回路12は、電源投入後の第1の電圧が検出閾値Vt12まで上昇したことを検出し、第1のリセット信号R_12を出力する。第2のパワーオンリセット回路13は、電源投入後の第2の電圧が検出閾値Vt13まで上昇したことを検出し、第2のリセット信号R_13を出力する。制御回路14は、第1のリセット信号R_12及び第2のリセット信号R_13の論理積である第3のリセット信号R_Cを出力する。

(もっと読む)

スイッチングアンプ

【課題】 2つの出力素子の入力が共にハイレベルになり次に電源オン状態に移行する際に動作を開始することができないとい問題を解決する。

【解決手段】 電源制御手段16は、スイッチングアンプ10が電源オフ状態に移行する場合に、スイッチSWがオフ状態になり、コンデンサC102を強制的に放電させ、第2電源電圧V2に対する基準電位V3を強制的に低下させる。基準電位V3に対するロジック電源電圧Vddは、基準電位V3と同じだけ低下していくので、基準電位V3から見たロジック電源電圧Vddは固定される。定電流回路は、第2電源電圧V2に対する基準電位V3の低下に伴い、定電流Iを減少させ、第1の電流I1および第2の電流I2を減少させる。従って、基準電位V3から見たロジック電源電圧Vddが低下しないうちに、第1の電流I1、第2の電流I2を減少させ、パルス発生手段の動作を正常な状態で終了できる。

(もっと読む)

半導体装置

【課題】本発明は、第1状態と第2状態との二つの状態のうち、第1状態に初期化し、初期化した第1状態に対応する電位の信号を生成することが可能な半導体装置を提供する。

【解決手段】本発明は、“0”(第1状態)と“1”(第2状態)との二つの状態のうち、“0”に初期化し、初期化した“0”に対応する電位の信号Aを生成することが可能な半導体装置10である。半導体装置10は、並列に複数接続され、“0”と“1”との二つの状態を保持することが可能なフリップフロップ回路2と、複数のフリップフロップ回路2と接続し、複数のフリップフロップ回路2のうち、少なくとも一つのフリップフロップ回路2で保持する状態が“0”の場合、“0”に対応する電位の信号を生成し、出力するAND回路3とを備える。

(もっと読む)

電源電圧検出回路

【課題】簡単な構成で電源投入時にも精度よく電源電圧の状態を検出する。

【解決手段】第1スイッチ(122)と第2スイッチ(124)とは直列に接続されてスイッチ部を形成し、第1スイッチ(122)は、基準信号に基づいて開閉が制御される。判定信号生成回路(110)は、第1電源電圧(VDD)と第2電源電圧(VSS)とに基づいて電源電圧判定信号(VG)を生成し、第2スイッチ(124)は、電源電圧判定信号(VG)に基づいて開閉が制御される。第1負荷素子(126)は、第1電源電圧(VDD)とスイッチ部との間に直列に挿入される。スイッチ部は、基準信号(Vref)が所定の第1電圧を超え、電源電圧判定信号(VG)が所定の第2電圧を超えたとき回路を閉成して第1負荷素子(126)に電流を供給し、第1負荷素子(126)とスイッチ部との接続ノードから第1電源電圧(VDD)の状態を示す第1出力信号(VOUT)を出力する。

(もっと読む)

周波数入力モジュール

【課題】第1モジュールと第2モジュールが別電源で給電される周波数入力モジュールにおいて、第1モジュールへの給電が第2モジュールへの給電よりも遅れて起動する場合に、第1モジュールへの給電が安定化するまでの期間中、第1モジュールから第2モジュールへ渡される信号の演算を停止させることを可能とする周波数入力モジュールを実現する。

【解決手段】電源モジュールからの第1電源電圧で給電されて入力パルスを処理する第1モジュールと、前記電源モジュールからの第2電源電圧で給電されて前記第1モジュールからの出力パルスの複数個のパルス間隔情報とパルス数情報に基づき前記入力パルスの周波数を演算して出力する第2モジュールを具備し、起動時に前記第1電源電圧が前記第2電源電圧より所定時間遅れて立ち上がる周波数入力モジュールにおいて、

前記第1電源電圧が所定の安定値に達するまでの期間中、前記第2モジュールの演算機能を停止させるリセット信号を出力するリセット手段を備える。

(もっと読む)

パワーオンリセット回路

【課題】面積の小さいパワーオンリセット回路を提供する。

【解決手段】電源端子と接地端子との間に設けられる容量及び電流源と、容量と電流源の接続点を入力端子に接続するインバータと、を備えたパワーオンリセット回路に、電源電圧の立ち上がりを検出すると、容量をディスチャージするディスチャージ回路を設けた。ディスチャージ回路は、容量と電流源を備えているが、この容量の容量値は小さくて良いので、パワーオンリセット回路の面積が小さくなる。

(もっと読む)

リセット回路及び半導体集積回路

【課題】低電圧で動作可能なリセット回路を提供する。

【解決手段】リセット回路50Aは、Pチャネルの第1トランジスタ11を備え、第1電流i1が第1の値を超えると第1信号D1をアクティブとする第1回路10Aと、Nチャネルの第2トランジスタ21を備え、第2電流i2が第2の値を超えると第2信号D2をアクティブとする第2回路20Aと、電源電圧Vddの供給開始から、所定時間が経過した後に第3信号D3をアクティブとする第3回路30Aと、第1信号D1、第2信号D2、及び第3信号D3の全てがアクティブになるとリセット解除を指示するリセット信号RESを生成する論理回路40とを備える。

(もっと読む)

電源復帰検出回路

【課題】電圧比較器を用いることなく、電源遮断ブロックの電源復帰を検出する。

【解決手段】電源遮断ブロック1に配置された信号遅延回路11と、電源が常時供給される常時オンブロック9に配置された測定パターン生成回路13、測定パターン検出回路15及び遅延時間測定回路17を備えている。遅延時間測定回路17は、測定パターン生成回路13から送信された測定パターンが信号遅延回路11を介して測定パターン検出回路15に到達するまでの遅延時間を測定する。電源遮断ブロック1の電源が遮断状態から投入状態に切り替えられた後、上記遅延時間が信号遅延回路11の設計値に基づく所定の遅延量以内になったときに、電源遮断ブロック1の電源が復帰したと判断する。

(もっと読む)

リセット回路及び電子装置

【課題】本発明は、パワーオンした瞬間に生じる雑音を除去することができる静音制御回路及び該静音制御回路を有する電子装置を提供することを目的とする。

【解決手段】本発明に係る電子装置は、処理ユニット、静音制御回路、オーディオアンプ及びオーディオ出力インターフェースユニットを備え、前記オーディオアンプは、前記電子装置が生成するオーディオ信号を増幅し、且つ増幅されたオーディオ信号を前記オーディオ出力インターフェースユニットに出力し、前記処理ユニットは、静音制御信号を出力し、前記静音制御回路は、前記静音制御信号によって前記オーディオアンプを制御して静音状態と再生状態との間で切替させるメイン回路と、前記電子装置にパワーオンした瞬間、前記オーディオアンプの出力を接地により釈放させて、前記オーディオアンプと前記オーディオ出力インターフェースユニットとの間の通信を切る補助回路と、を備える。

(もっと読む)

半導体装置

【課題】従来よりも低消費電力かつ小面積であるとともに設計性のよいパワーオンリセット回路またはスタートアップ回路を備えた半導体装置を提供する。

【解決手段】半導体装置1は、出力部10と、第1および第2の電位設定部8,9とを備える。出力部10は、電源投入時に、中間電位ノードN1の電位に応じた制御信号RSを内部回路3に出力する。第1の電位設定部8は、第1の基準電位ノードVDDと中間電位ノードN1との間に接続された第1の導電型を有するエンハンスメント型の第1のMOSトランジスタEPを含む。第2の電位設定部9は、第2の基準電位ノードGNDと中間電位ノードN1との間に直列接続された第2の導電型を有するディプレッション型の複数の第2のMOSトランジスタDN1_〜DN_nを含む。複数の第2のMOSトランジスタDN1_〜DN_nの各々において、ソースとウェルとが互いに接続される。

(もっと読む)

パワーオンリセット回路

【課題】回路の消費電流を低減可能な、パワーオンリセット回路を提供すること。

【解決手段】抵抗分圧回路(R3,R4)によって得られた電源電圧VDDの検出電圧Vcが基準電圧Vrefを超えているとき、リセット解除信号を出力するコンパレータC2と、基準電圧Vrefよりも高い所定電圧を検出する第2の電圧検出回路D2と、第2の電圧検出回路D2によって前記の所定電圧が検出されているときに抵抗分圧回路(R3,R4)とコンパレータC2に流れる電流を遮断するスイッチM1,M2と、スイッチM1,M2によって電流が遮断されているときにリセット解除信号の出力を補償する補償回路とを備え、第2の電圧検出回路D2の消費電流を、抵抗分圧回路(R3,R4)とコンパレータC2との合計消費電流よりも低く設定した、パワーオンリセット回路。

(もっと読む)

半導体集積回路装置

【課題】

複数の電源を有する半導体集積回路装置において、複数の電源が半導体集積回路装置の外部、内部であるに関わらず、それら電源の立ち上げ順序に依存せずに各回路のオン状態を一意に制御するためのシーケンス制御信号を生成することができる半導体集積回路装置を提供する。

【解決手段】

半導体集積回路装置100は、第1電源VCC1で動作する第1電子回路120と、第2電源VCC2で動作する第2電子回路140と、第1電源VCC1および第2電源VCC2の電圧の大きさを所定の検知レベルで検出し、第1電子回路120のオン動作を制御するためのシーケンス制御信号PS1、および第2電子回路140の所期化を行うためのパワーオンリセット信号PORを生成するシーケンス制御回路180を備える。

(もっと読む)

半導体集積回路装置

【課題】電源投入手順によらずに安定した動作を行う入出力回路の制御を、回路規模の増大を抑え、チューニングが不要なデジタル回路のみで実現する集積回路を提供する。

【解決手段】信号発生器113で生成した信号を、レベルシフト回路111で電源電圧Vcc2の信号振幅へ変換する。次にVcc2の信号振幅に変換したものを、もう一度レベルシフト回路112で内部電源電圧Vcc1の信号振幅へ変換して、フィードバック信号を生成する。比較器114で信号発生器113が生成したオリジナルの信号と、2つのレベルシフトを経て生成された、フィードバック信号とを論理的に比較し、一致しない場合にはVcc2の電源が遮断されていると見なして、入出力回路115での不定伝播を防止するように制御を行う。

(もっと読む)

パワーオンクリア回路

【課題】電源電圧の立ち上がり状態の影響を受けないクリア信号を生成、出力するパワーオンクリア回路を提供する。

【課題の解決手段】パワーオンクリア回路は、電源の投入によってパルスを発生するパルス発生回路1と、発生したパルスを遅延して出力する遅延回路5と、遅延されたパルスが入力する縦続接続した2段のインバータ6,7と、遅延回路5の前段側の出力が入力する入力端子と1段目のインバータ6の出力が入力する入力端子とを有するNOR回路8とを備え、NOR回路8の出力を電源電圧の立ち上がり状態の影響を受けない第1のクリア信号とし、インバータ7の出力を電源電圧の立ち上がり状態に応じた第2のクリア信号とするものである。

(もっと読む)

1 - 20 / 113

[ Back to top ]