Fターム[5J055AX56]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | 課題の発生する時、注目している時 (638) | オンからオフ方向に変化するとき (105)

Fターム[5J055AX56]に分類される特許

1 - 20 / 105

負荷駆動装置

パワー半導体素子の駆動回路

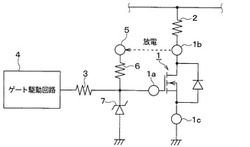

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

駆動信号出力回路

【課題】負荷、電源などの動作条件が変化しても、電磁妨害等を引き起こす周波数帯域の成分が除去された駆動信号を出力する。

【解決手段】負荷5に与えられる駆動信号をハイパスフィルタまたはバンドパスフィルタからなる検出用フィルタ17を介して検出し、その検出駆動信号をバンドギャップ回路18に入力する。バンドギャップ回路18は、固有の周波数特性を有し、検出駆動信号に固有の周波数帯域内の周波数成分が含まれていると出力電圧が低下する特性を持つ。制御回路28は、バンドギャップ回路18の出力電圧を基準電圧と比較し、検出駆動信号に固有の周波数帯域内の信号成分が含まれるか否かを判定する。含まれる場合には、ローパスフィルタ13により駆動信号から当該周波数帯域内の信号成分を除去する。

(もっと読む)

半導体スイッチ

【課題】半導体スイッチにおいて、エネルギー効率を高くする。

【解決手段】半導体スイッチ1は、LED2を駆動回路3により駆動して発光させ、LED2から発光された光を受光部4により受光する。駆動回路3は、バイポーラトランジスタ31と、コイル32と、ダイオード33等を有する。バイポーラトランジスタ31は、導通状態と非導通状態とに切換えられ、導通状態のときに、電源からLED2に電流が供給される状態にし、非導通状態のときに、電源からLED2に電流が供給されない状態にする。コイル32は、LED2に直列に接続されており、バイポーラトランジスタ31が導通状態から非導通状態になったときに、自己誘導作用によって誘導起電力を発生する。ダイオード33は、LED2及びコイル32に並列に接続されており、バイポーラトランジスタ31が非導通状態のときに、コイル32が発生する誘導起電力によって、LED2に電流を還流させる。

(もっと読む)

ドライバ及びその使用方法

【課題】 簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるようにする。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

(もっと読む)

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

半導体モジュール

【課題】半導体スイッチを小さい負担で駆動できるとともに、半導体スイッチに十分なゲート電流を流すことができ、しかも、ゲート配線のインピーダンスによる障害を回避できる半導体モジュール。

【解決手段】ゲートに印加される電圧に応じてオンオフする半導体スイッチQ1と、半導体スイッチのソース電位に対して正極性を有する正極コンデンサ110と、半導体スイッチのソース電位に対して負極性を有する負極コンデンサ111と、正極コンデンサを充電する機能を有し、半導体スイッチをターンオンさせる場合は正極コンデンサからの電流を半導体スイッチのゲートに流すターンオン制御部112と、負極コンデンサを充電する機能を有し、半導体スイッチをターンオフさせる場合は負極コンデンサからの電流を半導体スイッチのゲートに流すターンオフ制御部113を備える。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体かなるスイッチング素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続されたコンデンサC1と抵抗R1とからなる並列回路と、並列回路にコンデンサC2とスイッチング素子Q2と抵抗R2からなる直列回路がさらに並列接続され、コンデンサC2とスイッチング素子Q2との接続点にダイオードD1のアノードが接続され、ダイオードD1のカソードとスイッチング素子Q2のゲートはスイッチング素子Q1のソースに接続され、制御信号のオフ信号に対してスイッチング素子Q1ゲートを負電位にバイアスする。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ドレインとソースとゲートとを有し且つワイドバンドギャップ半導体かなるスイッチグ素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続され、第1のコンデンサC1と第1の抵抗R1とからなる並列回路と、スイッチング素子のゲートとソースとの間に接続され、制御信号のオフ信号に対して遅延させてゲートとソースとの間を短絡する短絡手段S4とを備える。

(もっと読む)

ゲートドライブ回路

【課題】ワイドバンドギャップ半導体からなるスイッチング素子の回生動作時の電力損失を抑制し、かつ、安定してターンオン/オフさせることができるゲートドライブ回路。

【解決手段】制御回路とスイッチング素子Q1のゲートとの間に接続され、コンデンサC1と抵抗R1とダイオードD1からなる直列回路と、スイッチング素子のゲートとソースとの間にPNP型トランジスタQ2が抵抗R2を介して接続され、トランジスタQ2のコレクタ・ベース間にダイオードD2が接続され、さらにトランジスタQ2のベースはダイオードD1のアノードに接続され、制御回路からのオフ信号が入力されると、トランジスタの接合電圧とダイオードD2との順方向電圧との差分電圧を残してゲートとソースとの間を短絡する。

(もっと読む)

電源回路

【課題】高速スイッチング素子である電圧駆動型トランジスタ(MOSFET)のターンオン・オフ時の電圧変化(dV/dt)と電流変化(di/dt)を緩和して、ノイズとサージ電圧の発生を抑制する電源回路を提供する。

【解決手段】トランス2に流れる電流をスイッチングさせるためのMOSFET1のゲート抵抗値を、スイッチング期間内で、MOSFET1のドレイン電圧Vdsの変化の検出と共に切り替える、MOSFET1のゲート電圧Vgは、MOSFET1のゲート電圧の最大定格Vgmax以下とする。

(もっと読む)

CMOSインバータを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路

【課題】CMOSインバータのP形MOSトランジスタのボディバイアスを変化させても、入力信号の立ち上がりと立ち下がりの伝搬遅延時間の差を、従来のものより小さく保てるマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路を提供する。

【解決手段】パスゲートM1、M2の出力に初段出力バッファとして低しきい値CMOSインバータINV1を接続したセレクター回路を基本構成とし、それを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路であって、パスゲートはそのボディ端子が可変電位をとるボディバイアス電源VBNに接続し、INV1のP形MOSトランジスタM3のしきい値電圧を可変にできるようにそのボディ端子は可変電位をとるボディバイアス電源VBPに接続し、そのN形MOSトランジスタM4はそのしきい値電圧を固定するためにそのボディ端子が固定電位をとる電源VSSに接続する。

(もっと読む)

スイッチング素子の駆動回路

【課題】パワーデバイス(メインスイッチM)のゲートの印加電圧をバッテリ12の正電圧より高い電圧と負電圧との双方の電圧とする場合、電源装置の小型化が困難なこと。

【解決手段】バッテリ12、端子T3、スイッチング素子SW1、コンデンサC、スイッチング素子SW2、逆流防止用ダイオードD1、端子T1および充電用抵抗体14によって、メインスイッチMのゲート充電経路が構成される。また、放電用抵抗体16、端子T2、逆流防止用ダイオードD2、スイッチング素子SW3、コンデンサC,スイッチング素子SW4、および端子T4によって、メインスイッチMのゲート放電経路が構成される。さらに、端子T3、スイッチング素子SW6、逆流防止用ダイオードD4、コンデンサC、逆流防止用ダイオードD3、スイッチング素子SW5および端子T4によって、コンデンサCの充電経路が構成される。

(もっと読む)

スイッチング回路

【課題】大電流を制御可能なスイッチング回路において、部品点数を少なくしたコンパクトな構成にて、スイッチング損失を低減するとともにサージ電圧を抑制することができるスイッチング回路を提供する。

【解決手段】高電圧ラインL1と低電圧ラインL2との間においてMOSFET30,31,32,33が並列接続され、ゲート抵抗50,51,52,53の第1の端子がMOSFET30〜33のゲート電極に接続されている。MOSFET30,31,32,33毎に設けられたゲート抵抗50,51,52,53の第2の端子がゲート電圧印加ラインL3を介してパルス発生回路60と接続されている。パルス発生回路60により、ゲート抵抗50〜53を介してMOSFET30〜33のゲート電極にパルス状のゲート電圧が印加される。ゲート電圧印加ラインL3と高電圧ラインL1との間の1箇所にコンデンサ70が接続されている。

(もっと読む)

半導体スイッチング素子のゲート制御回路

【課題】スイッチング素子の発熱を抑制した過電圧抑制ゲート制御を確実、容易にし、さらにスイッチング素子を複数直列接続した半導体スイッチ回路における発振防止と分担電圧のバランス制御を確実、容易にする。

【解決手段】ゲートドライブ回路2によるゲート抵抗Aを通したIGBT1の主ゲート電流とは独立して、電圧補償ゲート制御回路3〜6はIGBT1のコレクタ・エミッタ間電圧Vceがしきい値を超えたときにゲート抵抗Bを通して電圧補償ゲート電流を注入し、電圧Vceがしきい値を下回ったときに電圧補償ゲート電流の注入をオフする。

ゲート抵抗Aの抵抗値に対してゲート抵抗Bの抵抗値を小さくする。電圧補償ゲート電流を注入した後にこのゲート電流の注入量とほぼ同じ電荷量分をIGBT1からゲート電流として引き抜く。

(もっと読む)

ゲート駆動回路

【課題】 簡便な回路構成で、高速に動作するゲート駆動回路を提供することである。

【解決手段】 パワー半導体素子のゲート端子に正電圧を印加するためのNPNトランジスタと、パワー半導体素子のゲート端子に負電圧を印加するためのPNPトランジスタと、NPNトランジスタと、PNPトランジスタとに直列に接続された遮断用抵抗器と、遮断用抵抗器に、正極がパワー半導体素子のゲート端子側となるように並列に接続された遮断用抵抗器切換え半導体スイッチとを備えたゲート駆動回路である。

(もっと読む)

1 - 20 / 105

[ Back to top ]