ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、ゲート駆動回路およびそれを用いた電力変換装置に関する。

【背景技術】

【0002】

従来、P型電界効果トランジスタとN型電界効果トランジスタとを備えるゲート駆動回路が知られている(たとえば、特許文献1参照)。

【0003】

上記特許文献1には、PMOSトランジスタ(P型電界効果トランジスタ)と、PMOSトランジスタのドレインにドレインが接続されるNMOSトランジスタ(N型電界効果トランジスタ)とを備える信号駆動回路(ゲート駆動回路)が開示されている。この信号駆動回路では、PMOSトランジスタのゲートとNMOSトランジスタのゲートとは接続されており、同一の電圧が印加されるように構成されている。また、PMOSトランジスタのソースは、電源電位に接続されるとともに、NMOSトランジスタのソースは、接地電位に接続されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−340088号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特許文献1に開示されている信号駆動回路では、PMOSトランジスタのゲートとNMOSトランジスタのゲートとには、同一の電圧が印加されるように構成されているため、PMOSトランジスタとNMOSトランジスタとが同時にオン状態になる期間がある。このため、電源電位からPMOSトランジスタおよびNMOSトランジスタを介して接地電位に短絡電流が流れることに起因して、消費電力が増大するとともにスイッチングスピードアップの障害になっていた。

【0006】

この発明は、上記のような課題を解決するためになされたものであり、この発明の1つの目的は、P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するとともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路およびそれを用いた電力変換装置を提供することである。

【課題を解決するための手段および発明の効果】

【0007】

上記目的を達成するために、この発明の第1の局面によるゲート駆動回路は、スイッチング素子のゲートを駆動するゲート駆動回路であって、P型電界効果トランジスタと、P型電界効果トランジスタに直列に接続されるN型電界効果トランジスタと、P型電界効果トランジスタのゲートおよびN型電界効果トランジスタのゲートのうちの少なくとも一方に接続されるとともに、電源電位に接続されているダイオードとを備え、ダイオードは、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせるように構成されている。なお、閾値電圧(threshold voltage)とは電界効果トランジスタ(FET)としてドレイン電流を流すために必要なゲート電圧を意味する。PchFETの閾値電圧は正側電源電圧からのゲート電圧、NchFETの閾値電圧は基準電源(0V)側電源電圧から計られたゲート電圧である。

【0008】

この第1の局面によるゲート駆動回路では、上記のように、ダイオードが、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせることによって、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧と、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧との差が小さくなるので、ゲートに印加される電圧が増加し始めてから(または、減少し始めてから)、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方がオン状態からオフ状態(または、オフ状態からオン状態)に切り替わるまでの時間を短縮することができる。これにより、P型電界効果トランジスタとN型電界効果トランジスタとの両方が同時にオン状態になる時間を短縮することができるので、短絡電流に起因する消費電力の増大を抑制することができるとともに、パワー素子を高速スイッチングさせることができる。

【0009】

この発明の第2の局面によるモータ制御装置は、複数のスイッチング素子を含む電力変換部と、複数のスイッチング素子のゲートを駆動するゲート駆動回路とを備え、ゲート駆動回路は、P型電界効果トランジスタと、P型電界効果トランジスタに接続されるN型電界効果トランジスタと、P型電界効果トランジスタのゲートおよびN型電界効果トランジスタのゲートのうちの少なくとも一方に接続されるとともに、電源電位に接続されているダイオードとを含み、ダイオードは、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせるように構成されている。

【0010】

この第2の局面によるモータ制御装置では、上記のように、ダイオードが、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせることによって、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧と、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧との差が小さくなるので、ゲートに印加される電圧が増加し始めてから(または、減少し始めてから)、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方がオン状態からオフ状態(または、オフ状態からオン状態)に切り替わるまでの時間を短縮することができる。これにより、P型電界効果トランジスタとN型電界効果トランジスタとの両方が同時にオン状態になる時間を短縮することができるので、短絡電流に起因する消費電力の増大を抑制可能なモータ制御装置を提供することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の第1実施形態による電力変換装置(モータ制御装置)のブロック図である。

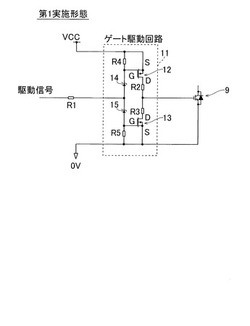

【図2】本発明の第1実施形態による電力変換装置(モータ制御装置)のゲート駆動回路の回路図である。

【図3】本発明の第1実施形態による電力変換装置(モータ制御装置)のゲート駆動回路の動作を説明するための電圧波形図である。

【図4】比較例によるゲート駆動回路の回路図である。

【図5】本発明の第2実施形態による電力変換装置(モータ制御装置)のゲート駆動回路の回路図である。

【図6】本発明の第2実施形態による電力変換装置(モータ制御装置)のゲート駆動回路の動作を説明するための電圧波形図である。

【図7】シミュレーションにより求めた比較例、第1実施形態および第2実施形態の同時ON期間、消費電力、回路定数を示す図である。

【図8】本発明の第2実施形態の第1変形例によるゲート駆動回路の回路図である。

【図9】本発明の第2実施形態の第2変形例によるゲート駆動回路の回路図である。

【図10】本発明におけるツェナーダイオードをダイオードで置換する一例である。

【発明を実施するための形態】

【0012】

以下、本発明の実施形態を図面に基づいて説明する。

【0013】

(第1実施形態)

まず、図1を参照して、本発明の第1実施形態による電力変換装置の一例であるモータ制御装置100の構成について説明する。なお、電力変換装置は本実施形態のゲート駆動回路を用いるものを包含するものであり、高周波電源装置やモータ駆動装置などがある。

【0014】

図1に示すように、第1実施形態によるモータ制御装置100は、コンバータ部1と、インバータ部2と、ゲート駆動回路部3と、制御電源4と、制御部5と、入出力ポート(I/O)6とを備えている。なお、コンバータ部1はAC電圧からDC電圧へ変換する順変換部の一例であり、インバータ部2は、本発明の「電力変換部」の一例である。

【0015】

コンバータ部1には、R端子、S端子およびT端子から3相の交流電源が入力されるように構成されている。コンバータ部1は三相全波整流ダイオードブリッジと三相全波整流ダイオードブリッジの直流出力側の電圧を平滑する平滑用コンデンサを備える。コンバータ部1の入力側には3相交流電源が接続され、コンバータ部1の出力はまた、インバータ部2の入力側に接続されている。また、インバータ部2の出力は、U端子、V端子およびW端子を介して負荷となるモータ(M)200に接続されている。

【0016】

制御電源4には、R端子およびS端子が接続されており、単相の交流電源が入力されるように構成されている。また、制御電源4は、制御部5とゲート駆動回路部3へ接続され、それらに電源を供給している。また、制御部5には入出力ポート6が接続されており、入出力ポート6を介して外部から指令が入力されるように構成されている。また、制御部5は、ゲート駆動回路部3にPWMゲート駆動信号を出力する。

【0017】

コンバータ部1には、6つのダイオード7で構成される全波整流回路と1つの平滑用コンデンサ8とが設けられている。コンバータ部1は、交流を直流に変換する機能を有する。インバータ部2には、6つのスイッチング素子9が設けられている。なお、スイッチング素子9は、IGBT(絶縁ゲートバイポーラトランジスタ)と還流ダイオードとから構成されている。

【0018】

また、ゲート駆動回路部3には、6つのスイッチング素子9のゲートにそれぞれ接続されるゲート駆動回路11(図2参照)が設けられている。図2はゲート駆動回路の回路図である。ゲート駆動回路11は、PchFET12と、NchFET13と、抵抗R2、R3、R4およびR5と、2つのツェナーダイオード14および15とから構成されている。なお、PchFET12は、本発明の「P型電界効果トランジスタ」の一例である。また、NchFET13は、本発明の「N型電界効果トランジスタ」の一例である。なお、ツェナーダイオード14は、本発明の「ダイオード」および「第1ダイオード」の一例である。また、ツェナーダイオード15は、本発明の「ダイオード」および「第2ダイオード」の一例である。

【0019】

PchFET12のソース(S)は、電源電位(VCC)に接続されているとともに、PchFET12のドレイン(D)は、抵抗R2および抵抗R3を介してNchFET13のドレイン(D)に接続されている。NchFET13のソース(S)は抵抗R5を介して接地電位(0V)に接続されている。また、抵抗R2と抵抗R3との共通接続点は、インバータ部2のスイッチング素子9のゲート(G)に接続されている。また、P型トランジスタ12のゲート(G)は、抵抗R4を介して電源電位(VCC)に接続されている。

【0020】

ここで、第1実施形態では、駆動信号が入力される入力側(抵抗R1)とPchFET12のゲート(G)との間には、PchFET12のゲートに印加される電圧を増加させることによりPchFET12のゲート(G)に印加される電圧をPchFET12のゲート(G)の閾値電圧側にシフトさせるためのツェナーダイオード14が設けられている。具体的には、ツェナーダイオード14のアノード側は、抵抗R1に接続されている。また、ツェナーダイオード14のカソード側は、PchFET12のゲート(G)に接続されるとともに、抵抗R4を介して電源電位(VCC)に接続されている。また、ツェナーダイオード14は、ツェナー電圧が電源電位(VCC)からPchFET12のゲート(G)の閾値電圧を引いた電圧より低い電圧になるように選定されている。

【0021】

また、NchFET13のドレイン(D)は、抵抗R2および抵抗R3を介してPchFET12のドレイン(D)に接続される。NchFET13のソース(S)は、接地電位(0V)に接続されている。ここで、第1実施形態では、駆動信号が入力される入力側(抵抗R1)とNchFET13のゲート(G)との間には、NchFET13のゲートに印加される電圧を減少させることによりNchFET13のゲート(G)に印加される電圧をNchFET13のゲート(G)の閾値電圧側にシフトさせるためのツェナーダイオード15が設けられている。具体的には、ツェナーダイオード15のカソード側は、抵抗R1に接続されている。また、ツェナーダイオード15のアノード側は、NchFET13のゲート(G)に接続されるとともに、抵抗R5を介して接地電位(0V)に接続されている。また、ツェナーダイオード15は、電源電位(VCC)からツェナー電圧を引いた電圧が、NchFET13の閾値電圧より高い電圧になるように選定されている。なお、抵抗R1、R4及びR5は、R1≪R4、R5となるように抵抗値が選定されている。

【0022】

なお、PchFET12とNchFET13とが同時にオン状態になるのを抑制するためには、PchFET12の閾値電圧と、NchFET13の閾値電圧とを加算した値が、電源電位(VCC)以上になるのが望ましい。すなわち、下記の式(1)を満足するのが望ましい。

【0023】

【数1】

【0024】

しかしながら、PchFET12およびNchFET13のゲート(G)の閾値電圧は、電源電位(VCC)に比べて比較的小さいため、上記の式(1)の状態(特に等号が成り立つ状態)を満足するのが難しい。そこで、上記のように、ツェナーダイオード14およびツェナーダイオード15を設けることにより、下記の式(2)を満足するように、PchFET12、NchFET13、ツェナーダイオード14およびツェナーダイオード15が選定される。すなわち、PchFET12の閾値電圧と、ツェナーダイオード14およびツェナーダイオード15の閾値電圧と、NchFET13の閾値電圧とを加算した値が、電源電位(VCC)以上になるように選定される。

【0025】

【数2】

【0026】

次に、図2〜図4を参照して、本発明の第1実施形態によるモータ制御装置100のゲート駆動回路11の動作を図4に示すツェナーダイオードを使用しない場合の比較例と比較しながら説明する。

【0027】

まず、図4を参照して、比較例によるゲート駆動回路111の構成について説明する。図4に示すように、比較例によるゲート駆動回路111では、上記第1実施形態のモータ制御装置100のゲート駆動回路11と異なり、第1実施形態の図2においてツェナーダイオード14とツェナーダイオード15を除去しPchFET12のゲート(G)とNchFET13のゲート(G)を駆動信号が入力される抵抗R1の一端に接続し、PchFET12のゲート(G)と電源電位(VCC)との間に接続された抵抗R4を除去し、NchFET13のゲート(G)と接地電位(0V)との間に接続された抵抗R5を除去したものである。PchFET12および112(NchFET13および113)の閾値電圧値等の特性は各々同一とする。PchFET12および112の閾値電圧が、NchFET13および113の閾値電圧値より高いとして以下説明する。

【0028】

(期間A)

図3に示すように、期間Aでは、抵抗R1を介して、Lレベル(0V)の駆動信号が入力される。ここで、第1実施形態では、抵抗R1とPchFET12のゲート(G)との間にツェナーダイオード14が設けられているとともに、PchFET12のゲート(G)が抵抗R4を介して電源電位(VCC)に接続されているので、PchFET12のゲート(G)に印加される電圧は、0Vよりもツェナーダイオード14のツェナー電圧分高くなる。一方、比較例では、PchFET112のゲート(G)に印加される電圧(図3の破線)は、Lレベル(0V)である。

【0029】

期間Aでは、第1実施形態のPchFET12のゲート(G)に印加される電圧(0Vよりもツェナーダイオード14のツェナー電圧分高い電圧)は、前述したツェナーダイオード14の選定により、電源電位(VCC)からPchFET12(PchFET112)のゲート電圧(G)の閾値電圧を引いた値よりも低い。また、比較例のP型トランジスタ112のゲート(G)に印加される電圧は、0Vであり、PchFET12(PchFET112)のゲート電圧(G)の閾値電圧を引いた値よりも低い。従って、第1実施形態のPchFET12および比較例のPchFET112は、オン状態となる。これにより、インバータ部2(図1参照)のスイッチング素子9のゲートには、電源電位(VCC)が印加されて、スイッチング素子9は、オン状態となる。

【0030】

また、第1実施形態のNchFET13のゲート(G)には、抵抗R5を介して、接地電位(0V)の電圧が印加される。一方、比較例のNchFET113のゲート(G)には、抵抗R1を介して、Lレベル(0V)の電圧が印加される。したがって、NchFET13(NchFET113)の閾値電圧よりも低いため、第1実施形態のNchFET13および比較例のNchFET113は、オフ状態となる。

【0031】

(期間B)

期間Bでは、抵抗R1を介して入力される駆動信号を、Lレベル(0V)からHレベル(VCC)に変化させる。これにより、第1実施形態のPchFET12のゲート(G)および比較例のPchFET112のゲート(G)に印加される電圧は、PchFETのゲート−ソース間の浮遊容量が抵抗R1を介して徐々に放電されるため、徐々に高くなる。その結果、ゲート(G)に印加される電圧が電源電位(VCC)から閾値電圧を引いた値に等しくなった際に、第1実施形態のPchFET12および比較例のPchFET112は、オフ状態となる。ここで、第1実施形態のPchFET12には、期間Aにおいて0Vよりツェナーダイオード14のツェナー電圧分高い電圧が印加されているので、第1実施形態のPchFET12のゲート(G)に印加される電圧の方が、比較例のPchFET112のゲート(G)に印加されている電圧よりも閾値電圧に早く到達する。その結果、第1実施形態のPchFET12は、比較例のPchFET112に比べて、早くオフ状態となる。その後、第1実施形態のPchFET12のゲート(G)に印加される電圧が、VCCと等しくなった時点で、PchFET12のゲート(G)には、抵抗R4を介してVCCの電圧が印加される。一方、比較例のPchFET112のゲート(G)には、抵抗R1を介してHレベル(VCC)の電圧が印加される。

【0032】

また、第1実施形態のNchFET13のゲート(G)および比較例のNchFET113のゲート(G)に印加される電圧は、ゲート−ソース間の浮遊容量が抵抗R1を介して徐々に充電されるため、徐々に高くなる。そして、第1実施形態のNchFET13のゲート(G)に印加される電圧、および、比較例のNchFET113のゲート(G)に印加される電圧が閾値電圧に等しくなった際に、第1実施形態のNchFET13および比較例のNchFET113は、オン状態となる。これにより、インバータ部2(図1参照)のスイッチング素子9のゲートには、接地電位(0V)が印加されて、オフ状態となる。

【0033】

その後、第1実施形態のNchFET13のゲート(G)および比較例のNchFET113のゲート(G)に印加される電圧は、閾値電圧よりもさらに高くなる。そして、抵抗R1とNchFET13のゲート(G)との間にツェナーダイオード15が設けられているとともに、NchFET13のゲート(G)が抵抗R5を介して接地電位(0V)に接続されているので、第1実施形態のNchFET13のゲート(G)には、電源電位(VCC)よりもツェナーダイオード15のツェナー電圧分低い電圧が印加される。一方、比較例のNchFET113のゲート(G)には、抵抗R1を介して電源電位(VCC)が印加される。

【0034】

なお、第1実施形態のNchFET13がオン状態になってから、PchFET12がオフ状態になるまでの間は、PchFET12とNchFET13との両方がオン状態となっている。同様に、比較例においても、NchFET113がオン状態になってから、PchFET112がオフ状態になるまでの間は、PchFET112とNchFET113との両方がオン状態となっている。そして、上記のように、第1実施形態のPchFET12が比較例のPchFET112に比べて早くオフ状態となり、第1実施形態のPchFET12およびNchFET13が両方オン状態である期間(同時オン期間)は、比較例のPchFET112およびNchFET113がオン状態である期間と比べて短くなる。

【0035】

(期間C)

期間Cでは、期間Bに引き続き、抵抗R4を介して、Hレベル(VCC)の駆動信号が入力される。これにより、第1実施形態のPchFET12のゲート(G)には、VCCの電圧が印加されるとともに、比較例のPchFET112のゲート(G)にも、VCCの電圧が印加される。したがって、第1実施形態のPchFET12および比較例のPchFET112は、オフ状態のままである。

【0036】

また、第1実施形態のNchFET13のゲート(G)には、VCCよりもツェナーダイオード15のツェナー電圧分低い電圧が印加されるとともに、比較例のNchFET113のゲート(G)には、抵抗R1を介してVCCの電圧が印加される。したがって、第1実施形態のNchFET12および比較例のNchFET112は、オフ状態のままである。その結果、インバータ部2(図1参照)のスイッチング素子9のゲートには、接地電位(0V)が印加されて、スイッチング素子9は、オフ状態を継続する。

【0037】

(期間D)

期間Dでは、抵抗R1を介して、入力される駆動信号が、Hレベル(VCC)からLレベル(0V)に変化する。これにより、第1実施形態のP型トランジスタ12のゲート(G)および比較例のP型トランジスタ112のゲート(G)においては、ゲート−ソース間の浮遊容量が抵抗R1を介して徐々に充電される。したがって、第1実施形態のPchFET12のゲート(G)および比較例のPchFET112のゲート(G)に印加される電圧はすぐには低くならず、徐々に低くなる。そして、第1実施形態のPchFET12のゲート(G)に印加される電圧と比較例のPchFET112のゲート(G)に印加される電圧とが、電源電位(VCC)から閾値電圧を引いた電圧よりも低くなった時点でPchFET12およびPchFET112はオフ状態からオン状態に変化する。その後、第1実施形態のPchFET12のゲート(G)には、0Vよりツェナーダイオード14のツェナー電圧分高い電圧が印加されるとともに、比較例のPchFET112のゲート(G)には、0Vの電圧が印加される。

【0038】

また、第1実施形態のNchFET13においては、ゲート−ソース間に浮遊容量が徐々に放電するため、ゲート(G)に印加される電圧は、電源電圧VCCよりもツェナーダイオード15のツェナー電圧分低い電圧から徐々に低くなる。NchFET13のゲート(G)に印加される電圧が閾値電圧より低くなった時点で、NchFET13はオン状態からオフ状態に変化する。一方、比較例のNchFET113のゲート(G)に印加される電圧は、電源電位VCCから徐々に低くなる。NchFET113のゲート(G)に印加される電圧が、閾値電圧より低くなった時点で、NchFET113はオン状態からオフ状態に変化する。その後、第1実施形態のNchFET13のゲート(G)に印加される電圧がゼロになった時点で、NchFET13のゲート(G)には、抵抗R5を介して接地電位0Vが印加される。また、比較例のNchFET113のゲート(G)には、抵抗R1を介してLレベル(0V)の電圧が印加される。ここで、第1実施形態のNchFET13には、期間Cにおいて電源電位(VCC)よりツェナーダイオード15のツェナー電圧分低い電圧が印加されているので、第1実施形態のNchFET13のゲート(G)に印加される電圧の方が、比較例のNchFET113のゲート(G)に印加されている電圧よりも閾値電圧に早く到達する。その結果、第1実施形態のNchFET13は、比較例のNchFET113に比べて、早くオフ状態となる。

【0039】

なお、第1実施形態のPchFET12がオン状態になってから、NchFET13がオフ状態になるまでの間は、PchFET12とNchFET13との両方がオン状態となっている。同様に、比較例のPchFET112がオン状態になってから、比較例のNchFET113がオフ状態になるまでの間は、比較例のPchFET112とNchFET113との両方がオン状態となっている。上記のように、第1実施形態のNchFET13が比較例のNchFET113に比べて早くオフ状態となることにより、第1実施形態のPchFET12およびNchFET13が両方オン状態である期間(同時オン期間)は、比較例のPchFET112およびNchFET113がオン状態である期間と比べて短くなる。

【0040】

第1実施形態では、上記のように、ツェナーダイオード14およびツェナーダイオード15が、それぞれ、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせることによって、PchFET12およびNchFET13のゲート(G)に印加される電圧と、PchFET12およびNchFET13のゲート(G)の閾値電圧との差が小さくなる。これにより、ゲート(G)に印加される電圧が増加し始めてから、PchFET12がオン状態からオフ状態に切り替わる時間を短縮することができるとともに、ゲート(G)に印加される電圧が減少し始めてから、NchFET13がオン状態からオフ状態に切り替わる時間を短縮することができる。その結果、PchFET12とNchFET13との両方がオン状態になる時間を短縮することができるので、短絡電流に起因する消費電力の増大を抑制することができるとともに、スイッチング素子9を高速スイッチングさせることができる。

【0041】

また、第1実施形態では、上記のように、PchFET12の閾値電圧と、ツェナーダイオード14およびツェナーダイオード15の各ツェナー電圧と、NchFET13の閾値電圧とを加算した値が、電源電位(VCC)以上になるように構成する。これにより、PchFET12とNchFET13とが同時にオン状態になる期間を略ゼロにすることができる。

【0042】

(第2実施形態)

次に、図5を参照して、第2実施形態のモータ制御装置100aのゲート駆動回路11aについて説明する。この第2実施形態では、駆動信号が入力される入力側とPchFET12およびNchFET13との間に、それぞれ、コンデンサ16および17が設けられている。なお、コンデンサ16および17は、それぞれ、本発明の「第1コンデンサ」および「第2コンデンサ」の一例である。

【0043】

図5に示すように、第2実施形態のモータ制御装置100aのゲート駆動回路11aでは、駆動信号が入力される入力側(抵抗R1)とPchFET12との間には、ツェナーダイオード14と並列にコンデンサ16が設けられている。コンデンサ16は、PchFET12がオン状態からオフ状態に移行する際のゲート(G)に印加される電圧の増加率を大きくする機能を有する。コンデンサ16の電極16aは、抵抗R4、ツェナーダイオード14およびPchFET12のゲート(G)に接続されているとともに、電極16bは、抵抗R1に接続されている。

【0044】

また、第2実施形態では、駆動信号が入力される入力側とNchFET13との間には、ツェナーダイオード15と並列にコンデンサ17が設けられている。コンデンサ17は、NchFET13がオン状態からオフ状態に移行する際のゲート(G)に印加される電圧の減少率を大きくする機能を有する。コンデンサ17の電極17aは、抵抗R1に接続されているとともに、電極17bは、抵抗R5、ツェナーダイオード15およびNchFET13のゲート(G)に接続されている。なお、第2実施形態のその他の構成は、上記第1実施形態と同様である。

【0045】

次に、図6を参照して、本発明の第2実施形態によるモータ制御装置100aのゲート駆動回路11aの動作を図4に示す比較例と比較しながら説明する。

【0046】

(期間E)

図6に示すように、期間Eでは、抵抗R1を介して、Lレベル(0V)の駆動信号が入力される。ここで、第2実施形態では、上記第1実施形態と同様に、PchFET12のゲート(G)には、0Vよりもツェナーダイオード14のツェナー電圧分高い電圧が印加される。一方、比較例では、PchFET112のゲート(G)に印加される電圧(図6の破線)は、Lレベル(0V)である。前述のとおり、ツェナーダイオード14のツェナー電圧は、電源電位(VCC)からPchFET12のゲート(G)の閾値電圧を引いた値より低くなっている。その結果、PchFET12(PchFET112)は、オン状態となる。また、第2実施形態のコンデンサ16はツェナーダイオード14のツェナー電圧で充電される。また、このときPchFET12のゲート−ソース間浮遊容量は、電源電位(VCC)からツェナーダイオード14のツェナー電圧で充電されている。

【0047】

また、第2実施形態のNchFET13のゲート(G)には、抵抗R5を介して、0Vの電圧が印加される。同様に、比較例のNchFET113のゲート(G)には、抵抗R1を介して、Lレベル(0V)の電圧が印加される。その結果、NchFET13およびNchFET113は、オフ状態となる。また、コンデンサ17の電極17aと電極17bとの間の電位差は、0Vである。

【0048】

(期間F)

期間Fでは、抵抗R1を介して入力される駆動信号を、Lレベル(0V)からHレベル(VCC)に変化させる。このとき、第2実施形態のPchFET12のゲート(G)および比較例(図4参照)のPchFET112のゲート(G)に印加される電圧は、ゲート−ソース間の浮遊容量が徐々に放電するので、徐々に高くなる。ここでPchFET12のゲート−ソース間の浮遊容量は、R1を介した放電ルートとR4を介した放電ルートの二つの放電ルートがある。これに対してPchFET112のゲート−ソース間の浮遊容量はR1を介した放電ルートのみである。従って、PchFET12のゲート−ソース間浮遊容量のほうが、PchFET112のゲート−ソース間浮遊容量より早く放電するため、PchFET12のゲート(G)に印加される電圧の増加率(傾き)は、比較例のPchFET112のゲート(G)に印加される電圧の増加率よりも大きくなる。そして、第2実施形態のPchFET12および比較例のPchFET112は、ゲート(G)に印加される電圧が電源電位(VCC)からゲート(G)の閾値電圧を引いた電圧値(ここではターンオフ電圧と呼ぶ)より高くなった時点でオフ状態となる。ここで、第2実施形態のPchFET12には、期間Eにおいて0Vよりツェナーダイオード14のツェナー電圧分高い電圧が印加されているとともに印加される電圧の増加率(傾き)が大きくなるので、第2実施形態のPchFET12のゲート(G)に印加される電圧の方が、比較例のPchFET112のゲート(G)に印加されている電圧よりもターンオフ電圧に早く到達する。その結果、第2実施形態のPchFET12は、比較例のPchFET112に比べて、早くオフ状態となる。その後、第2実施形態のPchFET12のゲート(G)に印加される電圧は、徐々に高くなるが、一般には容量の大きさからPchFET12のゲート−ソース間の浮遊容量がコンデンサ16よりも先に蓄積された電荷がゼロとなり、このときPchFET12に印加される電圧は、電源電位VCCとなる。その後は、コンデンサ16のみが放電するが、この放電電流によりPchFET12のゲート−ソース間の浮遊容量は、放電時とは逆の極性で充電される。これにより、PchFET12のゲート(G)に印加される電圧は、電源電位(VCC)を超えて高くなる。このときコンデンサ16の放電電流は、抵抗R4とPchFET12のゲート−ソース間の浮遊容量に分流して流れる。抵抗R4を流れる電流はPchFET12のゲート−ソース間の浮遊容量の充電電圧に比例して大きくなる。これに対してコンデンサ16の放電電流は、放電が進むにつれ減少している。従ってある時点で、抵抗R4を流れる電流とコンデンサ16の放電電流は等しくなる。このときPchFET12のゲート−ソース間の浮遊容量の充電電流はゼロとなり、PchFET12のゲート(G)に印加される電圧はピーク値となる。以後は、コンデンサ16とPchFET12のゲート−ソース間の浮遊容量の双方の放電電流が抵抗R4を流れ、PchFET12のゲート(G)に印加される電圧は徐々に低くなる。双方の放電が完了した時点で、PchFET12のゲート(G)に印加される電圧は電源電位(VCC)となる。これに対して比較例のPchFET12のゲート(G)に印加される電圧は、徐々に高くなって電源電位(VCC)になる。

【0049】

また、第2実施形態のNchFET13のゲート(G)および比較例のNchFET113のゲート(G)に印加される電圧は、PchFET12のゲート(G)と同様徐々に高くなる。そして、第2実施形態のNchFET13のゲート(G)に印加される電圧、および、比較例のNchFET113のゲート(G)に印加される電圧が、閾値電圧と等しくなった際に、第2実施形態のNchFET13および比較例のNchFET113は、オン状態となる。そして、インバータ部2(図1参照)のスイッチング素子9のゲートには、接地電位(0V)が印加されて、オフ状態となる。その後、NchFET13のゲート(G)に印加される電圧は、徐々に高くなり、電源電位(VCC)よりもツェナーダイオード15のツェナー電圧分低い電圧になる。また、比較例のNchFET113のゲート(G)に印加される電圧は、電源電位(VCC)になる。

【0050】

そして、上記のように、第2実施形態のPchFET12が比較例のPchFET112に比べて早くオフ状態となるため、第2実施形態のPchFET12およびNchFET13が両方オン状態である期間(同時オン期間)は、比較例のPchFET112およびNchFET113がオン状態である期間と比べて短くなる。

【0051】

(期間G)

期間Gでは、期間Fに引き続き、抵抗R1を介して、Hレベル(VCC)の駆動信号が入力される。これにより、第2実施形態のPchFET12および比較例のPchFET112は、オフ状態のままである。また、第2実施形態のNchFET13および比較例のNchFET113は、オン状態のままである。

【0052】

(期間H)

期間Hでは、抵抗R1を介して、入力される駆動信号が、Hレベル(VCC)からLレベル(0V)に変化する。これにより、第2実施形態のPchFET12のゲート(G)および比較例のPchFET112のゲート(G)に印加される電圧は、徐々に低くなる。第2実施形態、比較例とも、PchFET12またはNchFET112のゲート(G)に印加される電圧が、電源電位(VCC)からPchFET12またはPchFET112のゲート(G)の閾値電圧を引いた電圧(ここではターンオン電圧と呼ぶ)に等しくなったときに、PchFET12および比較例のPchFET112は、オン状態となる。その後、第2実施形態のPchFET12のゲート(G)には、0Vよりツェナーダイオード14のツェナー電圧分高い電圧が印加されるとともに、比較例のPchFET112のゲート(G)には、0Vの電圧が印加される。

【0053】

また、第2実施形態のNchFET13のゲート(G)および比較例のNchFET113のゲート(G)に印加される電圧は、ゲート−ソース間の浮遊容量がR1を介して徐々に放電するので、徐々に低くなる。このとき期間FにおけるPchFET12と同様、比較例に比べて抵抗R5を流れる放電電流が加算されるため、NchFET13のゲート(G)に印加される電圧は、比較例のNchFET113のゲート(G)に印加される電圧よりも増加率(傾き)が大きくなる。そして、第2実施形態のNchFET13および比較例のNchFET113は、ゲート(G)に印加される電圧がゲート(G)の閾値電圧より低くなった時点でオフ状態となる。その後、第2実施形態のNchFET13のゲート(G)に印加される電圧は、徐々に増加するが、一般には容量の大きさからNchFET13のゲート−ソース間の浮遊容量がコンデンサ17よりも先に蓄積された電荷がゼロとなり、このときNchFET13に印加される電圧は、Lレベル(0V)となる。その後は、コンデンサ17のみが放電するが、この放電電流によりNchFET13のゲート−ソース間の浮遊容量は、放電時とは逆の極性で充電される。これにより、NchFET13のゲート(G)に印加される電圧は、Lレベル(0V)よりも低くなる。このときコンデンサ17の放電電流は、抵抗R5とNchFET13のゲート−ソース間の浮遊容量に分流して流れる。抵抗R5を流れる電流はNchFET13のゲート−ソース間の浮遊容量の充電電圧に比例して大きくなる。これに対してコンデンサ17の放電電流は、放電が進むにつれ減少している。従ってある時点で、抵抗R5を流れる電流とコンデンサ17の放電電流は等しくなる。このときNchFET13のゲート−ソース間の浮遊容量の充電電流はゼロとなり、NchFET13のゲート(G)に印加される電圧は最低値となる。以後は、コンデンサ17とNchFET13のゲート−ソース間の浮遊容量の双方の放電電流が抵抗R5を流れ、NchFET13のゲート(G)に印加される電圧は徐々に高くなる。双方の放電が完了した時点で、NchFET13のゲート(G)に印加される電圧はLレベル(0V)となる。これに対して比較例のNchFET113のゲート(G)に印加される電圧は、徐々に低くなってLレベル(0V)となる。ここで、第2実施形態のNchFET13には、期間Gにおいて電源電位(VCC)よりツェナーダイオード15のツェナー電圧分低い電圧が印加されているとともに、第2実施形態のNchFET13に印加される電圧の減少率が比較例のNchFET113に印加される電圧の減少率よりも大きいので、第2実施形態のNchFET13のゲート(G)に印加される電圧の方が、比較例のNchFET113のゲート(G)に印加されている電圧よりも閾値電圧に早く到達する。その結果、第2実施形態のNchFET13は、比較例のNchFET113に比べて、早くオフ状態となる。

【0054】

そして、上記のように、第2実施形態のNchFET13が比較例のNchFET113に比べて早くオフ状態となるため、第2実施形態のPchFET12およびNchFET13が両方オン状態である期間(同時オン期間)は、比較例のPchFET112およびNchFET113がオン状態である期間と比べて短くなる。

【0055】

第2実施形態では、上記のように、PchFET12とNchFET13との両方がオン状態になる時間をより短縮することができる。その結果、短絡電流に起因する消費電力の増大をより抑制することができる。

【0056】

(シミュレーション)

次に、図7を参照して、比較例(図4参照)、第1実施形態(図2参照)および第2実施形態(図5参照)のゲート駆動回路の消費電力について行ったシミュレーションについて説明する。

【0057】

シミュレーションの条件としては、比較例のPchFET112およびNchFET113と、第1実施形態(第2実施形態)のPchFET12およびNchFET13には、Lレベルの電圧(0V)とHレベルの電圧(13V)とが印加されるとする。また、Lレベルの電圧(0V)とHレベルの電圧(13V)とは、100kHzの周期で交互に印加されるとする。また、比較例のPchFET112およびNchFET113、第1実施形態(第2実施形態)のPchFET12およびNchFET13に接続される抵抗R1の抵抗は、130Ωとする。また、比較例のPchFET112およびNchFET113の間、および、第1実施形態(第2実施形態)のPchFET12およびNchFET13の間に設けられる抵抗R2およびR3の抵抗は、それぞれ、10Ωおよび1Ωとする。また、第1実施形態(第2実施形態)のPchFET12およびNchFET13にそれぞれ接続される抵抗R4およびR5の抵抗は、10kΩとする。また、第2実施形態のコンデンサ16および17の静電容量は、それぞれ、220pFとする。また、比較例のPchFET112、第1実施形態(第2実施形態)のPchFET12の閾値電圧は、それぞれ、1.7Vとする。また、比較例のNchFET113、第1実施形態(第2実施形態)のNchFET13の閾値電圧は、それぞれ、1.15Vとする。

【0058】

上記のような条件によりシミュレーションを行ったところ、比較例によるゲート駆動回路111(図4参照)では、PchFET112およびNchFET113に印加される電圧がLレベル(0V)からHレベル(13V)に変化する際(図3の期間B参照)に、PchFET112とNchFET113との両方がオン状態である期間が105nsになることが判明した。また、PchFET112およびNchFET113に印加される電圧がHレベル(13V)からLレベル(0V)に変化する際(図3の期間D参照)に、PchFET112とNchFET113との両方がオン状態である期間が70nsになることが判明した。その結果、PchFET112から抵抗R2およびR3を介してNchFET113に短絡電流が流れることにより消費される電力は、0.27Wになることが判明した。

【0059】

なお、PchFET112およびNchFET113に印加される電圧がLレベル(0V)からHレベル(13V)に変化し始めてから、スイッチング素子9がオン状態からオフ状態に変化し始めるまでの時間(ON遅延)は、13nsになることが確認された。また、PchFET112およびNchFET113に印加される電圧がHレベル(13V)からLレベル(0V)に変化し始めてから、スイッチング素子9がオフ状態からオン状態(OFF遅延)に変化し始めるまでの時間は、65nsになることが確認された。

【0060】

次に、第1実施形態によるゲート駆動回路11(図2参照)では、PchFET12およびNchFET13に印加される電圧がLレベル(0V)からHレベル(13V)に変化する際(図3の期間B参照)に、PchFET12とNchFET13との両方がオン状態である期間が58nsになることが判明した。また、PchFET12およびNchFET13に印加される電圧がHレベル(13V)からLレベル(0V)に変化する際(図3の期間D参照)に、PchFET12とNchFET13との両方がオン状態である期間が0sになることが判明した。すなわち、第1実施形態のPchFET12とNchFET13との両方がオン状態である合計の期間58ns(=58ns+0s)は、比較例のPchFET112とNchFET113との両方がオン状態である合計の期間175ns(=105ns+70ns)よりも短くなることが確認された。つまり、ツェナーダイオード14および15を設けることにより、PchFET12とNchFET13との両方がオン状態である期間が短くなることが確認された。その結果、PchFET12から抵抗R2およびR3を介してNchFET13に短絡電流が流れることにより消費される電力は、0.09Wになり、比較例(0.27W)と比べて小さくなることが判明した。

【0061】

なお、PchFET12およびNchFET13に印加される電圧がLレベル(0V)からHレベル(13V)に変化し始めてから、スイッチング素子9がオン状態からオフ状態に変化し始めるまでの時間(ON遅延)は、15nsになることが確認された。また、PchFET12およびNchFET13に印加される電圧がHレベル(13V)からLレベル(0V)に変化し始めてから、スイッチング素子9がオフ状態からオン状態に変化し始めるまでの時間(OFF遅延)は、18nsになることが確認された。

【0062】

次に、第2実施形態によるゲート駆動回路11(図5参照)では、PchFET12およびNchFET13に印加される電圧がLレベル(0V)からHレベル(13V)に変化する際(図6の期間F参照)に、PchFET12とNchFET13との両方がオン状態である期間が15nsになることが判明した。また、PchFET12およびNchFET13に印加される電圧がHレベル(13V)からLレベル(0V)に変化する際(図6の期間H参照)に、PchFET12とNchFET13との両方がオン状態である期間が0sになることが判明した。すなわち、第2実施形態のPchFET12とNchFET13との両方がオン状態である合計の期間15ns(=15ns+0s)は、比較例のPchFET112とNchFET113との両方がオン状態である合計の期間175ns(=105ns+70ns)、および、第1実施形態のPchFET12とNchFET13との両方がオン状態である合計の期間58ns(=58ns+0s)よりも短くなることが確認された。つまり、ツェナーダイオード14および15と、コンデンサ16および17とを設けることにより、PchFET12とNchFET13との両方がオン状態である期間がより短くなることが確認された。その結果、PchFET12から抵抗R2およびR3を介してNchFET13に短絡電流が流れることにより消費される電力は、0.02Wになり、比較例(0.27W)および第1実施形態(0.09W)と比べて小さくなることが判明した。

【0063】

なお、PchFET12およびNchFET13に印加される電圧がLレベル(0V)からHレベル(13V)に変化し始めてから、スイッチング素子9がオン状態からオフ状態に変化し始めるまでの時間(ON遅延)は、上記第1実施形態と同じ15nsになることが確認された。また、PchFET12およびNchFET13に印加される電圧がHレベル(13V)からLレベル(0V)に変化し始めてから、スイッチング素子9がオフ状態からオン状態になるまでの時間(OFF遅延)は、上記第1実施形態と同じ18nsになることが確認された。

【0064】

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれる。

【0065】

たとえば、上記第1および第2実施形態では、入力側とPchFETとの間、および、入力側とNchFETとの間の両方にツェナーダイオードを設ける例を示したが、本発明はこれに限られない。たとえば、入力側とPchFETとの間、または、入力側とNchFETとの間の一方にツェナーダイオードを設けてもよい。

【0066】

また、上記第1および第2実施形態では、入力側とPchFETとの間、および、入力側とNchFETとの間の両方にツェナーダイオードを設ける例を示したが、本発明はこれに限られない。たとえば、入力側とPchFETとの間、および、入力側とNchFETとの間にツェナーダイオード以外のダイオードを設けてもよい。

【0067】

また、上記第1および第2実施形態では、インバータ部に含まれるスイッチング素子が、電解効果トランジスタと還流ダイオードとから構成されている例を示したが、本発明はこれに限られない。たとえば、スイッチング素子をIGBTと還流ダイオードとから構成してもよい。

【0068】

また、上記第2実施形態では、入力側とPchFETとの間、および、入力側とNchFETとの間の両方にコンデンサを設ける例を示したが、本発明はこれに限られない。たとえば、入力側とP型の電界効果トランジスタとの間、または、入力側とNchFETとの間の一方にコンデンサを設けてもよい。

【0069】

また、上記第2実施形態では、入力側とPchFETとの間、および、入力側とNchFETとの間に、それぞれ、ツェナーダイオードとコンデンサとを並列に設ける例を示したが、本発明はこれに限られない。たとえば、図8に示す第2実施形態の第1変形例によるゲート駆動回路11bのように、入力側とPchFET12との間にツェナーダイオード14とコンデンサ16とに並列に放電用ダイオード18を設けるとともに、ツェナーダイオード14とPchFET12のゲート(G)との間に逆流防止ダイオード19を設けてもよい。さらに、入力側とNchFET13との間にツェナーダイオード15とコンデンサ17とに並列に放電用ダイオード20を設けるとともに、ツェナーダイオード15とNchFET13のゲート(G)との間に逆流防止ダイオード21を設けてもよい。これにより、放電用ダイオード18および放電用ダイオード20を介してPchFET12およびNchFET13に電圧を印加することができるので、PchFET12およびNchFET13の容量が大きくなった場合でも、PchFET12およびNchFET13のオンオフを容易に行うことができる。

【0070】

さらなる第2実施形態の第2変形例を図9に示す。第2実施形態(図5)と異なる点は、図9に示すように、ツェナーダイオード14を、電源電位VCCとPchFET12のゲート(G)との間に配置するとともに、ツェナーダイオード15を、接地電位(0V)とNchFET13のゲート(G)との間に配置したことである。なお、ツェナーダイオード14(ツェナーダイオード15でも同様)のツェナー電圧はPchFET12(NchFET13でも同様)の閾値電圧よりも高く設定されている。また、PchFET12(NchFET13でも同様)のオン時にPchFET12のゲートとソース間電圧をツェナー電圧に維持するため、コンデンサ16と並列に抵抗R6(R6≪R4)が、およびコンデンサ17と並列に抵抗R7(R7≪R5)が設けられている。これによりPchFET12のオン時に抵抗R6を流れている電流の一部がツェナーダイオード14を流れるので、PchFET12のゲートとソース間電圧はツェナー電圧に維持される。以上はNchFET13においても同様である。

【0071】

この第2実施形態の第2変形例の場合、PchFET12のオン時、ゲート(G)にはツェナーダイオード14のツェナー電圧が印加(ツェナー電圧で抑制)され、NchFET13のオン時、ゲート(G)にはツェナーダイオード15のツェナー電圧が印加(ツェナー電圧で抑制)されており、第2実施形態で説明した動作と同様にオフ動作への切り替わりに際しては、比較例のPchFET112およびNchFET113のゲート(G)に印加されている電圧よりも閾値電圧に早く到達する。さらにコンデンサ16は、PchFET12がオン状態からオフ状態に移行する際のゲート(G)に印加される電圧の増加率を大きくし、コンデンサ17は、NchFET13がオン状態からオフ状態に移行する際のゲート(G)に印加される電圧の減少率を大きくする機能を有するので、この点からも閾値電圧に早く到達する。このように、この変形例は第2実施形態と回路構成に上述の相違部分はあるが、第2実施形態と同様の効果が得られる。

【0072】

また、第1実施形態(図2)、第2実施形態(図5)、第2実施形態の第1変形例(図8)、および、第2実施形態の第2変形例(図9)では、上記のように、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるためにツェナーダイオード14および15を用いる例を示したが、本発明はこれに限られない。たとえば、これらツェナーダイオードを図10に示すダイオードで構成する回路で置き換えてもよい。図10に示すように、通常のダイオードを用いる場合には、ツェナー電圧(降伏電圧)に相当する電圧をダイオードの順電圧降下で代用し、ツェナー電圧に相当する大きさの電圧とするために1つ以上(図10では、3つ)のダイオード14a(15a)を直列に接続している。またツェナーダイオードの順方向特性を代用するために、この1つ以上のダイオード14a(15a)の直列接続体と逆並列に1個のダイオード14b(15b)を接続している。

【0073】

上述のようにダイオード順方向降下電圧がツェナーダイオードの降伏電圧に略等しくなるように1つ以上のダイオード14a(15a)を直列接続した直列接続体と、直列接続体とは逆極性にしたダイオード14b(15b)とを並列接続した並列接続体を準備する。そしてツェナーダイオードのカソード(K)側が逆極性にしたダイオードのカソード側に、ツェナーダイオードのアノード(A)側が逆極性にしたダイオードのアノード側になるようにツェナーダイオードを並列接続体に置換する。

【符号の説明】

【0074】

1 コンバータ部(順変換部)

2 インバータ部(電力変換部)

3 ゲート駆動回路部

4 制御電源

5 制御部

6 I/O

7 ダイオード

8 平滑用コンデンサ

9 スイッチング素子

11、11a、11b ゲート駆動回路

12 PchFET(P型電界効果トランジスタ)

13 NchFET(N型電界効果トランジスタ)

14 ツェナーダイオード(ダイオード、第1ツェナーダイオード)

15 ツェナーダイオード(ダイオード、第2ツェナーダイオード)

16 コンデンサ(第1コンデンサ)

17 コンデンサ(第2コンデンサ)

18、20 放電用ダイオード

100、100a モータ制御装置(電力変換装置)

【技術分野】

【0001】

この発明は、ゲート駆動回路およびそれを用いた電力変換装置に関する。

【背景技術】

【0002】

従来、P型電界効果トランジスタとN型電界効果トランジスタとを備えるゲート駆動回路が知られている(たとえば、特許文献1参照)。

【0003】

上記特許文献1には、PMOSトランジスタ(P型電界効果トランジスタ)と、PMOSトランジスタのドレインにドレインが接続されるNMOSトランジスタ(N型電界効果トランジスタ)とを備える信号駆動回路(ゲート駆動回路)が開示されている。この信号駆動回路では、PMOSトランジスタのゲートとNMOSトランジスタのゲートとは接続されており、同一の電圧が印加されるように構成されている。また、PMOSトランジスタのソースは、電源電位に接続されるとともに、NMOSトランジスタのソースは、接地電位に接続されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−340088号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特許文献1に開示されている信号駆動回路では、PMOSトランジスタのゲートとNMOSトランジスタのゲートとには、同一の電圧が印加されるように構成されているため、PMOSトランジスタとNMOSトランジスタとが同時にオン状態になる期間がある。このため、電源電位からPMOSトランジスタおよびNMOSトランジスタを介して接地電位に短絡電流が流れることに起因して、消費電力が増大するとともにスイッチングスピードアップの障害になっていた。

【0006】

この発明は、上記のような課題を解決するためになされたものであり、この発明の1つの目的は、P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するとともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路およびそれを用いた電力変換装置を提供することである。

【課題を解決するための手段および発明の効果】

【0007】

上記目的を達成するために、この発明の第1の局面によるゲート駆動回路は、スイッチング素子のゲートを駆動するゲート駆動回路であって、P型電界効果トランジスタと、P型電界効果トランジスタに直列に接続されるN型電界効果トランジスタと、P型電界効果トランジスタのゲートおよびN型電界効果トランジスタのゲートのうちの少なくとも一方に接続されるとともに、電源電位に接続されているダイオードとを備え、ダイオードは、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせるように構成されている。なお、閾値電圧(threshold voltage)とは電界効果トランジスタ(FET)としてドレイン電流を流すために必要なゲート電圧を意味する。PchFETの閾値電圧は正側電源電圧からのゲート電圧、NchFETの閾値電圧は基準電源(0V)側電源電圧から計られたゲート電圧である。

【0008】

この第1の局面によるゲート駆動回路では、上記のように、ダイオードが、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせることによって、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧と、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧との差が小さくなるので、ゲートに印加される電圧が増加し始めてから(または、減少し始めてから)、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方がオン状態からオフ状態(または、オフ状態からオン状態)に切り替わるまでの時間を短縮することができる。これにより、P型電界効果トランジスタとN型電界効果トランジスタとの両方が同時にオン状態になる時間を短縮することができるので、短絡電流に起因する消費電力の増大を抑制することができるとともに、パワー素子を高速スイッチングさせることができる。

【0009】

この発明の第2の局面によるモータ制御装置は、複数のスイッチング素子を含む電力変換部と、複数のスイッチング素子のゲートを駆動するゲート駆動回路とを備え、ゲート駆動回路は、P型電界効果トランジスタと、P型電界効果トランジスタに接続されるN型電界効果トランジスタと、P型電界効果トランジスタのゲートおよびN型電界効果トランジスタのゲートのうちの少なくとも一方に接続されるとともに、電源電位に接続されているダイオードとを含み、ダイオードは、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせるように構成されている。

【0010】

この第2の局面によるモータ制御装置では、上記のように、ダイオードが、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせることによって、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧と、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧との差が小さくなるので、ゲートに印加される電圧が増加し始めてから(または、減少し始めてから)、P型電界効果トランジスタおよびN型電界効果トランジスタのうちの少なくとも一方がオン状態からオフ状態(または、オフ状態からオン状態)に切り替わるまでの時間を短縮することができる。これにより、P型電界効果トランジスタとN型電界効果トランジスタとの両方が同時にオン状態になる時間を短縮することができるので、短絡電流に起因する消費電力の増大を抑制可能なモータ制御装置を提供することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の第1実施形態による電力変換装置(モータ制御装置)のブロック図である。

【図2】本発明の第1実施形態による電力変換装置(モータ制御装置)のゲート駆動回路の回路図である。

【図3】本発明の第1実施形態による電力変換装置(モータ制御装置)のゲート駆動回路の動作を説明するための電圧波形図である。

【図4】比較例によるゲート駆動回路の回路図である。

【図5】本発明の第2実施形態による電力変換装置(モータ制御装置)のゲート駆動回路の回路図である。

【図6】本発明の第2実施形態による電力変換装置(モータ制御装置)のゲート駆動回路の動作を説明するための電圧波形図である。

【図7】シミュレーションにより求めた比較例、第1実施形態および第2実施形態の同時ON期間、消費電力、回路定数を示す図である。

【図8】本発明の第2実施形態の第1変形例によるゲート駆動回路の回路図である。

【図9】本発明の第2実施形態の第2変形例によるゲート駆動回路の回路図である。

【図10】本発明におけるツェナーダイオードをダイオードで置換する一例である。

【発明を実施するための形態】

【0012】

以下、本発明の実施形態を図面に基づいて説明する。

【0013】

(第1実施形態)

まず、図1を参照して、本発明の第1実施形態による電力変換装置の一例であるモータ制御装置100の構成について説明する。なお、電力変換装置は本実施形態のゲート駆動回路を用いるものを包含するものであり、高周波電源装置やモータ駆動装置などがある。

【0014】

図1に示すように、第1実施形態によるモータ制御装置100は、コンバータ部1と、インバータ部2と、ゲート駆動回路部3と、制御電源4と、制御部5と、入出力ポート(I/O)6とを備えている。なお、コンバータ部1はAC電圧からDC電圧へ変換する順変換部の一例であり、インバータ部2は、本発明の「電力変換部」の一例である。

【0015】

コンバータ部1には、R端子、S端子およびT端子から3相の交流電源が入力されるように構成されている。コンバータ部1は三相全波整流ダイオードブリッジと三相全波整流ダイオードブリッジの直流出力側の電圧を平滑する平滑用コンデンサを備える。コンバータ部1の入力側には3相交流電源が接続され、コンバータ部1の出力はまた、インバータ部2の入力側に接続されている。また、インバータ部2の出力は、U端子、V端子およびW端子を介して負荷となるモータ(M)200に接続されている。

【0016】

制御電源4には、R端子およびS端子が接続されており、単相の交流電源が入力されるように構成されている。また、制御電源4は、制御部5とゲート駆動回路部3へ接続され、それらに電源を供給している。また、制御部5には入出力ポート6が接続されており、入出力ポート6を介して外部から指令が入力されるように構成されている。また、制御部5は、ゲート駆動回路部3にPWMゲート駆動信号を出力する。

【0017】

コンバータ部1には、6つのダイオード7で構成される全波整流回路と1つの平滑用コンデンサ8とが設けられている。コンバータ部1は、交流を直流に変換する機能を有する。インバータ部2には、6つのスイッチング素子9が設けられている。なお、スイッチング素子9は、IGBT(絶縁ゲートバイポーラトランジスタ)と還流ダイオードとから構成されている。

【0018】

また、ゲート駆動回路部3には、6つのスイッチング素子9のゲートにそれぞれ接続されるゲート駆動回路11(図2参照)が設けられている。図2はゲート駆動回路の回路図である。ゲート駆動回路11は、PchFET12と、NchFET13と、抵抗R2、R3、R4およびR5と、2つのツェナーダイオード14および15とから構成されている。なお、PchFET12は、本発明の「P型電界効果トランジスタ」の一例である。また、NchFET13は、本発明の「N型電界効果トランジスタ」の一例である。なお、ツェナーダイオード14は、本発明の「ダイオード」および「第1ダイオード」の一例である。また、ツェナーダイオード15は、本発明の「ダイオード」および「第2ダイオード」の一例である。

【0019】

PchFET12のソース(S)は、電源電位(VCC)に接続されているとともに、PchFET12のドレイン(D)は、抵抗R2および抵抗R3を介してNchFET13のドレイン(D)に接続されている。NchFET13のソース(S)は抵抗R5を介して接地電位(0V)に接続されている。また、抵抗R2と抵抗R3との共通接続点は、インバータ部2のスイッチング素子9のゲート(G)に接続されている。また、P型トランジスタ12のゲート(G)は、抵抗R4を介して電源電位(VCC)に接続されている。

【0020】

ここで、第1実施形態では、駆動信号が入力される入力側(抵抗R1)とPchFET12のゲート(G)との間には、PchFET12のゲートに印加される電圧を増加させることによりPchFET12のゲート(G)に印加される電圧をPchFET12のゲート(G)の閾値電圧側にシフトさせるためのツェナーダイオード14が設けられている。具体的には、ツェナーダイオード14のアノード側は、抵抗R1に接続されている。また、ツェナーダイオード14のカソード側は、PchFET12のゲート(G)に接続されるとともに、抵抗R4を介して電源電位(VCC)に接続されている。また、ツェナーダイオード14は、ツェナー電圧が電源電位(VCC)からPchFET12のゲート(G)の閾値電圧を引いた電圧より低い電圧になるように選定されている。

【0021】

また、NchFET13のドレイン(D)は、抵抗R2および抵抗R3を介してPchFET12のドレイン(D)に接続される。NchFET13のソース(S)は、接地電位(0V)に接続されている。ここで、第1実施形態では、駆動信号が入力される入力側(抵抗R1)とNchFET13のゲート(G)との間には、NchFET13のゲートに印加される電圧を減少させることによりNchFET13のゲート(G)に印加される電圧をNchFET13のゲート(G)の閾値電圧側にシフトさせるためのツェナーダイオード15が設けられている。具体的には、ツェナーダイオード15のカソード側は、抵抗R1に接続されている。また、ツェナーダイオード15のアノード側は、NchFET13のゲート(G)に接続されるとともに、抵抗R5を介して接地電位(0V)に接続されている。また、ツェナーダイオード15は、電源電位(VCC)からツェナー電圧を引いた電圧が、NchFET13の閾値電圧より高い電圧になるように選定されている。なお、抵抗R1、R4及びR5は、R1≪R4、R5となるように抵抗値が選定されている。

【0022】

なお、PchFET12とNchFET13とが同時にオン状態になるのを抑制するためには、PchFET12の閾値電圧と、NchFET13の閾値電圧とを加算した値が、電源電位(VCC)以上になるのが望ましい。すなわち、下記の式(1)を満足するのが望ましい。

【0023】

【数1】

【0024】

しかしながら、PchFET12およびNchFET13のゲート(G)の閾値電圧は、電源電位(VCC)に比べて比較的小さいため、上記の式(1)の状態(特に等号が成り立つ状態)を満足するのが難しい。そこで、上記のように、ツェナーダイオード14およびツェナーダイオード15を設けることにより、下記の式(2)を満足するように、PchFET12、NchFET13、ツェナーダイオード14およびツェナーダイオード15が選定される。すなわち、PchFET12の閾値電圧と、ツェナーダイオード14およびツェナーダイオード15の閾値電圧と、NchFET13の閾値電圧とを加算した値が、電源電位(VCC)以上になるように選定される。

【0025】

【数2】

【0026】

次に、図2〜図4を参照して、本発明の第1実施形態によるモータ制御装置100のゲート駆動回路11の動作を図4に示すツェナーダイオードを使用しない場合の比較例と比較しながら説明する。

【0027】

まず、図4を参照して、比較例によるゲート駆動回路111の構成について説明する。図4に示すように、比較例によるゲート駆動回路111では、上記第1実施形態のモータ制御装置100のゲート駆動回路11と異なり、第1実施形態の図2においてツェナーダイオード14とツェナーダイオード15を除去しPchFET12のゲート(G)とNchFET13のゲート(G)を駆動信号が入力される抵抗R1の一端に接続し、PchFET12のゲート(G)と電源電位(VCC)との間に接続された抵抗R4を除去し、NchFET13のゲート(G)と接地電位(0V)との間に接続された抵抗R5を除去したものである。PchFET12および112(NchFET13および113)の閾値電圧値等の特性は各々同一とする。PchFET12および112の閾値電圧が、NchFET13および113の閾値電圧値より高いとして以下説明する。

【0028】

(期間A)

図3に示すように、期間Aでは、抵抗R1を介して、Lレベル(0V)の駆動信号が入力される。ここで、第1実施形態では、抵抗R1とPchFET12のゲート(G)との間にツェナーダイオード14が設けられているとともに、PchFET12のゲート(G)が抵抗R4を介して電源電位(VCC)に接続されているので、PchFET12のゲート(G)に印加される電圧は、0Vよりもツェナーダイオード14のツェナー電圧分高くなる。一方、比較例では、PchFET112のゲート(G)に印加される電圧(図3の破線)は、Lレベル(0V)である。

【0029】

期間Aでは、第1実施形態のPchFET12のゲート(G)に印加される電圧(0Vよりもツェナーダイオード14のツェナー電圧分高い電圧)は、前述したツェナーダイオード14の選定により、電源電位(VCC)からPchFET12(PchFET112)のゲート電圧(G)の閾値電圧を引いた値よりも低い。また、比較例のP型トランジスタ112のゲート(G)に印加される電圧は、0Vであり、PchFET12(PchFET112)のゲート電圧(G)の閾値電圧を引いた値よりも低い。従って、第1実施形態のPchFET12および比較例のPchFET112は、オン状態となる。これにより、インバータ部2(図1参照)のスイッチング素子9のゲートには、電源電位(VCC)が印加されて、スイッチング素子9は、オン状態となる。

【0030】

また、第1実施形態のNchFET13のゲート(G)には、抵抗R5を介して、接地電位(0V)の電圧が印加される。一方、比較例のNchFET113のゲート(G)には、抵抗R1を介して、Lレベル(0V)の電圧が印加される。したがって、NchFET13(NchFET113)の閾値電圧よりも低いため、第1実施形態のNchFET13および比較例のNchFET113は、オフ状態となる。

【0031】

(期間B)

期間Bでは、抵抗R1を介して入力される駆動信号を、Lレベル(0V)からHレベル(VCC)に変化させる。これにより、第1実施形態のPchFET12のゲート(G)および比較例のPchFET112のゲート(G)に印加される電圧は、PchFETのゲート−ソース間の浮遊容量が抵抗R1を介して徐々に放電されるため、徐々に高くなる。その結果、ゲート(G)に印加される電圧が電源電位(VCC)から閾値電圧を引いた値に等しくなった際に、第1実施形態のPchFET12および比較例のPchFET112は、オフ状態となる。ここで、第1実施形態のPchFET12には、期間Aにおいて0Vよりツェナーダイオード14のツェナー電圧分高い電圧が印加されているので、第1実施形態のPchFET12のゲート(G)に印加される電圧の方が、比較例のPchFET112のゲート(G)に印加されている電圧よりも閾値電圧に早く到達する。その結果、第1実施形態のPchFET12は、比較例のPchFET112に比べて、早くオフ状態となる。その後、第1実施形態のPchFET12のゲート(G)に印加される電圧が、VCCと等しくなった時点で、PchFET12のゲート(G)には、抵抗R4を介してVCCの電圧が印加される。一方、比較例のPchFET112のゲート(G)には、抵抗R1を介してHレベル(VCC)の電圧が印加される。

【0032】

また、第1実施形態のNchFET13のゲート(G)および比較例のNchFET113のゲート(G)に印加される電圧は、ゲート−ソース間の浮遊容量が抵抗R1を介して徐々に充電されるため、徐々に高くなる。そして、第1実施形態のNchFET13のゲート(G)に印加される電圧、および、比較例のNchFET113のゲート(G)に印加される電圧が閾値電圧に等しくなった際に、第1実施形態のNchFET13および比較例のNchFET113は、オン状態となる。これにより、インバータ部2(図1参照)のスイッチング素子9のゲートには、接地電位(0V)が印加されて、オフ状態となる。

【0033】

その後、第1実施形態のNchFET13のゲート(G)および比較例のNchFET113のゲート(G)に印加される電圧は、閾値電圧よりもさらに高くなる。そして、抵抗R1とNchFET13のゲート(G)との間にツェナーダイオード15が設けられているとともに、NchFET13のゲート(G)が抵抗R5を介して接地電位(0V)に接続されているので、第1実施形態のNchFET13のゲート(G)には、電源電位(VCC)よりもツェナーダイオード15のツェナー電圧分低い電圧が印加される。一方、比較例のNchFET113のゲート(G)には、抵抗R1を介して電源電位(VCC)が印加される。

【0034】

なお、第1実施形態のNchFET13がオン状態になってから、PchFET12がオフ状態になるまでの間は、PchFET12とNchFET13との両方がオン状態となっている。同様に、比較例においても、NchFET113がオン状態になってから、PchFET112がオフ状態になるまでの間は、PchFET112とNchFET113との両方がオン状態となっている。そして、上記のように、第1実施形態のPchFET12が比較例のPchFET112に比べて早くオフ状態となり、第1実施形態のPchFET12およびNchFET13が両方オン状態である期間(同時オン期間)は、比較例のPchFET112およびNchFET113がオン状態である期間と比べて短くなる。

【0035】

(期間C)

期間Cでは、期間Bに引き続き、抵抗R4を介して、Hレベル(VCC)の駆動信号が入力される。これにより、第1実施形態のPchFET12のゲート(G)には、VCCの電圧が印加されるとともに、比較例のPchFET112のゲート(G)にも、VCCの電圧が印加される。したがって、第1実施形態のPchFET12および比較例のPchFET112は、オフ状態のままである。

【0036】

また、第1実施形態のNchFET13のゲート(G)には、VCCよりもツェナーダイオード15のツェナー電圧分低い電圧が印加されるとともに、比較例のNchFET113のゲート(G)には、抵抗R1を介してVCCの電圧が印加される。したがって、第1実施形態のNchFET12および比較例のNchFET112は、オフ状態のままである。その結果、インバータ部2(図1参照)のスイッチング素子9のゲートには、接地電位(0V)が印加されて、スイッチング素子9は、オフ状態を継続する。

【0037】

(期間D)

期間Dでは、抵抗R1を介して、入力される駆動信号が、Hレベル(VCC)からLレベル(0V)に変化する。これにより、第1実施形態のP型トランジスタ12のゲート(G)および比較例のP型トランジスタ112のゲート(G)においては、ゲート−ソース間の浮遊容量が抵抗R1を介して徐々に充電される。したがって、第1実施形態のPchFET12のゲート(G)および比較例のPchFET112のゲート(G)に印加される電圧はすぐには低くならず、徐々に低くなる。そして、第1実施形態のPchFET12のゲート(G)に印加される電圧と比較例のPchFET112のゲート(G)に印加される電圧とが、電源電位(VCC)から閾値電圧を引いた電圧よりも低くなった時点でPchFET12およびPchFET112はオフ状態からオン状態に変化する。その後、第1実施形態のPchFET12のゲート(G)には、0Vよりツェナーダイオード14のツェナー電圧分高い電圧が印加されるとともに、比較例のPchFET112のゲート(G)には、0Vの電圧が印加される。

【0038】

また、第1実施形態のNchFET13においては、ゲート−ソース間に浮遊容量が徐々に放電するため、ゲート(G)に印加される電圧は、電源電圧VCCよりもツェナーダイオード15のツェナー電圧分低い電圧から徐々に低くなる。NchFET13のゲート(G)に印加される電圧が閾値電圧より低くなった時点で、NchFET13はオン状態からオフ状態に変化する。一方、比較例のNchFET113のゲート(G)に印加される電圧は、電源電位VCCから徐々に低くなる。NchFET113のゲート(G)に印加される電圧が、閾値電圧より低くなった時点で、NchFET113はオン状態からオフ状態に変化する。その後、第1実施形態のNchFET13のゲート(G)に印加される電圧がゼロになった時点で、NchFET13のゲート(G)には、抵抗R5を介して接地電位0Vが印加される。また、比較例のNchFET113のゲート(G)には、抵抗R1を介してLレベル(0V)の電圧が印加される。ここで、第1実施形態のNchFET13には、期間Cにおいて電源電位(VCC)よりツェナーダイオード15のツェナー電圧分低い電圧が印加されているので、第1実施形態のNchFET13のゲート(G)に印加される電圧の方が、比較例のNchFET113のゲート(G)に印加されている電圧よりも閾値電圧に早く到達する。その結果、第1実施形態のNchFET13は、比較例のNchFET113に比べて、早くオフ状態となる。

【0039】

なお、第1実施形態のPchFET12がオン状態になってから、NchFET13がオフ状態になるまでの間は、PchFET12とNchFET13との両方がオン状態となっている。同様に、比較例のPchFET112がオン状態になってから、比較例のNchFET113がオフ状態になるまでの間は、比較例のPchFET112とNchFET113との両方がオン状態となっている。上記のように、第1実施形態のNchFET13が比較例のNchFET113に比べて早くオフ状態となることにより、第1実施形態のPchFET12およびNchFET13が両方オン状態である期間(同時オン期間)は、比較例のPchFET112およびNchFET113がオン状態である期間と比べて短くなる。

【0040】

第1実施形態では、上記のように、ツェナーダイオード14およびツェナーダイオード15が、それぞれ、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせることによって、PchFET12およびNchFET13のゲート(G)に印加される電圧と、PchFET12およびNchFET13のゲート(G)の閾値電圧との差が小さくなる。これにより、ゲート(G)に印加される電圧が増加し始めてから、PchFET12がオン状態からオフ状態に切り替わる時間を短縮することができるとともに、ゲート(G)に印加される電圧が減少し始めてから、NchFET13がオン状態からオフ状態に切り替わる時間を短縮することができる。その結果、PchFET12とNchFET13との両方がオン状態になる時間を短縮することができるので、短絡電流に起因する消費電力の増大を抑制することができるとともに、スイッチング素子9を高速スイッチングさせることができる。

【0041】

また、第1実施形態では、上記のように、PchFET12の閾値電圧と、ツェナーダイオード14およびツェナーダイオード15の各ツェナー電圧と、NchFET13の閾値電圧とを加算した値が、電源電位(VCC)以上になるように構成する。これにより、PchFET12とNchFET13とが同時にオン状態になる期間を略ゼロにすることができる。

【0042】

(第2実施形態)

次に、図5を参照して、第2実施形態のモータ制御装置100aのゲート駆動回路11aについて説明する。この第2実施形態では、駆動信号が入力される入力側とPchFET12およびNchFET13との間に、それぞれ、コンデンサ16および17が設けられている。なお、コンデンサ16および17は、それぞれ、本発明の「第1コンデンサ」および「第2コンデンサ」の一例である。

【0043】

図5に示すように、第2実施形態のモータ制御装置100aのゲート駆動回路11aでは、駆動信号が入力される入力側(抵抗R1)とPchFET12との間には、ツェナーダイオード14と並列にコンデンサ16が設けられている。コンデンサ16は、PchFET12がオン状態からオフ状態に移行する際のゲート(G)に印加される電圧の増加率を大きくする機能を有する。コンデンサ16の電極16aは、抵抗R4、ツェナーダイオード14およびPchFET12のゲート(G)に接続されているとともに、電極16bは、抵抗R1に接続されている。

【0044】

また、第2実施形態では、駆動信号が入力される入力側とNchFET13との間には、ツェナーダイオード15と並列にコンデンサ17が設けられている。コンデンサ17は、NchFET13がオン状態からオフ状態に移行する際のゲート(G)に印加される電圧の減少率を大きくする機能を有する。コンデンサ17の電極17aは、抵抗R1に接続されているとともに、電極17bは、抵抗R5、ツェナーダイオード15およびNchFET13のゲート(G)に接続されている。なお、第2実施形態のその他の構成は、上記第1実施形態と同様である。

【0045】

次に、図6を参照して、本発明の第2実施形態によるモータ制御装置100aのゲート駆動回路11aの動作を図4に示す比較例と比較しながら説明する。

【0046】

(期間E)

図6に示すように、期間Eでは、抵抗R1を介して、Lレベル(0V)の駆動信号が入力される。ここで、第2実施形態では、上記第1実施形態と同様に、PchFET12のゲート(G)には、0Vよりもツェナーダイオード14のツェナー電圧分高い電圧が印加される。一方、比較例では、PchFET112のゲート(G)に印加される電圧(図6の破線)は、Lレベル(0V)である。前述のとおり、ツェナーダイオード14のツェナー電圧は、電源電位(VCC)からPchFET12のゲート(G)の閾値電圧を引いた値より低くなっている。その結果、PchFET12(PchFET112)は、オン状態となる。また、第2実施形態のコンデンサ16はツェナーダイオード14のツェナー電圧で充電される。また、このときPchFET12のゲート−ソース間浮遊容量は、電源電位(VCC)からツェナーダイオード14のツェナー電圧で充電されている。

【0047】

また、第2実施形態のNchFET13のゲート(G)には、抵抗R5を介して、0Vの電圧が印加される。同様に、比較例のNchFET113のゲート(G)には、抵抗R1を介して、Lレベル(0V)の電圧が印加される。その結果、NchFET13およびNchFET113は、オフ状態となる。また、コンデンサ17の電極17aと電極17bとの間の電位差は、0Vである。

【0048】

(期間F)

期間Fでは、抵抗R1を介して入力される駆動信号を、Lレベル(0V)からHレベル(VCC)に変化させる。このとき、第2実施形態のPchFET12のゲート(G)および比較例(図4参照)のPchFET112のゲート(G)に印加される電圧は、ゲート−ソース間の浮遊容量が徐々に放電するので、徐々に高くなる。ここでPchFET12のゲート−ソース間の浮遊容量は、R1を介した放電ルートとR4を介した放電ルートの二つの放電ルートがある。これに対してPchFET112のゲート−ソース間の浮遊容量はR1を介した放電ルートのみである。従って、PchFET12のゲート−ソース間浮遊容量のほうが、PchFET112のゲート−ソース間浮遊容量より早く放電するため、PchFET12のゲート(G)に印加される電圧の増加率(傾き)は、比較例のPchFET112のゲート(G)に印加される電圧の増加率よりも大きくなる。そして、第2実施形態のPchFET12および比較例のPchFET112は、ゲート(G)に印加される電圧が電源電位(VCC)からゲート(G)の閾値電圧を引いた電圧値(ここではターンオフ電圧と呼ぶ)より高くなった時点でオフ状態となる。ここで、第2実施形態のPchFET12には、期間Eにおいて0Vよりツェナーダイオード14のツェナー電圧分高い電圧が印加されているとともに印加される電圧の増加率(傾き)が大きくなるので、第2実施形態のPchFET12のゲート(G)に印加される電圧の方が、比較例のPchFET112のゲート(G)に印加されている電圧よりもターンオフ電圧に早く到達する。その結果、第2実施形態のPchFET12は、比較例のPchFET112に比べて、早くオフ状態となる。その後、第2実施形態のPchFET12のゲート(G)に印加される電圧は、徐々に高くなるが、一般には容量の大きさからPchFET12のゲート−ソース間の浮遊容量がコンデンサ16よりも先に蓄積された電荷がゼロとなり、このときPchFET12に印加される電圧は、電源電位VCCとなる。その後は、コンデンサ16のみが放電するが、この放電電流によりPchFET12のゲート−ソース間の浮遊容量は、放電時とは逆の極性で充電される。これにより、PchFET12のゲート(G)に印加される電圧は、電源電位(VCC)を超えて高くなる。このときコンデンサ16の放電電流は、抵抗R4とPchFET12のゲート−ソース間の浮遊容量に分流して流れる。抵抗R4を流れる電流はPchFET12のゲート−ソース間の浮遊容量の充電電圧に比例して大きくなる。これに対してコンデンサ16の放電電流は、放電が進むにつれ減少している。従ってある時点で、抵抗R4を流れる電流とコンデンサ16の放電電流は等しくなる。このときPchFET12のゲート−ソース間の浮遊容量の充電電流はゼロとなり、PchFET12のゲート(G)に印加される電圧はピーク値となる。以後は、コンデンサ16とPchFET12のゲート−ソース間の浮遊容量の双方の放電電流が抵抗R4を流れ、PchFET12のゲート(G)に印加される電圧は徐々に低くなる。双方の放電が完了した時点で、PchFET12のゲート(G)に印加される電圧は電源電位(VCC)となる。これに対して比較例のPchFET12のゲート(G)に印加される電圧は、徐々に高くなって電源電位(VCC)になる。

【0049】

また、第2実施形態のNchFET13のゲート(G)および比較例のNchFET113のゲート(G)に印加される電圧は、PchFET12のゲート(G)と同様徐々に高くなる。そして、第2実施形態のNchFET13のゲート(G)に印加される電圧、および、比較例のNchFET113のゲート(G)に印加される電圧が、閾値電圧と等しくなった際に、第2実施形態のNchFET13および比較例のNchFET113は、オン状態となる。そして、インバータ部2(図1参照)のスイッチング素子9のゲートには、接地電位(0V)が印加されて、オフ状態となる。その後、NchFET13のゲート(G)に印加される電圧は、徐々に高くなり、電源電位(VCC)よりもツェナーダイオード15のツェナー電圧分低い電圧になる。また、比較例のNchFET113のゲート(G)に印加される電圧は、電源電位(VCC)になる。

【0050】

そして、上記のように、第2実施形態のPchFET12が比較例のPchFET112に比べて早くオフ状態となるため、第2実施形態のPchFET12およびNchFET13が両方オン状態である期間(同時オン期間)は、比較例のPchFET112およびNchFET113がオン状態である期間と比べて短くなる。

【0051】

(期間G)

期間Gでは、期間Fに引き続き、抵抗R1を介して、Hレベル(VCC)の駆動信号が入力される。これにより、第2実施形態のPchFET12および比較例のPchFET112は、オフ状態のままである。また、第2実施形態のNchFET13および比較例のNchFET113は、オン状態のままである。

【0052】

(期間H)

期間Hでは、抵抗R1を介して、入力される駆動信号が、Hレベル(VCC)からLレベル(0V)に変化する。これにより、第2実施形態のPchFET12のゲート(G)および比較例のPchFET112のゲート(G)に印加される電圧は、徐々に低くなる。第2実施形態、比較例とも、PchFET12またはNchFET112のゲート(G)に印加される電圧が、電源電位(VCC)からPchFET12またはPchFET112のゲート(G)の閾値電圧を引いた電圧(ここではターンオン電圧と呼ぶ)に等しくなったときに、PchFET12および比較例のPchFET112は、オン状態となる。その後、第2実施形態のPchFET12のゲート(G)には、0Vよりツェナーダイオード14のツェナー電圧分高い電圧が印加されるとともに、比較例のPchFET112のゲート(G)には、0Vの電圧が印加される。

【0053】

また、第2実施形態のNchFET13のゲート(G)および比較例のNchFET113のゲート(G)に印加される電圧は、ゲート−ソース間の浮遊容量がR1を介して徐々に放電するので、徐々に低くなる。このとき期間FにおけるPchFET12と同様、比較例に比べて抵抗R5を流れる放電電流が加算されるため、NchFET13のゲート(G)に印加される電圧は、比較例のNchFET113のゲート(G)に印加される電圧よりも増加率(傾き)が大きくなる。そして、第2実施形態のNchFET13および比較例のNchFET113は、ゲート(G)に印加される電圧がゲート(G)の閾値電圧より低くなった時点でオフ状態となる。その後、第2実施形態のNchFET13のゲート(G)に印加される電圧は、徐々に増加するが、一般には容量の大きさからNchFET13のゲート−ソース間の浮遊容量がコンデンサ17よりも先に蓄積された電荷がゼロとなり、このときNchFET13に印加される電圧は、Lレベル(0V)となる。その後は、コンデンサ17のみが放電するが、この放電電流によりNchFET13のゲート−ソース間の浮遊容量は、放電時とは逆の極性で充電される。これにより、NchFET13のゲート(G)に印加される電圧は、Lレベル(0V)よりも低くなる。このときコンデンサ17の放電電流は、抵抗R5とNchFET13のゲート−ソース間の浮遊容量に分流して流れる。抵抗R5を流れる電流はNchFET13のゲート−ソース間の浮遊容量の充電電圧に比例して大きくなる。これに対してコンデンサ17の放電電流は、放電が進むにつれ減少している。従ってある時点で、抵抗R5を流れる電流とコンデンサ17の放電電流は等しくなる。このときNchFET13のゲート−ソース間の浮遊容量の充電電流はゼロとなり、NchFET13のゲート(G)に印加される電圧は最低値となる。以後は、コンデンサ17とNchFET13のゲート−ソース間の浮遊容量の双方の放電電流が抵抗R5を流れ、NchFET13のゲート(G)に印加される電圧は徐々に高くなる。双方の放電が完了した時点で、NchFET13のゲート(G)に印加される電圧はLレベル(0V)となる。これに対して比較例のNchFET113のゲート(G)に印加される電圧は、徐々に低くなってLレベル(0V)となる。ここで、第2実施形態のNchFET13には、期間Gにおいて電源電位(VCC)よりツェナーダイオード15のツェナー電圧分低い電圧が印加されているとともに、第2実施形態のNchFET13に印加される電圧の減少率が比較例のNchFET113に印加される電圧の減少率よりも大きいので、第2実施形態のNchFET13のゲート(G)に印加される電圧の方が、比較例のNchFET113のゲート(G)に印加されている電圧よりも閾値電圧に早く到達する。その結果、第2実施形態のNchFET13は、比較例のNchFET113に比べて、早くオフ状態となる。

【0054】

そして、上記のように、第2実施形態のNchFET13が比較例のNchFET113に比べて早くオフ状態となるため、第2実施形態のPchFET12およびNchFET13が両方オン状態である期間(同時オン期間)は、比較例のPchFET112およびNchFET113がオン状態である期間と比べて短くなる。

【0055】

第2実施形態では、上記のように、PchFET12とNchFET13との両方がオン状態になる時間をより短縮することができる。その結果、短絡電流に起因する消費電力の増大をより抑制することができる。

【0056】

(シミュレーション)

次に、図7を参照して、比較例(図4参照)、第1実施形態(図2参照)および第2実施形態(図5参照)のゲート駆動回路の消費電力について行ったシミュレーションについて説明する。

【0057】

シミュレーションの条件としては、比較例のPchFET112およびNchFET113と、第1実施形態(第2実施形態)のPchFET12およびNchFET13には、Lレベルの電圧(0V)とHレベルの電圧(13V)とが印加されるとする。また、Lレベルの電圧(0V)とHレベルの電圧(13V)とは、100kHzの周期で交互に印加されるとする。また、比較例のPchFET112およびNchFET113、第1実施形態(第2実施形態)のPchFET12およびNchFET13に接続される抵抗R1の抵抗は、130Ωとする。また、比較例のPchFET112およびNchFET113の間、および、第1実施形態(第2実施形態)のPchFET12およびNchFET13の間に設けられる抵抗R2およびR3の抵抗は、それぞれ、10Ωおよび1Ωとする。また、第1実施形態(第2実施形態)のPchFET12およびNchFET13にそれぞれ接続される抵抗R4およびR5の抵抗は、10kΩとする。また、第2実施形態のコンデンサ16および17の静電容量は、それぞれ、220pFとする。また、比較例のPchFET112、第1実施形態(第2実施形態)のPchFET12の閾値電圧は、それぞれ、1.7Vとする。また、比較例のNchFET113、第1実施形態(第2実施形態)のNchFET13の閾値電圧は、それぞれ、1.15Vとする。

【0058】

上記のような条件によりシミュレーションを行ったところ、比較例によるゲート駆動回路111(図4参照)では、PchFET112およびNchFET113に印加される電圧がLレベル(0V)からHレベル(13V)に変化する際(図3の期間B参照)に、PchFET112とNchFET113との両方がオン状態である期間が105nsになることが判明した。また、PchFET112およびNchFET113に印加される電圧がHレベル(13V)からLレベル(0V)に変化する際(図3の期間D参照)に、PchFET112とNchFET113との両方がオン状態である期間が70nsになることが判明した。その結果、PchFET112から抵抗R2およびR3を介してNchFET113に短絡電流が流れることにより消費される電力は、0.27Wになることが判明した。

【0059】

なお、PchFET112およびNchFET113に印加される電圧がLレベル(0V)からHレベル(13V)に変化し始めてから、スイッチング素子9がオン状態からオフ状態に変化し始めるまでの時間(ON遅延)は、13nsになることが確認された。また、PchFET112およびNchFET113に印加される電圧がHレベル(13V)からLレベル(0V)に変化し始めてから、スイッチング素子9がオフ状態からオン状態(OFF遅延)に変化し始めるまでの時間は、65nsになることが確認された。

【0060】

次に、第1実施形態によるゲート駆動回路11(図2参照)では、PchFET12およびNchFET13に印加される電圧がLレベル(0V)からHレベル(13V)に変化する際(図3の期間B参照)に、PchFET12とNchFET13との両方がオン状態である期間が58nsになることが判明した。また、PchFET12およびNchFET13に印加される電圧がHレベル(13V)からLレベル(0V)に変化する際(図3の期間D参照)に、PchFET12とNchFET13との両方がオン状態である期間が0sになることが判明した。すなわち、第1実施形態のPchFET12とNchFET13との両方がオン状態である合計の期間58ns(=58ns+0s)は、比較例のPchFET112とNchFET113との両方がオン状態である合計の期間175ns(=105ns+70ns)よりも短くなることが確認された。つまり、ツェナーダイオード14および15を設けることにより、PchFET12とNchFET13との両方がオン状態である期間が短くなることが確認された。その結果、PchFET12から抵抗R2およびR3を介してNchFET13に短絡電流が流れることにより消費される電力は、0.09Wになり、比較例(0.27W)と比べて小さくなることが判明した。

【0061】

なお、PchFET12およびNchFET13に印加される電圧がLレベル(0V)からHレベル(13V)に変化し始めてから、スイッチング素子9がオン状態からオフ状態に変化し始めるまでの時間(ON遅延)は、15nsになることが確認された。また、PchFET12およびNchFET13に印加される電圧がHレベル(13V)からLレベル(0V)に変化し始めてから、スイッチング素子9がオフ状態からオン状態に変化し始めるまでの時間(OFF遅延)は、18nsになることが確認された。

【0062】

次に、第2実施形態によるゲート駆動回路11(図5参照)では、PchFET12およびNchFET13に印加される電圧がLレベル(0V)からHレベル(13V)に変化する際(図6の期間F参照)に、PchFET12とNchFET13との両方がオン状態である期間が15nsになることが判明した。また、PchFET12およびNchFET13に印加される電圧がHレベル(13V)からLレベル(0V)に変化する際(図6の期間H参照)に、PchFET12とNchFET13との両方がオン状態である期間が0sになることが判明した。すなわち、第2実施形態のPchFET12とNchFET13との両方がオン状態である合計の期間15ns(=15ns+0s)は、比較例のPchFET112とNchFET113との両方がオン状態である合計の期間175ns(=105ns+70ns)、および、第1実施形態のPchFET12とNchFET13との両方がオン状態である合計の期間58ns(=58ns+0s)よりも短くなることが確認された。つまり、ツェナーダイオード14および15と、コンデンサ16および17とを設けることにより、PchFET12とNchFET13との両方がオン状態である期間がより短くなることが確認された。その結果、PchFET12から抵抗R2およびR3を介してNchFET13に短絡電流が流れることにより消費される電力は、0.02Wになり、比較例(0.27W)および第1実施形態(0.09W)と比べて小さくなることが判明した。

【0063】

なお、PchFET12およびNchFET13に印加される電圧がLレベル(0V)からHレベル(13V)に変化し始めてから、スイッチング素子9がオン状態からオフ状態に変化し始めるまでの時間(ON遅延)は、上記第1実施形態と同じ15nsになることが確認された。また、PchFET12およびNchFET13に印加される電圧がHレベル(13V)からLレベル(0V)に変化し始めてから、スイッチング素子9がオフ状態からオン状態になるまでの時間(OFF遅延)は、上記第1実施形態と同じ18nsになることが確認された。

【0064】

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれる。

【0065】

たとえば、上記第1および第2実施形態では、入力側とPchFETとの間、および、入力側とNchFETとの間の両方にツェナーダイオードを設ける例を示したが、本発明はこれに限られない。たとえば、入力側とPchFETとの間、または、入力側とNchFETとの間の一方にツェナーダイオードを設けてもよい。

【0066】

また、上記第1および第2実施形態では、入力側とPchFETとの間、および、入力側とNchFETとの間の両方にツェナーダイオードを設ける例を示したが、本発明はこれに限られない。たとえば、入力側とPchFETとの間、および、入力側とNchFETとの間にツェナーダイオード以外のダイオードを設けてもよい。

【0067】

また、上記第1および第2実施形態では、インバータ部に含まれるスイッチング素子が、電解効果トランジスタと還流ダイオードとから構成されている例を示したが、本発明はこれに限られない。たとえば、スイッチング素子をIGBTと還流ダイオードとから構成してもよい。

【0068】

また、上記第2実施形態では、入力側とPchFETとの間、および、入力側とNchFETとの間の両方にコンデンサを設ける例を示したが、本発明はこれに限られない。たとえば、入力側とP型の電界効果トランジスタとの間、または、入力側とNchFETとの間の一方にコンデンサを設けてもよい。

【0069】

また、上記第2実施形態では、入力側とPchFETとの間、および、入力側とNchFETとの間に、それぞれ、ツェナーダイオードとコンデンサとを並列に設ける例を示したが、本発明はこれに限られない。たとえば、図8に示す第2実施形態の第1変形例によるゲート駆動回路11bのように、入力側とPchFET12との間にツェナーダイオード14とコンデンサ16とに並列に放電用ダイオード18を設けるとともに、ツェナーダイオード14とPchFET12のゲート(G)との間に逆流防止ダイオード19を設けてもよい。さらに、入力側とNchFET13との間にツェナーダイオード15とコンデンサ17とに並列に放電用ダイオード20を設けるとともに、ツェナーダイオード15とNchFET13のゲート(G)との間に逆流防止ダイオード21を設けてもよい。これにより、放電用ダイオード18および放電用ダイオード20を介してPchFET12およびNchFET13に電圧を印加することができるので、PchFET12およびNchFET13の容量が大きくなった場合でも、PchFET12およびNchFET13のオンオフを容易に行うことができる。

【0070】

さらなる第2実施形態の第2変形例を図9に示す。第2実施形態(図5)と異なる点は、図9に示すように、ツェナーダイオード14を、電源電位VCCとPchFET12のゲート(G)との間に配置するとともに、ツェナーダイオード15を、接地電位(0V)とNchFET13のゲート(G)との間に配置したことである。なお、ツェナーダイオード14(ツェナーダイオード15でも同様)のツェナー電圧はPchFET12(NchFET13でも同様)の閾値電圧よりも高く設定されている。また、PchFET12(NchFET13でも同様)のオン時にPchFET12のゲートとソース間電圧をツェナー電圧に維持するため、コンデンサ16と並列に抵抗R6(R6≪R4)が、およびコンデンサ17と並列に抵抗R7(R7≪R5)が設けられている。これによりPchFET12のオン時に抵抗R6を流れている電流の一部がツェナーダイオード14を流れるので、PchFET12のゲートとソース間電圧はツェナー電圧に維持される。以上はNchFET13においても同様である。

【0071】

この第2実施形態の第2変形例の場合、PchFET12のオン時、ゲート(G)にはツェナーダイオード14のツェナー電圧が印加(ツェナー電圧で抑制)され、NchFET13のオン時、ゲート(G)にはツェナーダイオード15のツェナー電圧が印加(ツェナー電圧で抑制)されており、第2実施形態で説明した動作と同様にオフ動作への切り替わりに際しては、比較例のPchFET112およびNchFET113のゲート(G)に印加されている電圧よりも閾値電圧に早く到達する。さらにコンデンサ16は、PchFET12がオン状態からオフ状態に移行する際のゲート(G)に印加される電圧の増加率を大きくし、コンデンサ17は、NchFET13がオン状態からオフ状態に移行する際のゲート(G)に印加される電圧の減少率を大きくする機能を有するので、この点からも閾値電圧に早く到達する。このように、この変形例は第2実施形態と回路構成に上述の相違部分はあるが、第2実施形態と同様の効果が得られる。

【0072】

また、第1実施形態(図2)、第2実施形態(図5)、第2実施形態の第1変形例(図8)、および、第2実施形態の第2変形例(図9)では、上記のように、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるためにツェナーダイオード14および15を用いる例を示したが、本発明はこれに限られない。たとえば、これらツェナーダイオードを図10に示すダイオードで構成する回路で置き換えてもよい。図10に示すように、通常のダイオードを用いる場合には、ツェナー電圧(降伏電圧)に相当する電圧をダイオードの順電圧降下で代用し、ツェナー電圧に相当する大きさの電圧とするために1つ以上(図10では、3つ)のダイオード14a(15a)を直列に接続している。またツェナーダイオードの順方向特性を代用するために、この1つ以上のダイオード14a(15a)の直列接続体と逆並列に1個のダイオード14b(15b)を接続している。

【0073】

上述のようにダイオード順方向降下電圧がツェナーダイオードの降伏電圧に略等しくなるように1つ以上のダイオード14a(15a)を直列接続した直列接続体と、直列接続体とは逆極性にしたダイオード14b(15b)とを並列接続した並列接続体を準備する。そしてツェナーダイオードのカソード(K)側が逆極性にしたダイオードのカソード側に、ツェナーダイオードのアノード(A)側が逆極性にしたダイオードのアノード側になるようにツェナーダイオードを並列接続体に置換する。

【符号の説明】

【0074】

1 コンバータ部(順変換部)

2 インバータ部(電力変換部)

3 ゲート駆動回路部

4 制御電源

5 制御部

6 I/O

7 ダイオード

8 平滑用コンデンサ

9 スイッチング素子

11、11a、11b ゲート駆動回路

12 PchFET(P型電界効果トランジスタ)

13 NchFET(N型電界効果トランジスタ)

14 ツェナーダイオード(ダイオード、第1ツェナーダイオード)

15 ツェナーダイオード(ダイオード、第2ツェナーダイオード)

16 コンデンサ(第1コンデンサ)

17 コンデンサ(第2コンデンサ)

18、20 放電用ダイオード

100、100a モータ制御装置(電力変換装置)

【特許請求の範囲】

【請求項1】

スイッチング素子のゲートを駆動するゲート駆動回路であって、

P型電界効果トランジスタと、

前記P型電界効果トランジスタに直列に接続されるN型電界効果トランジスタと、

前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートのうちの少なくとも一方に接続されるとともに、電源に接続されているダイオードとを備え、

前記ダイオードは、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせるように構成されている、ゲート駆動回路。

【請求項2】

前記ダイオードは、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせるためのツェナーダイオードを含む、請求項1に記載のゲート駆動回路。

【請求項3】

前記ツェナーダイオードは、前記P型電界効果トランジスタのゲートに印加される電圧を増加させることにより前記P型電界効果トランジスタのゲートに印加される電圧を前記P型電界効果トランジスタのゲートの閾値電圧側にシフトさせるための第1ツェナーダイオードと、前記N型電界効果トランジスタのゲートに印加される電圧を減少させることにより前記N型電界効果トランジスタのゲートに印加される電圧を前記N型電界効果トランジスタのゲートの閾値電圧側にシフトさせるための第2ツェナーダイオードとを含む、請求項2に記載のゲート駆動回路。

【請求項4】

前記P型電界効果トランジスタの閾値電圧と、前記第1ツェナーダイオードの降伏電圧と、前記第2ツェナーダイオードの降伏電圧と、前記N型電界効果トランジスタの閾値電圧とを加算した合計の電圧は、前記電源の電圧以上になるように構成されている、請求項3に記載のゲート駆動回路。

【請求項5】

前記第1ツェナーダイオードは、前記ゲート駆動回路を駆動する信号が入力される入力側に接続されるとともに、前記第1ツェナーダイオードの前記ゲート駆動回路を駆動する信号が入力される入力側とは反対側と、前記P型電界効果トランジスタのゲートとは、前記電源に接続されている、請求項3または4に記載のゲート駆動回路。

【請求項6】

前記第2ツェナーダイオードは、前記ゲート駆動回路を駆動する信号が入力される入力側に接続されるとともに、前記第2ツェナーダイオードの前記ゲート駆動回路を駆動する信号が入力される入力側とは反対側と、前記N型電界効果トランジスタのゲートとは、接地電位に接続されている、請求項3〜5のいずれか1項に記載のゲート駆動回路。

【請求項7】

前記ダイオードは、ダイオード順方向降下電圧がツェナーダイオードの降伏電圧に略等しくなるように1つ以上のダイオードを直列接続した直列接続体と、前記直列接続体とは逆極性にしたダイオードとを並列接続した並列接続体を含む、請求項1に記載のゲート駆動回路。

【請求項8】

ゲート駆動回路を駆動する信号が入力される入力側と、前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートのうちの少なくとも一方との間に、前記ダイオードと並列に設けられるコンデンサをさらに備える、請求項1〜7のいずれか1項に記載のゲート駆動回路。

【請求項9】

前記コンデンサは、前記P型電界効果トランジスタがオン状態からオフ状態に移行する際のゲートに印加される電圧の増加率を大きくするための第1コンデンサと、前記N型電界効果トランジスタがオン状態からオフ状態に移行する際のゲートに印加される電圧の減少率を大きくするための第2コンデンサとを含む、請求項8に記載のゲート駆動回路。

【請求項10】

前記ゲート駆動回路を駆動する信号が入力される入力側と、前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートのうちの少なくとも一方との間に、前記ダイオードおよび前記コンデンサと並列に設けられる放電用ダイオードをさらに備える、請求項8または9に記載のゲート駆動回路。

【請求項11】

前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートは、各々抵抗値の等しい第1の抵抗を介して前記電源に接続され、

ゲート駆動回路を駆動する信号が入力される入力側と、前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートとの間には、前記第1の抵抗よりも抵抗が1桁以上小さい第2の抵抗が配置され、

前記ダイオードは、前記P型電界効果トランジスタのゲートとソース、前記N型電界効果トランジスタのゲートとソースのうちの少なくとも一方との間に前記ゲートがアノード、前記ソースがカソードに接続されるように設けられるツェナーダイオードを含む、請求項1に記載のゲート駆動回路。

【請求項12】

複数のスイッチング素子を含む電力変換部と、

前記複数のスイッチング素子のゲートを駆動するゲート駆動回路とを備え、

前記ゲート駆動回路は、

P型電界効果トランジスタと、

前記P型電界効果トランジスタに接続されるN型電界効果トランジスタと、

前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートのうちの少なくとも一方に接続されるとともに、電源に接続されているダイオードとを含み、

前記ダイオードは、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせるように構成されている、電力変換装置。

【請求項1】

スイッチング素子のゲートを駆動するゲート駆動回路であって、

P型電界効果トランジスタと、

前記P型電界効果トランジスタに直列に接続されるN型電界効果トランジスタと、

前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートのうちの少なくとも一方に接続されるとともに、電源に接続されているダイオードとを備え、

前記ダイオードは、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせるように構成されている、ゲート駆動回路。

【請求項2】

前記ダイオードは、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせるためのツェナーダイオードを含む、請求項1に記載のゲート駆動回路。

【請求項3】

前記ツェナーダイオードは、前記P型電界効果トランジスタのゲートに印加される電圧を増加させることにより前記P型電界効果トランジスタのゲートに印加される電圧を前記P型電界効果トランジスタのゲートの閾値電圧側にシフトさせるための第1ツェナーダイオードと、前記N型電界効果トランジスタのゲートに印加される電圧を減少させることにより前記N型電界効果トランジスタのゲートに印加される電圧を前記N型電界効果トランジスタのゲートの閾値電圧側にシフトさせるための第2ツェナーダイオードとを含む、請求項2に記載のゲート駆動回路。

【請求項4】

前記P型電界効果トランジスタの閾値電圧と、前記第1ツェナーダイオードの降伏電圧と、前記第2ツェナーダイオードの降伏電圧と、前記N型電界効果トランジスタの閾値電圧とを加算した合計の電圧は、前記電源の電圧以上になるように構成されている、請求項3に記載のゲート駆動回路。

【請求項5】

前記第1ツェナーダイオードは、前記ゲート駆動回路を駆動する信号が入力される入力側に接続されるとともに、前記第1ツェナーダイオードの前記ゲート駆動回路を駆動する信号が入力される入力側とは反対側と、前記P型電界効果トランジスタのゲートとは、前記電源に接続されている、請求項3または4に記載のゲート駆動回路。

【請求項6】

前記第2ツェナーダイオードは、前記ゲート駆動回路を駆動する信号が入力される入力側に接続されるとともに、前記第2ツェナーダイオードの前記ゲート駆動回路を駆動する信号が入力される入力側とは反対側と、前記N型電界効果トランジスタのゲートとは、接地電位に接続されている、請求項3〜5のいずれか1項に記載のゲート駆動回路。

【請求項7】

前記ダイオードは、ダイオード順方向降下電圧がツェナーダイオードの降伏電圧に略等しくなるように1つ以上のダイオードを直列接続した直列接続体と、前記直列接続体とは逆極性にしたダイオードとを並列接続した並列接続体を含む、請求項1に記載のゲート駆動回路。

【請求項8】

ゲート駆動回路を駆動する信号が入力される入力側と、前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートのうちの少なくとも一方との間に、前記ダイオードと並列に設けられるコンデンサをさらに備える、請求項1〜7のいずれか1項に記載のゲート駆動回路。

【請求項9】

前記コンデンサは、前記P型電界効果トランジスタがオン状態からオフ状態に移行する際のゲートに印加される電圧の増加率を大きくするための第1コンデンサと、前記N型電界効果トランジスタがオン状態からオフ状態に移行する際のゲートに印加される電圧の減少率を大きくするための第2コンデンサとを含む、請求項8に記載のゲート駆動回路。

【請求項10】

前記ゲート駆動回路を駆動する信号が入力される入力側と、前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートのうちの少なくとも一方との間に、前記ダイオードおよび前記コンデンサと並列に設けられる放電用ダイオードをさらに備える、請求項8または9に記載のゲート駆動回路。

【請求項11】

前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートは、各々抵抗値の等しい第1の抵抗を介して前記電源に接続され、

ゲート駆動回路を駆動する信号が入力される入力側と、前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートとの間には、前記第1の抵抗よりも抵抗が1桁以上小さい第2の抵抗が配置され、

前記ダイオードは、前記P型電界効果トランジスタのゲートとソース、前記N型電界効果トランジスタのゲートとソースのうちの少なくとも一方との間に前記ゲートがアノード、前記ソースがカソードに接続されるように設けられるツェナーダイオードを含む、請求項1に記載のゲート駆動回路。

【請求項12】

複数のスイッチング素子を含む電力変換部と、

前記複数のスイッチング素子のゲートを駆動するゲート駆動回路とを備え、

前記ゲート駆動回路は、

P型電界効果トランジスタと、

前記P型電界効果トランジスタに接続されるN型電界効果トランジスタと、

前記P型電界効果トランジスタのゲートおよび前記N型電界効果トランジスタのゲートのうちの少なくとも一方に接続されるとともに、電源に接続されているダイオードとを含み、

前記ダイオードは、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートに印加される電圧を、前記P型電界効果トランジスタおよび前記N型電界効果トランジスタのうちの少なくとも一方のゲートの閾値電圧側にシフトさせるように構成されている、電力変換装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−42632(P2013−42632A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2011−179314(P2011−179314)

【出願日】平成23年8月19日(2011.8.19)

【出願人】(000006622)株式会社安川電機 (2,482)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成23年8月19日(2011.8.19)

【出願人】(000006622)株式会社安川電機 (2,482)

【Fターム(参考)】

[ Back to top ]