Fターム[5J055EZ65]の内容

Fターム[5J055EZ65]に分類される特許

1 - 19 / 19

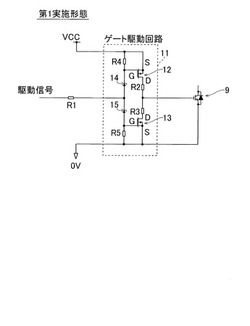

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

半導体デバイス駆動回路及び半導体装置

【課題】電源電圧が変動しても半導体デバイスのオン動作及びオフ動作を安定して駆動できる半導体デバイス駆動回路を得る。

【解決手段】ドライブ回路10は、入力回路11より得られる制御信号S11に基づき、インバータG4から電源電圧VCCにより決定される“H”(オンレベル)、あるいは接地電圧GNDにより決定される“L”(オフレベル)の出力電圧VOUT1を駆動信号として半導体デバイスQ1のゲートに出力する。基準電源部14は抵抗R1及びR2の直列接続により、電源電圧VCC,接地電圧GND間の電位差を所定の分圧比率(抵抗R1及びR2による抵抗比)で分圧して得られる電圧が基準電圧VREF1として得られる。バッファ回路8は基準電圧VREF1により決定される基準信号となる出力電圧VOUT2を半導体デバイスQ1のソースに付与する。

(もっと読む)

表示装置

【課題】表示装置の走査信号線の駆動回路において、走査信号線の出力波形なまりを改善し、表示品質を高めた表示装置を提供する。

【解決手段】表示装置は、複数の信号線Gnに対して、順に画素トランジスタを導通させる電位であるアクティブ電位を印加する駆動回路210を備え、前記駆動回路210は、前記複数の信号線のうちの一の信号線である出力信号線の一端に、より上位の前記出力信号線において出力されるアクティブ電位が入力されることに起因して、クロック信号を印加してアクティブ電位を出力させる主駆動回路240と、前記出力信号線の他端、及び前記クロック信号の信号線が、ソース/ドレインを介して接続されたトランジスタである補助トランジスタを含む補助駆動回路250と、を有する。

(もっと読む)

スイッチ回路及び半導体回路

【課題】 超音波診断装置等に適用され、送信信号または反射信号の電位変動に対しスイッチの誤動作や素子の破壊を起こすことなく、生体からの反射信号を広帯域、低雑音で受信回路に伝送するT/Rスイッチ回路を実現する。

【解決手段】 2つのMOSトランジスタのソースを共通に直列接続した共有ソース端子と、双方向スイッチ回路のゲート端子を共通に接続した共有ゲート端子と、2つのMOSトランジスタのドレインが入出力端子に接続されて構成される双方向スイッチ回路と、共有ゲート端子と共有ソース端子に接続され共有ソース端子の電位変動に対して共有ゲート端子の電位を同相で追従させ、スイッチのオンまたはオフ信号を共有ゲート端子に送るフローティングゲート電圧制御回路と、によりスイッチ回路を構成する。

(もっと読む)

信号伝達回路及びこれを用いたスイッチ駆動装置

【課題】入力信号をレベルシフトして出力するレベルシフト回路を有しながらも、電源の電圧変動等による誤信号の出力を抑えることが可能となる信号伝達回路を提供する。

【解決手段】第1入力信号および第2入力信号の各々をレベルシフトし、それぞれ第1シフト済み信号および第2シフト済み信号として出力する、レベルシフト回路を備え、レベルシフト回路は、第1入力信号に応じて開閉するスイッチング素子と抵抗を有する第1直列回路、および、第2入力信号に応じて開閉するスイッチング素子と抵抗を有する第2直列回路が、電源と接地端との間において互いに並列に設けられており、第1直列回路上の電圧を第1シフト済み信号として、第2直列回路上の電圧を第2シフト済み信号として、それぞれ出力するようになっており、接地端から第1直列回路および第2直列回路に向かって逆電流が流れることを防止する、逆流防止部を備えた信号伝達回路とする。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

過電流保護回路

【課題】出力トランジスタの駆動用電源から引き抜かれる無駄な駆動制限電流を低減する。

【解決手段】駆動制限回路11は、トランジスタ5に流れる検出電流Isを入力すると、それに応じた駆動制限電流をチャージポンプ回路6から制御ライン12を介して引き抜くことにより、電流Imを保護開始電流値Im1以下に制限する。電流引受回路25は、トランジスタ4の保護開始電流値Im1に対応してトランジスタ5に流れる検出電流値よりも小さく設定された引受電流Iaを流し込む。検出電流Isが引受電流Ia以下のときは、検出電流Isは全て電流引受回路25に流れ込むので、チャージポンプ回路6の出力電流は全てトランジスタ4のゲート駆動に使われる。

(もっと読む)

正負電圧論理出力回路及びこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とする。

【解決手段】負電圧レベルシフト回路4aは、第3のレベルシフタ13aと、第4のレベルシフタ14aとを具備すると共に、レベルシフト基準電圧回路3からの切替信号に応じて第4のレベルシフタ14aを短絡、開放するレベルシフト切替スイッチ8aとを具備してなり、負電圧VSSの大きさに応じて、レベルシフト切替スイッチ8aのオン、オフを選択することで、負電圧VSSの変動に対して正常な回路動作を確保できる範囲である動作ウィンドの拡張が可能に構成されたものとなっている。

(もっと読む)

液晶表示装置

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

直流過電流遮断装置

【課題】直流給電において、負荷に過電流が流れた場合、負荷電流路を瞬時に自動的に遮断する。さらに、負荷短絡が発生した場合でも、瞬時に自動的に負荷電流路を遮断する。

【解決手段】第1コイルの一端に外部の直流電源の一方の極の電位が印加され、第1半導体素子の他端に外部の直流電源の他方の極の電位が印加されているとき、第1コイルの他端と第2コイルの他端間に所定の電流値を超えた電流が流れると、第1半導体素子の一端の電位により、第2制御端を制御し、さらに第2半導体素子の一端の電位により、第1制御端を制御し、第1半導体素子が有する電流路を遮断する。

(もっと読む)

センサノードチップ、センサノードシステム、および受信装置

【課題】センサノードチップでの消費電力を効果的に削減して、センサチップノードの小型化を実現する。

【解決手段】外部振動に応じて容量値が互いに差動的に変化する2つの可変容量素子CP,CSからなるセンサ素子部11と、順方向で直列接続した3つ以上のダイオードD1〜D3とその後端部に接続した固定容量素子CSとからなるセンサ回路部12とを設け、センサ素子部11で得られた互いに差動的に変化する検知信号BP,BNで、各ダイオードD1〜D3を交互に導通制御して固定容量素子CSを徐々に充電することにより、外部振動に応じた電圧を示すセンサ出力信号SOを得る。

(もっと読む)

半導体集積回路装置

【課題】 超音波診断システム等に用いられる送信回路を、小面積で振動子駆動回路部高圧電源の高電位側及び低電位側とも0〜±200V程度まで可変とし、もって複数チャネルの送信回路を集積化した半導体集積回路装置を実現する。

【解決手段】 ゲート駆動回路部10において入力電圧パルスを電流パルスに変換し、振動子駆動回路部20に印加される高電位側電圧+HV及び低電位側電圧-HVを基準として、再び電流パルスを電圧パルスに変換することによって入力電圧パルスの電圧レベルシフトを実現すると共に、そのシフトされた電圧パルスを入力とするゲート駆動回路部10の出力バッファの電圧パルス振幅を、同じく振動子駆動回路部20に印加される高電位側電圧+HV及び低電位側電圧-HVを基準としてゲート駆動回路部10にて生成する構成とする。ゲート駆動回路部10と出力負荷駆動回路部20とは直流的に結合される。

(もっと読む)

半導体集積回路装置および高周波電力増幅モジュール

【課題】充分な昇圧電圧を確保しながら、挿入損失の低下を防ぐことによりアンテナスイッチの高調歪みを低減させる。

【解決手段】制御端子Tx1cLにオン電圧が印加されて、アンテナ端子と送信端子Tx1との間に設けられたアンテナスイッチ部がオンとなり、PCS/DCS方式の送信信号が送信端子Tx1からアンテナ端子を通過する。その際、送信信号の一部分が供給された昇圧回路30は、ダイオード32,33の整流作用により制御部から出力される制御電圧よりも高い昇圧電圧を出力端子DCgateに発生させ、アンテナスイッチ部のトランジスタ回路のゲートに印加する。この昇圧回路30では、抵抗36が出力端子DCgateに接続されているので入力された送信電力のRF信号経路における抵抗通過が1個だけとなり、送信信号の減衰を小さく抑えて挿入損失特性を良好にする。

(もっと読む)

パワー半導体装置

【課題】一度異常が検出されたなら、電源を遮断しても継続的に通電を制限できるパワー半導体装置を提供する。

【解決手段】制御信号が入力される外部制御端子8と、出力電流が流入または流出する2つの外部出力端子3,4と、出力電流を制御するパワー半導体素子2とを有する半導体装置1に、パワー半導体素子2の動作状態に応じた電気信号を出力する動作状態検出回路6と、動作状態検出回路6の出力が入力され、動作状態検出回路6の出力がパワー半導体素子2の異常を示す値になると所定の出力状態となり、電源が遮断されても所定の出力状態を保持し続ける不揮発性の状態保持回路7と、前記制御信号および状態保持回路の出力に応じて、パワー半導体素子2の出力を制限する制御回路5とを設ける。

(もっと読む)

半導体スイッチ回路

【課題】導通状態においても消費電流を低減することができる半導体スイッチ回路を提供すること。

【解決手段】半導体スイッチ回路100は、入出力端子101と入出力端子102間に、ソースを共有し、直列接続される導通用のP型MOSトランジスタQ101,Q102と、Q101のゲートにドレインが接続されたP型MOSトランジスタQ103及びN型MOSトランジスタQ105と、Q102のゲートにドレインが接続されたP型MOSトランジスタQ104及びN型MOSトランジスタQ106と、各トランジスタのゲートに接続された制御端子103とを備え、Q103,Q104のソース及びバックゲートはQ101,Q102のソースに接続される構成とし、制御端子103に印加する制御信号の電圧値Vcontによる電圧制御により、入出力端子101と入出力端子102間を導通/非導通に切り替える。

(もっと読む)

過電流検出回路

【課題】カレントミラー回路を構成するトランジスタにおいて発生するアーリー効果の影響を排除して、過電流検出精度を向上可能な過電流検出回路を提供する。

【解決手段】過電流検出回路21が、MOSトランジスタ2により負荷1を通電駆動すると、負荷電流の1/nの電流をMOSトランジスタ3側に流し、更にその電流をカレントミラー回路6によりミラーさせて抵抗10及び電圧検出回路11により検出を行なう場合、カレントミラー回路6とMOSトランジスタ3並びに電流検出抵抗10との間に、アーリー効果キャンセル回路29を配置する。

(もっと読む)

チャージポンプ回路

【課題】チャージポンプ回路のクロックドライバーのサイズを縮小してコストダウンを図る。

【解決手段】本発明のチャージポンプ回路は、プラス昇圧チャージポンプ回路100Aにおいて、初段のノードaに生成された正の昇圧電圧2VDDを用いて、第1、第3及び第4のクロックドライバー41,43,51の高レベル(VDD)を出力するMOSトランジスタをオンさせるためのゲート電圧として用いる。また、マイナス昇圧チャージポンプ回路200Aにおいて、初段のノードdに生成された負の昇圧電圧−VDDを用いて、第2及び第5のクロックドライバー42,52の高レベルを出力するMOSトランジスタをオンさせるためのゲート電圧として用いる。

(もっと読む)

電圧駆動素子の駆動方法

【課題】電動機の性能向上のため、所定の短時間のみ電動機側への電流すなわちインバータからの出力電流を大電流化するようなインバータ装置においても、短絡過電流に対してスイッチング素子を保護することができる電圧駆動素子の駆動方法を提供する。

【解決手段】少なくとも2つ以上の電圧駆動型スイッチング素子(Q1、Q2)を直列に接続したアームにおける電圧駆動素子の駆動方法において、インバータの出力電流要求値が所定の電流値以上となった場合に、通電に寄与しない電圧駆動型スイッチング素子のゲート電圧を、通電に寄与する電圧駆動型スイッチング素子のゲート電圧よりも低下させるとともに、通電に寄与しない電圧駆動型スイッチング素子の過電流検知レベルを、通電に寄与する電圧駆動型スイッチング素子の過電流検知レベルよりも低下させる(第1発明)。

(もっと読む)

半導体装置及び電圧発生回路

【課題】 スイッチング素子やスイッチング回路を構成する素子のオン抵抗を低減する。

【解決手段】 半導体装置1には、インバータINV1、インバータINV2、負電圧発生回路4、レベルシフタ11、及びPch MOSトランジスタP1が設けられている。インバータINV2は、高電位側電源Vddと負電圧発生回路4から出力される低電位側電源としての負電圧−Vnの間に設けられている。Pch MOSトランジスタP1は、ソースが入力端子2に接続され、ドレインが出力端子3に接続され、ゲートに制御信号SG3が入力され、入力端子2から、高電位側電源Vddが供給される。そして、制御信号SG3の信号レベルが“Low”レベル(−Vn)のときに、Pch MOSトランジスタP1はオンして、出力端子3側に設けられた負荷に電力を供給する。

(もっと読む)

1 - 19 / 19

[ Back to top ]