Fターム[5J056CC21]の内容

Fターム[5J056CC21]に分類される特許

1 - 20 / 574

レベルシフト回路

【課題】レベルシフト回路を高速動作する。

【解決手段】一つの実施形態によれば、レベルシフト回路は、第一のトランジスタ、第二のトランジスタ、第一のコンデンサ、及び第二のコンデンサが設けられる。第一のトランジスタは、制御端子に入力電圧が入力される。第二のトランジスタは、制御端子に入力電圧の反転信号が入力される。第一のコンデンサは、一端が第一のトランジスタの第一の端子に接続され、他端に入力電圧の反転信号が入力され、入力電圧の立ち上りのときに電荷を蓄積して第一のトランジスタの第一の端子側から一端側へ第一の電流を発生する。第二のコンデンサは、一端が第二のトランジスタの第一の端子に接続され、他端に入力電圧が入力され、入力電圧の立ち下りのときに電荷を蓄積して第二のトランジスタの第一の端子側から一端側へ第二の電流を発生する。

(もっと読む)

半導体装置

【課題】低電圧動作を実現可能なレベルシフト回路を提供する。

【解決手段】入力電位は、GNDとVDDとの間で切り替わる。電源端子には、VDDよりも高いVDDOが印加される。レベルシフト回路は、クランプ回路と接続制御回路を備える。クランプ回路は、ソースが第1ノードに接続され、ドレインがP側出力端子に接続され、ゲートが電源端子に接続された第1NMOSトランジスタと、ソースが第1ノードに接続され、ドレインがN側出力端子に接続され、ゲートがグランド端子に接続された第1PMOSトランジスタと、を備える。入力電位がGNDとVDDの一方の場合、接続制御回路は、P側出力端子にVDDOを印加し、且つ、N側出力端子とグランド端子との間の電気的接続を遮断する。入力電位がGNDとVDDの他方の場合、接続制御回路は、N側出力端子にGNDを印加し、且つ、P側出力端子と電源端子との間の電気的接続を遮断する。

(もっと読む)

バッファ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路の入力電圧の振幅を増大させることが可能なバッファ回路を提供する。

【解決手段】第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、且つ、各入力端同士及び各出力端同士がそれぞれ共通に接続されており、第1,第2トランジスタ回路の少なくとも一方のトランジスタ回路がダブルゲートトランジスタから成るバッファ回路において、第1,第2トランジスタ回路の一方のトランジスタ回路が動作状態のとき、他方のトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

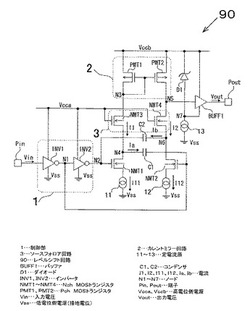

半導体装置

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、高電源電位が入力される入力端子とグランド端子との間に接続された抵抗と、抵抗中の第1ノードに接続された第2ノードと、第2ノードと第3ノードとの間に接続されたインバータと、抵抗を通した入力端子とグランド端子との間の電気的接続をON/OFF制御するスイッチと、を備える。ターゲット反転電位は、インバータの反転電位よりも高い。入力端子の電位がターゲット反転電位の場合、第2ノードの電位がその反転電位となる。第2ノードの電位が反転電位より低い場合、インバータは低電源電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をONする。一方、第2ノードの電位が反転電位より高い場合、インバータはグランド電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をOFFする。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

ソースフォロア回路

【課題】複数段構成におけるソースフォロア回路において入出力レンジを確保する。

【解決手段】ソースフォロア部SF11、SF12間に、ゲートドレイン間がダイオード接続され且つソースフォロア部SF11およびSF12を構成するMOSトランジスタM11およびM12と同一チャネル種類のMOSトランジスタM13とそのドレインに接続された電流源C13とからなる接続部11を設け、前段のソースフォロア部SF11の出力端とMOSトランジスタM13のソースとを接続し、MOSトランジスタM13のドレインと後段のソースフォロア部SF12の入力端とを接続する。接続部11における入出力間の電圧レベルのシフト方向は、ソースフォロア部SF11、SF12における入出力間の電圧レベルのシフト方向と逆となり、電圧シフトを打ち消す方向に作用するため、電圧レベルのシフトにより入出力レンジが狭くなることを抑制することが可能となる。

(もっと読む)

出力回路

【課題】高電圧信号を出力する回路を低耐圧トランジスタで構成しても、信頼性を向上させることのできる出力回路を提供する。

【解決手段】実施形態の出力回路は、出力部1が、高電圧電源端子VCCHと出力端子とZの間に接続されPMOSトランジスタP11、P12と、接地電位端子GNDと出力端子Zとの間に接続されたNMOSトランジスタN11、N12とを有し、低電圧入力信号INが入力されるプリバッファ部2が、PMOSトランジスタP11、NMOSトランジスタN11へ、VCCHよりも小さい振幅のゲート電圧PG、NGを出力する。PMOSトランジスタP12およびNMOSトランジスタN12のゲート端子へVCCHよりも低い定電圧VGが印加され、PMOSトランジスタP12の基板へVCCHよりも低い基板バイアス電圧VBPが印加され、NMOSトランジスタN12の基板へ接地電位よりも高い基板バイアス電圧VBNが印加される。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

半導体装置

【課題】小面積化、低コスト化を図ることが可能な半導体装置を提供すること。

【解決手段】制御回路50は、I/O方向レジスタ5から出力される値を信号50aとして出力し、信号50aに応じて、プルアップ許可レジスタ4から出力される値とI/Oレジスタ6から出力される値とのいずれかを選択して信号50bとして出力する。AND回路13は、電源制御部20から出力される信号21と制御回路50から出力される信号50aとの論理和を演算して出力する。AND回路14は、電源制御部20から出力される信号21と制御回路50から出力される信号50bとの論理和を演算して出力する。トライステートバッファ16は、AND回路13および14から出力される値に応じて、電極19に接続される外部のデバイスを駆動する。したがって、レベル変換(AND)回路の数を削減することができ、半導体装置の小面積化、低コスト化を図ることが可能となる。

(もっと読む)

半導体装置及び電子機器

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、シリアライザの負荷を抑制する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、n×2本の入力信号線から相補な内部データ信号DAT0/DAC0〜DAT3/DAC3を受信し、内部データ信号DT1/DC1をシリアルに出力する。プルアップバッファ回路100とプルダウンバッファ回路200は、内部データ信号DT1/DC1により制御される。

(もっと読む)

レベルコンバータ及びプロセッサ

【課題】本実施例の一側面におけるレベルコンバータは電源シーケンス制御用のトランジスタに起因する貫通電流の発生を防止することを目的とする。

【解決手段】本実施例の一側面におけるレベルコンバータは、第1電圧レベルより低い第2電圧レベルを第1論理レベルとし、基準電圧レベルを第2論理レベルとする入力信号を、第1電圧レベルを第1論理レベルとし、基準電圧レベルを第2論理レベルとする信号に変換するレベル変換回路と、第2電圧レベルを出力する第2電源がオフのとき基準電圧レベルを有し、第2電源がオンのとき第1電圧レベルを有する制御信号を出力する制御信号生成回路と、第1電圧レベルを出力する第1電源に接続された第1電源線とレベル変換回路の出力ノードの間に設けられ、制御信号に応じて、第2電源がオフのとき第1電源線と出力ノードを電気的に接続し、第2電源がオンのとき第1電源線と出力ノードを電気的に分離する接続回路を含む。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

レベルシフト回路

【課題】レベルシフト基準電位が下がった場合にスイッチング素子を安全且つ確実に停止できるレベルシフト回路。

【解決手段】レベルシフト電源に接続された抵抗R1にドレインが接続されソースがグランドに接続されたMOSFETMN3、R1と同じ抵抗値を有しレベルシフト電源に接続された抵抗R2にドレインが接続されソースがグランドに接続されたMOSFETMN4、入力信号に基づきMN3,MN4のオン/オフを制御するパルス生成回路10、MN3がオンである場合にセット信号を生成しMN4がオンである場合にリセット信号を生成する制御部MN1,MN2,R5,R6、制御部で生成されたセット信号とリセット信号とに基づき入力信号をレベルシフトした出力信号を出力しスイッチング素子Q1を動作させるフリップフロップFF1、レベルシフト基準電位が負電位に下がったことを検出してスイッチング素子を停止させるスイッチング動作停止部INV3,FF2,AD1を備える。

(もっと読む)

低いデューティサイクル歪みを有するレベルシフタ

【課題】低いデューティサイクル歪み及び高い電源電圧マージンの高速レベルシフティング回路を提供する。

【解決手段】レベルシフタ100は、反転回路104と、クロス接続されたレベルシフティングラッチ102と、SRロジックゲートラッチ103とを含み、レベルシフティングラッチ102の第1、第2出力は、SRロジックゲートラッチ103のセット(S)入力ノード121およびリセット(R)入力ノード120に接続され、反転回路104は、レベルシフティングラッチ102の第1入力ノード112に非反転の信号を供給すると共に、第2入力ノード113に反転の信号を供給し、入力信号のロウからハイへの変化はSRロジックゲートラッチ103をリセットし、ハイからロウへの変化はSRロジックゲートラッチ103をセットするように構成されている。

(もっと読む)

正負電圧論理出力回路およびこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とし、回路動作の確実性、安定性の向上を図った正負電圧論理出力回路を提供する。

【解決手段】論理入力と負電圧との間に、ゲートに論理入力するエンハンスメント型P型電界効果トランジスタEPFET1とブレークダウン保護用素子13,14とが直列に接続され、ブレークダウン保護用素子14に並列に短絡する切替スイッチ8aが接続される。切替スイッチ8aをオン、オフ制御することで、VSSの変動に対して正常な回路動作を確保できる動作ウィンドウの拡張を可能とする。

(もっと読む)

レベルシフト回路及びそれを用いたドライバと表示装置

【課題】低振幅の入力信号を高速に高振幅信号に変換するレベルシフト回路を提供する。

【解決手段】第1及び第2の出力端子の一方を第1電圧レベルに設定する第1のレベルシフト回路10と、第2の電圧端子と、前記第1及び第2の出力端子との間に接続され、前記第1及び第2の出力端子の他方を第2電圧レベルに設定する第2のレベルシフト回路20と、第1の制御信号に基づき、第1及び第2の入力信号が第1及び第2の入力端子に入力される時点で前記第2電圧レベルとされる一つの出力端子について、前記一つの出力端子と第2の給電端子間の電流経路を、前記第1及び第2の入力信号が前記第1及び第2の入力端子に入力される時点を含む所定期間、切断し、前記所定期間の後、前記一つの出力端子と前記第2の給電端子間の電流経路の切断を解除する制御を行う手段を備え、前記第1及び第2の出力端子の出力振幅は、前記第1及び第2の入力信号の振幅よりも大きい。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

1 - 20 / 574

[ Back to top ]