Fターム[5H740HH07]の内容

電力変換一般 (12,896) | 主回路スイッチング素子制御回路用電源 (495) | 別電源からとるもの (364) | オン用とオフ用の電源を1電源としたもの (118)

Fターム[5H740HH07]に分類される特許

1 - 20 / 118

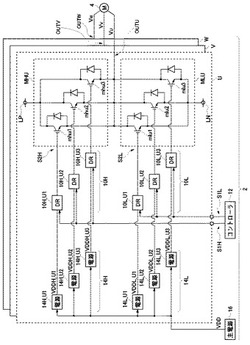

電力変換装置

【課題】電源電圧を安定化して、高周波駆動に対応可能な電力変換装置を提供する。

【解決手段】複数のハイサイドトランジスタユニットmhは、各相ごとに設けられ、対応する相の出力端子OUTと上側電源ラインLPの間に、電気的に並列に、かつ制御端子が独立して設けられる。複数のハイサイドゲートドライブ回路10H_U1〜U3は、対応する複数のハイサイドトランジスタユニットmhu1〜3にゲートドライブ信号を出力する。複数のハイサイド電源回路14H_U1〜U3は、対応するハイサイドゲートドライブ回路10H_U1〜U3に電源電圧VDDH_U1〜U3を供給する。下側アームについても同様に、複数のローサイドトランジスタユニットに分割される。

(もっと読む)

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

昇降圧コンバータ

【課題】ハイサイドにn型MOSFETを使用する昇降圧コンバータにおいて、より容易に昇圧モードを実現する。

【解決手段】昇降圧コンバータ100は、降圧モードにおいて、ハイサイドn型MOSFET134のオンオフにより、バッテリ電圧Vbatよりも低い駆動電圧Vdを生成する降圧部102と、昇圧モードにおいて、ローサイドn型MOSFET128のオンオフにより、バッテリ電圧Vbatよりも高い駆動電圧Vdを生成する昇圧部104と、昇圧モードにおいて、ローサイドn型MOSFET128のオンオフを利用してブートストラップキャパシタ114を充電する充電部142と、昇圧モードにおいて、充電されたブートストラップキャパシタ114の他端114bの電圧Vbをハイサイドn型MOSFET134のゲートに印加するハイサイドスイッチ駆動部138と、を備える。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

電源スイッチ保護回路及び車載機器

【課題】過電流から電源スイッチ回路を適切に保護する技術を提供する。

【解決手段】電源スイッチ保護回路は、電源スイッチ回路と、第1回路素子及び第2回路素子の両方がオン状態を示す場合に電源スイッチ回路をオン状態とし、第1回路素子及び第2回路素子の少なくとも一方がオフ状態を示す場合に電源スイッチ回路をオフ状態とする電源スイッチ制御回路と、電源スイッチ回路の出力側の短絡を検出し、短絡が検出されているか否かを示しかつ第1回路素子のオフ状態及びオン状態を切り換えるための短絡検出信号を出力する短絡検出回路と、所定時間内における短絡検出信号の状態変化に応じて、短絡が発生しているか否かを判定し、短絡が発生していると判定すると、第2回路素子がオフ状態を維持するように電源スイッチ制御回路を制御する制御部と、を備える。

(もっと読む)

電力変換装置

【課題】スイッチング素子を複数並列に接続して逆変換器等を構成した場合にも簡易かつ確実に電流アンバランスを解消することができる電力変換装置を提供する。

【解決手段】ゲート調整回路12は、基準素子ユニット501における直流電流検出器541の直流電流の検出値Id1および、基準素子ユニット501以外の素子ユニット502における直流電流検出器542の直流電流の検出値Id2に基づいて、それぞれ時間γ1および時間γ2から時間差Δtを電流アンバランス量として算出する。ゲート調整回路12は、時間差Δtを次の第1状態におけるターンオフのタイミングで、ゲート駆動回路552uの動作信号S2uに遅延時間として付加する。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

電力変換装置用の駆動回路および電力変換装置

【課題】上側のスイッチング素子の誤動作を抑制できる電力変換装置用の駆動回路を提供する。

【解決手段】第1回路10は、直流電源E1の低電位端と高電位端との間で相互に直列に接続される第1素子11及び第2素子12を有し、第1素子11は高電位端側に設けられ、第2素子12は低電位端側に設けられる。第1素子11及び第2素子12は、その両方がスイッチである。第2回路20は、第2素子12の両端の電圧が所定値よりも大きいときにスイッチング素子Tx1を非導通とし、当該電圧が所定値よりも小さいときにスイッチング素子Tx1を導通させる。スイッチ素子32は、第1素子11と並列に接続され、スイッチング素子Tx1が非導通である状態で導通し、スイッチング素子Tx1が導通する状態で非導通する。

(もっと読む)

電力変換装置及び電力変換システム

【課題】更なる信頼性向上を図れる電力変換装置及び電力変換システムを提供すること。

【解決手段】上記課題を解決するために、例えば、インバータ回路は、前記モータ制御回路からのPWM信号に基づき前記インバータ回路を構成する半導体スイッチング素子を駆動するゲートドライブ回路とサージ電圧検出信号を検出するサージ電圧検出回路を備え、サージ電圧検出回路により検出されたサージ電圧検出信号はモータ制御回路に入力され、サージ電圧検出信号を検出した際に前記電流指令生成部からの電流指令値と所定の電流指令値と対比することによりサージ電圧を抑制するサージ電圧抑制手段の実施の可否を選択するような手段を設けるようにすればよい。

(もっと読む)

電力変換装置

【課題】両極性ブートストラップ回路のキャパシタ充電を短絡電流が流れることがなく安全かつ確実に実施できる電力変換装置を提供する。

【解決手段】各レグ2〜4を構成する上下の各アームのスイッチング素子SuH、SuL、・・・に対しオン/オフ駆動用の正負両極の電圧を印加するアーム駆動回路DRuH、DRuL、・・・を個別に設け、直流電源Vg1〜Vg3からの電力により正負の各電圧を充電する各キャパシタC1u、C2u、・・・を上下の各アームに設け、かつ各レグ2〜4に両極性ブートストラップ回路5〜7を配置し、キャパシタ充電制御を行う制御回路8は、多相交流電源1の各相の電圧の中で最も高い電圧が入力されているレグの上段アーム側のスイッチング素子と、最も低い電圧が入力されているレグの下段アーム側のスイッチング素子のみをオンする制御信号を各相の電圧変化に応じて繰り返し出力する。

(もっと読む)

スイッチング素子の駆動装置及びスイッチング素子の駆動方法

【課題】スイッチング損失の増大を抑制しつつ、より高い周波数帯で発生するスイッチングノイズを抑制できるスイッチング素子の駆動装置を提供する。

【解決手段】スルーレート調整部は、NチャネルMOSFETを介してDCモータに出力される電圧波形のスルーレートを変化させ、キャリア周波数によって決まる周波数帯よりも高い周波数帯域に現れるスイッチングノイズの周波数成分を分散させてピークレベルを低下させる。

(もっと読む)

インバータ装置およびそれを用いた誘導加熱装置

【課題】スイッチング素子の耐数年数をのばすと共に、駆動電圧を低下させることによるスイッチング素子の損失増加も改善させるインバータ装置およびそれを用いた誘導加熱装置を提供することを目的とする。

【解決手段】交流電圧を直流電圧に変換するコンバータ回路30と、スイッチング素子24で構成され直流電圧を任意の電圧と周波数の電力に変換し、負荷に高周波電流を供給するインバータ回路31と、インバータ回路31のスイッチング素子24にスイッチング信号を供給する駆動回路25と、インバータ回路31の出力電力を検知する電力検知手段26とを備え、電力検知手段26で検知した電力に応じて、インバータ回路31のスイッチング素子24に供給するスイッチング信号の駆動電圧を可変させる駆動電圧可変手段27とを備えた構成とすることで、インバータの出力電力に応じて、スイッチング素子24の駆動電圧を可変させることが可能となる。

(もっと読む)

駆動装置

【課題】電圧駆動型素子を駆動状態と非駆動状態の間で遷移させるときの遷移期間において、電圧駆動型素子のゲート電圧を柔軟に制御するための技術を提供する。

【解決手段】駆動装置1は、電圧駆動部3と電流駆動部4を備えている。電圧駆動型素子2を駆動状態と非駆動状態の間で遷移させるときの遷移期間のうちの一部の区間では、電圧駆動部3を利用した電圧駆動型素子2のゲート電圧Vgの制御が停止され、電流駆動部4を利用した電圧駆動型素子2のゲート電圧Vgの制御が実行されるように構成されている。

(もっと読む)

スイッチング電源回路および電動機の制御装置

【課題】スイッチング電源で、電流検出回路を設けずに、負荷変動に伴う電圧上昇の抑制を可能とする。

【解決手段】スイッチング電源回路14は、一次巻線と二次巻線とを有するトランス41と、スイッチング信号を一次巻線に入力してトランス41を駆動する一次側回路40と、二次巻線に接続され、一次側回路40とは電気的に絶縁されているゲートドライブ回路20−nとを具備している。ゲートドライブ回路20−nは、モータECU100からのPWM信号によって駆動されるゲート駆動回路21−nと、ゲートドライブ回路20−nに流れる電流を増大させるブリーダ抵抗R20−nとを有し、モータECU100からのPWM信号を検出した場合に、ブリーダ抵抗R20−nに流れる電流値を減少させる。

(もっと読む)

電圧制御型スイッチング素子のゲート駆動回路

【課題】電圧制御型スイッチング素子のスイッチング時に、サージ電圧・サージ電流及びスイッチングノイズを抑制しながら、誤動作の発生を抑制することができる電圧制御型スイッチング素子のゲート駆動回路を提供する。

【解決手段】電圧制御型スイッチング素子2のゲートにゲート電圧を供給して当該電圧制御型スイッチング素子2を駆動するゲート駆動回路であって、直列に接続された高電位側スイッチング素子M1及び低電位側スイッチング素子M2と、前記高電位側スイッチング素子M1と高電位電源との間及び前記低電位側スイッチング素子M2と低電位電源との間の少なくとも一方に介挿された第1の可変抵抗VR11,VR12と、前記第1の可変抵抗VR11,VR12の抵抗値を調整する制御回路4とを備えている。

(もっと読む)

半導体装置

【課題】インバータ回路とそれを構成するスイッチ素子を駆動・制御する駆動・制御回路において、追加回路規模が少なく、所望の負電位を動的に印加できる駆動・制御回路、また、インバータ回路における短絡電流を削減し、損失の少ない電力変換回路を提供する。

【解決手段】半導体装置において、第1,第2スイッチ素子(下側アームのスイッチ素子LSW,同様の上側アームのスイッチ素子)を有するインバータ回路と駆動回路(L側ゲート駆動回路LGD,同様のH側ゲート駆動回路)と制御回路とを有し、駆動回路は、スイッチ素子のゲート電極をソース電位に駆動する回路と、スイッチ素子のゲート電極を負電位に駆動する回路とを有し、負電位に駆動する回路の出力ノードとスイッチ素子との間に直列にコンデンサが接続され、制御回路は、スイッチ素子がオフ状態からオン状態になる直前のスイッチ素子のゲート電極の電圧をソース電位と同じであるように制御する。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

(もっと読む)

ゲート駆動回路

【課題】絶縁ゲート型半導体スイッチ素子のターンオフ時の遅延時間短縮、遮断電流のdi/dtによるサージ電圧を抑制することができるゲート駆動回路を提供する。

【解決手段】半導体スイッチ素子のゲート端子とゲート補助端子間にオン用ゲート電源とオン用スイッチとオン用ゲート抵抗の直列体よりなるオン回路を接続し、半導体スイッチ素子のゲートとゲート補助端子間に第1のオフ用ゲート抵抗とオフ用スイッチとターンオフ用電源を直列に接続し第1のオフゲート抵抗と並列にコンデンサと第2のオフ用ゲート抵抗の直列体を接続したオフ回路を備えてなる。第1のオフ用ゲート抵抗より第2のオフ用ゲート抵抗の抵抗値が小さく、コンデンサと第2オフ用ゲート抵抗で構成するCR回路の時定数が絶縁ゲート型半導体スイッチ素子のターンオフ遅れ時間と同等である。

(もっと読む)

レベルシフト回路、制御回路及びDC−DCコンバータ

【課題】信号遅延が小さく高速化可能なレベルシフト回路、制御回路及びDC−DCコンバータを提供する。

【解決手段】実施形態によれば、差動電流生成回路と電流減算回路とを備えたレベルシフト回路が提供される。前記差動電流生成回路は、第1の高電位端子と第1の低電位端子との間に接続され、入力される制御信号に応じて、規定値または前記規定値よりも大きい電流値に変化する電流と前記規定値よりも大きい電流値または前記規定値に変化する電流とを一対の差動電流として生成する。前記電流減算回路は、第2の高電位端子と第2の低電位端子との間に接続され、前記一対の差動電流を受けて、前記一対の差動電流の差に等しい電流を生成する。

(もっと読む)

レベルシフト回路、制御回路及びDC−DCコンバータ

【課題】低消費電力で高速動作可能なレベルシフト回路、制御回路及びDC−DCコンバータを提供する。

【解決手段】実施形態によれば、電流生成回路と、電流スイッチ回路と、保護回路と、を備えたレベルシフト回路が提供される。前記電流生成回路は、第1の高電位端子と第1の低電位端子との間に接続され、第1の電流を生成して第1の出力線に出力する。前記電流スイッチ回路は、第2の高電位端子と第2の低電位端子との間に接続され、前記電流生成回路よりも大きい電流供給能力で前記第1の電流を受け、入力信号に応じて前記第1の電流を流しまたは前記第1の電流を遮断する。前記保護回路は、前記電流生成回路と前記電流スイッチ回路との間において前記第1の出力線に接続され、前記第1の出力線の電位を前記第1の低電位端子の電位以上で前記第1の高電位端子の電位以下に制限して前記電流生成回路を過電圧から保護する。

(もっと読む)

1 - 20 / 118

[ Back to top ]