ゲート駆動回路

【課題】絶縁ゲート型半導体スイッチ素子のターンオフ時の遅延時間短縮、遮断電流のdi/dtによるサージ電圧を抑制することができるゲート駆動回路を提供する。

【解決手段】半導体スイッチ素子のゲート端子とゲート補助端子間にオン用ゲート電源とオン用スイッチとオン用ゲート抵抗の直列体よりなるオン回路を接続し、半導体スイッチ素子のゲートとゲート補助端子間に第1のオフ用ゲート抵抗とオフ用スイッチとターンオフ用電源を直列に接続し第1のオフゲート抵抗と並列にコンデンサと第2のオフ用ゲート抵抗の直列体を接続したオフ回路を備えてなる。第1のオフ用ゲート抵抗より第2のオフ用ゲート抵抗の抵抗値が小さく、コンデンサと第2オフ用ゲート抵抗で構成するCR回路の時定数が絶縁ゲート型半導体スイッチ素子のターンオフ遅れ時間と同等である。

【解決手段】半導体スイッチ素子のゲート端子とゲート補助端子間にオン用ゲート電源とオン用スイッチとオン用ゲート抵抗の直列体よりなるオン回路を接続し、半導体スイッチ素子のゲートとゲート補助端子間に第1のオフ用ゲート抵抗とオフ用スイッチとターンオフ用電源を直列に接続し第1のオフゲート抵抗と並列にコンデンサと第2のオフ用ゲート抵抗の直列体を接続したオフ回路を備えてなる。第1のオフ用ゲート抵抗より第2のオフ用ゲート抵抗の抵抗値が小さく、コンデンサと第2オフ用ゲート抵抗で構成するCR回路の時定数が絶縁ゲート型半導体スイッチ素子のターンオフ遅れ時間と同等である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、MOSFET、IGBT等の絶縁ゲート構造を持つ半導体スイッチ素子のゲート駆動回路に関するものである。

【背景技術】

【0002】

MOSFETやIGBTなどの絶縁ゲート構造を持つ半導体スイッチ素子は、駆動速度が速く、また電圧駆動型素子であるためバイポーラトランジスタなどの電流駆動型素子に比べて駆動電力が小さく、マイクロエレクトロニクスからパワーエレクトロニクスの分野まで幅広く利用されている。

【0003】

これらの絶縁ゲート型半導体スイッチ素子は、ゲート端子が他の端子に対して絶縁膜で絶縁されており、ゲート端子から他の端子の間に等価的にコンデンサが形成されている。絶縁ゲート型半導体素子の一例としてIGBTをあげると、内部配線等に起因する寄生抵抗または意図的に挿入されたゲート抵抗Rgと、ゲート−エミッタ間容量CGE、ゲート−コレクタ間容量CGCがそれぞれ直列に接続されたCR回路が形成されており、ゲート駆動回路はこれらのゲート容量を充放電させるための回路となる。

【0004】

図3は、従来技術のゲート駆動回路を示す回路図である。図3では、絶縁ゲート型半導体スイッチ素子としてIGBTを例にとり、一般的なゲート駆動回路を示したものである。図4は従来技術のゲート駆動回路の動作を説明するタイミングチャートである。以下に図3の回路の動作を図4のタイミングチャートを交えて説明をする。駆動対象IGBT5をターンオンさせる場合、オン用スイッチ3を閉にする。このとき、オフ用スイッチ4はオン用スイッチ3と相補的に動作するように制御するので開とする。このスイッチ状態により、オン用電源1の正極からオン用スイッチ3、第1のゲート抵抗9と第2のゲート抵抗10の並列体(ダイオード11は正バイアスとなるので導通状態となる)、ゲート端子6、駆動対象IGBT5のゲート−エミッタ間容量を介しオン用電源1の負極に至る閉回路が形成される。この状態で時間が経過すると、駆動対象IGBT5のゲート容量が充電されてゲート−エミッタ間電圧VGEは上昇していく。VGEが駆動対象IGBT5のスレッショルド電圧に達すると、コレクタ電流ICが流れ始めコレクタ−エミッタ間電圧VCEは下降していく。オン用スイッチ3が閉になってからコレクタ電流ICが流れ始めるまでの時間をターンオン遅延時間td(ON)という。その後駆動対象IGBT5のゲートミラー容量を充電しコレクタ電流ICが飽和するまでの時間をコレクタ電流上昇時間trという。ゲート−エミッタ間電圧VGEはさらに充電され、最終的にオン用電源1の電圧まで達する。

【0005】

一方、駆動対象IGBT5をターンオフさせる場合、ターンオンとは逆にオン用スイッチ3を開、オフ用スイッチ4を閉とする。このスイッチ状態により、オフ用電源2の正極から駆動対象IGBT5のゲート−エミッタ間容量、ゲート端子6、第1のゲート抵抗9(ダイオード11は逆バイアスになるので第2のゲート抵抗10は電流路から外れる)、オフ用スイッチ4を介してオフ用電源2の負極に至る閉回路が形成される。この状態で時間が経過すると、駆動対象IGBT5のゲート容量が放電されてゲート−エミッタ間電圧VGEは下降していく。VGEが駆動対象IGBT5のスレッショルド電圧に達するとコレクタ電流ICは減少し始めコレクタ−エミッタ間電圧VCEは上昇していく。オフ用スイッチ4が閉になってからコレクタ電流ICが減少し始めるまでの時間をターンオフ遅延時間td(OFF)という。その後駆動対象IGBT5のゲートミラー容量を放電しコレクタ電流ICが消滅するまでの時間をコレクタ電流下降時間tfという。ゲート−エミッタ間電圧VGEはさらに放電され、最終的にオフ用電源2の電圧まで放電される。

【0006】

図3の回路で、ダイオード11によりターンオン時とターンオフ時のゲート抵抗値を切換える理由は、ターンオフ時のコレクタ−エミッタ間電圧VCEに過大なサージ電圧が発生することを抑制するためである。一般的にIGBTなどのスイッチ素子や、それらを組込んだパワー変換回路では、コレクタ電流ICが流れる経路上に寄生インダクタンスを抱えており、コレクタ電流の減少率(di/dt)が大きいと、寄生インダクタンスによる逆起電力(L・di/dt)によりIGBTのコレクタ−エミッタ間電圧VCEにサージ電圧が重畳される。これがIGBTのコレクタ−エミッタ間電圧絶対最大定格を越えると、IGBTの破壊に至る。ターンオフ時のコレクタ電流の減少率は、コレクタ電流が減少しているときの、ゲート容量を放電する速さに比例する。また、ゲート容量を放電する速さは、放電電流を制限するゲート抵抗の大きさで決まる。よって、ターンオン時にゲート抵抗を並列化してゲート抵抗値を減少させ、ターンオフ時はダイオードの逆バイアスによりゲート抵抗の並列化を阻止しゲート抵抗値を増大させ、コレクタ電流の減少率を抑制することで、サージ電圧の低減を図るものである。

【0007】

図3の回路によりターンオフ時のサージ電圧を抑えるゲート駆動回路を実現できるが、別の弊害もある。ターンオフ時のゲート抵抗値を常時大きくしているため、ゲート容量を放電する時間が一律に長くなり、ターンオフ遅延時間td(OFF)も増大することになる。これによりパワー変換回路の制御応答が悪化したり、これらの素子をアーム構成で使用する場合はデッドタイムが減少するなど、各種の弊害が発生する。この弊害を回避するには、ターンオフ動作時に、ターンオフ遅延時間の期間ではゲート抵抗を小さく、コレクタ電流下降時間の期間でゲート抵抗を大きくする等、動的にゲート抵抗を変化させることや、能動素子を使用し、ゲート電流をコントロールする方法がある。

【0008】

この問題に対し、特許文献1ではゲート抵抗と絶縁ゲート型スイッチ素子のゲート端子の接続点にゲート電位制御回路を接続し、ターンオン時にはゲート電位制御回路より適量の電荷を放電することでターンオンの速さを抑制し、ターンオフ時にはゲート電位制御回路より適量の電荷を充電することでターンオフの速さを抑制することで、サージ電圧を抑制するものである。しかしながら、ゲート電位制御回路にはゲート電位を検知する回路、ゲート電位を充放電する回路が必要であり、ゲート駆動回路が複雑化し大規模になってしまう難点があった。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2003−70233号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

絶縁ゲート型半導体スイッチ素子のゲート駆動回路において、ターンオフ時の遅延時間の短縮とサージ電圧に関与するdi/dtの抑制との相反する問題を、複雑な回路なしで単純な回路のみで解決するものである。

【課題を解決するための手段】

【0011】

請求項1の発明によれば、絶縁ゲート型半導体スイッチ素子と、該絶縁ゲート型半導体スイッチ素子のゲート端子とゲート補助端子間にオン用ゲート電源とオン用スイッチとオン用ゲート抵抗の直列体よりなるオン回路を接続し、前記絶縁ゲート型半導体スイッチ素子のゲート端子とゲート補助端子間に第1のオフ用ゲート抵抗とオフ用スイッチとオフ用電源の直列体よりなるオフ回路を接続し、該第1のオフ用ゲート抵抗にコンデンサと第2のオフ用ゲート抵抗の直列体を並列接続してなることを特徴とする。

【0012】

請求項2の発明によれば、請求項1に記載のゲート駆動回路において、前記第1のオフ用ゲート抵抗より前記第2のオフ用ゲート抵抗の抵抗値が小さく、前記コンデンサと前記第2オフ用ゲート抵抗で構成するCR回路の時定数が前記絶縁ゲート型半導体スイッチ素子のターンオフ遅れ時間と同等であることを特徴とする。

【発明の効果】

【0013】

本発明のゲート駆動回路によれば、絶縁ゲート型半導体スイッチ素子のターンオフ時において、遅延時間に関する期間はゲート抵抗を小さくして遅延時間を短縮し、di/dtに関与する期間はゲート抵抗を大きくしてdi/dtを抑制する動作を単純な回路で構成できる。

【図面の簡単な説明】

【0014】

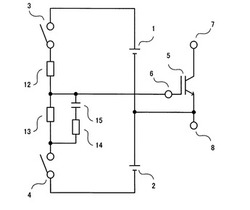

【図1】本発明のゲート駆動回路を示す回路図である。

【図2】本発明のゲート駆動回路の動作を説明するタイミングチャートである。

【図3】従来技術のゲート駆動回路を示す回路図である。

【図4】従来技術のゲート駆動回路の動作を説明するタイミングチャートである。

【発明を実施するための形態】

【0015】

ターンオフ時の遅延時間の短縮と、di/dtの抑制という目的を、回路の複雑化を伴わずに実現した。以下、本発明の実施の形態について説明する。

【実施例1】

【0016】

図1は、本発明のゲート駆動回路を示す回路図である。図2は本発明のゲート駆動回路の動作を説明するタイミングチャートである。図1では駆動対象の絶縁ゲート型半導体スイッチ素子としてIGBTを例にした。以下に図1の回路の動作について図2を交えて説明する。

【0017】

駆動対象IGBT5をターンオンさせる場合、オン用スイッチ3を閉に、オフ用スイッチ4を開にする。このとき、オン用電源1の正極からオン用スイッチ3、オン用ゲート抵抗12、ゲート端子6、駆動対象IGBT5のゲート−エミッタ間容量を介し、オン用電源1の負極に至る閉回路が形成される。この状態で時間が経過すると、ゲート−エミッタ間電圧VGEがスレッショルド電圧に達し駆動対象IGBT5はターンオンを始める。ターンオンに関しては従来技術と同様なので以降の説明は省略する。

【0018】

一方、駆動対象IGBT5をターンオフさせる場合、オン用スイッチ3を開に、オフ用スイッチ4を閉にする。このとき、オフ用電源2の正極から駆動対象IGBT5のゲート−エミッタ間容量、ゲート端子6、第1のオフ用ゲート抵抗13、オフ用スイッチ4を介し、オフ用電源2の負極に至る閉回路1と、オフ用電源2の正極から駆動対象IGBT5のゲート−エミッタ間容量、ゲート端子6、コンデンサ15、第2のオフ用ゲート抵抗14、オフ用スイッチ4を介し、オフ用電源2の負極に至る閉回路2の2つの放電経路が形成される。ここで、第1のオフ用ゲート抵抗13を経由する放電電流をIG(OFF1)、コンデンサ15と第2のオフ用ゲート抵抗14を経由する放電電流をIG(OFF2)とする。

【0019】

IG(OFF1)の初期ピーク値は、オン用電源1の電圧V(ON)とオフ用電源2の電圧V(OFF)の和を、第1のオフ用抵抗13の抵抗値RG(OFF1)で除した値となり、減衰は駆動対象IGBT5のゲート容量と第1のオフ用ゲート抵抗13の時定数で決定される。同様にIG(OFF2)の初期ピーク値は、V(ON)+V(OFF)を第2のオフ用抵抗14の抵抗値RG(OFF2)で除した値となり、減衰は駆動対象IGBT5のゲート容量とコンデンサ15の合成容量と第2のオフ用ゲート抵抗14の時定数で決定される。ここで、第1のオフ用ゲート抵抗13と第2のオフ用ゲート抵抗14の抵抗値の大小関係をRG(OFF1)>RG(OFF2)とすると、IG(OFF1)とIG(OFF2)の初期ピーク値の大小関係は図4のとおりとなる。また、コンデンサ15と第2のオフ用ゲート抵抗14の時定数を十分小さくすると、IG(OFF1)とIG(OFF2)の減衰時間の関係も図4のとおりとなる。

【0020】

ターンオフ時のゲート容量放電回路のうち、閉回路2の第2のオフ用ゲート抵抗14の抵抗値を許容できる最小限の値として、なおかつコンデンサ15と第2のオフ用ゲート抵抗14の時定数を所望の遅延時間td(OFF)相当に選定すると、ターンオフ動作開始時からコレクタ電流ICの遮断を始める間に、閉回路1と比較して大量のゲート容量を放電し、ターンオフ遅延時間を大幅に短縮する。ターンオフ動作開始から時間が経過し、コレクタ電流ICの遮断が始まる頃になると、閉回路2のコンデンサ15は十分充電されIG(OFF2)は十分減衰する。この時点で駆動対象IGBT5のゲート容量放電回路は閉回路1のみになり、コレクタ電流ICの遮断開始以降はゲート容量の放電は緩やかになる。ここで、所望のコレクタ電流下降時間tfになるよう閉回路1の第1のオフ用ゲート抵抗13の抵抗値を選定すると、di/dtが抑制されコレクタ−エミッタ間電圧VCEのサージ電圧も十分抑制できる。

【0021】

上記の動作を言い換えると、コンデンサ15と第2のオフ用ゲート抵抗14の直列体は、駆動対象IGBT5のターンオフ遅延時間td(OFF)相当の時間のみ、第1のオフ用ゲート抵抗13をバイパスする回路とみなすことができる。

【産業上の利用可能性】

【0022】

複雑な制御回路や検出回路を用いることなく受動素子の定数選定のみで、ターンオフ時の遅延時間短縮、サージ電圧の低減を実現でき、半導体スイッチ素子を組込んだ装置の制御性の改善、ノイズの低減、スナバ回路の削減による装置の小型化などを目的とした用途に適用できる。

【符号の説明】

【0023】

1 オン用電源

2 オフ用電源

3 オン用スイッチ

4 オフ用スイッチ

5 駆動対象IGBT

6 ゲート端子

7 コレクタ端子

8 エミッタ端子

9 第1のゲート抵抗

10 第2のゲート抵抗

11 ダイオード

12 オン用ゲート抵抗

13 第1のオフ用ゲート抵抗

14 第2のオフ用ゲート抵抗

15 コンデンサ

【技術分野】

【0001】

本発明は、MOSFET、IGBT等の絶縁ゲート構造を持つ半導体スイッチ素子のゲート駆動回路に関するものである。

【背景技術】

【0002】

MOSFETやIGBTなどの絶縁ゲート構造を持つ半導体スイッチ素子は、駆動速度が速く、また電圧駆動型素子であるためバイポーラトランジスタなどの電流駆動型素子に比べて駆動電力が小さく、マイクロエレクトロニクスからパワーエレクトロニクスの分野まで幅広く利用されている。

【0003】

これらの絶縁ゲート型半導体スイッチ素子は、ゲート端子が他の端子に対して絶縁膜で絶縁されており、ゲート端子から他の端子の間に等価的にコンデンサが形成されている。絶縁ゲート型半導体素子の一例としてIGBTをあげると、内部配線等に起因する寄生抵抗または意図的に挿入されたゲート抵抗Rgと、ゲート−エミッタ間容量CGE、ゲート−コレクタ間容量CGCがそれぞれ直列に接続されたCR回路が形成されており、ゲート駆動回路はこれらのゲート容量を充放電させるための回路となる。

【0004】

図3は、従来技術のゲート駆動回路を示す回路図である。図3では、絶縁ゲート型半導体スイッチ素子としてIGBTを例にとり、一般的なゲート駆動回路を示したものである。図4は従来技術のゲート駆動回路の動作を説明するタイミングチャートである。以下に図3の回路の動作を図4のタイミングチャートを交えて説明をする。駆動対象IGBT5をターンオンさせる場合、オン用スイッチ3を閉にする。このとき、オフ用スイッチ4はオン用スイッチ3と相補的に動作するように制御するので開とする。このスイッチ状態により、オン用電源1の正極からオン用スイッチ3、第1のゲート抵抗9と第2のゲート抵抗10の並列体(ダイオード11は正バイアスとなるので導通状態となる)、ゲート端子6、駆動対象IGBT5のゲート−エミッタ間容量を介しオン用電源1の負極に至る閉回路が形成される。この状態で時間が経過すると、駆動対象IGBT5のゲート容量が充電されてゲート−エミッタ間電圧VGEは上昇していく。VGEが駆動対象IGBT5のスレッショルド電圧に達すると、コレクタ電流ICが流れ始めコレクタ−エミッタ間電圧VCEは下降していく。オン用スイッチ3が閉になってからコレクタ電流ICが流れ始めるまでの時間をターンオン遅延時間td(ON)という。その後駆動対象IGBT5のゲートミラー容量を充電しコレクタ電流ICが飽和するまでの時間をコレクタ電流上昇時間trという。ゲート−エミッタ間電圧VGEはさらに充電され、最終的にオン用電源1の電圧まで達する。

【0005】

一方、駆動対象IGBT5をターンオフさせる場合、ターンオンとは逆にオン用スイッチ3を開、オフ用スイッチ4を閉とする。このスイッチ状態により、オフ用電源2の正極から駆動対象IGBT5のゲート−エミッタ間容量、ゲート端子6、第1のゲート抵抗9(ダイオード11は逆バイアスになるので第2のゲート抵抗10は電流路から外れる)、オフ用スイッチ4を介してオフ用電源2の負極に至る閉回路が形成される。この状態で時間が経過すると、駆動対象IGBT5のゲート容量が放電されてゲート−エミッタ間電圧VGEは下降していく。VGEが駆動対象IGBT5のスレッショルド電圧に達するとコレクタ電流ICは減少し始めコレクタ−エミッタ間電圧VCEは上昇していく。オフ用スイッチ4が閉になってからコレクタ電流ICが減少し始めるまでの時間をターンオフ遅延時間td(OFF)という。その後駆動対象IGBT5のゲートミラー容量を放電しコレクタ電流ICが消滅するまでの時間をコレクタ電流下降時間tfという。ゲート−エミッタ間電圧VGEはさらに放電され、最終的にオフ用電源2の電圧まで放電される。

【0006】

図3の回路で、ダイオード11によりターンオン時とターンオフ時のゲート抵抗値を切換える理由は、ターンオフ時のコレクタ−エミッタ間電圧VCEに過大なサージ電圧が発生することを抑制するためである。一般的にIGBTなどのスイッチ素子や、それらを組込んだパワー変換回路では、コレクタ電流ICが流れる経路上に寄生インダクタンスを抱えており、コレクタ電流の減少率(di/dt)が大きいと、寄生インダクタンスによる逆起電力(L・di/dt)によりIGBTのコレクタ−エミッタ間電圧VCEにサージ電圧が重畳される。これがIGBTのコレクタ−エミッタ間電圧絶対最大定格を越えると、IGBTの破壊に至る。ターンオフ時のコレクタ電流の減少率は、コレクタ電流が減少しているときの、ゲート容量を放電する速さに比例する。また、ゲート容量を放電する速さは、放電電流を制限するゲート抵抗の大きさで決まる。よって、ターンオン時にゲート抵抗を並列化してゲート抵抗値を減少させ、ターンオフ時はダイオードの逆バイアスによりゲート抵抗の並列化を阻止しゲート抵抗値を増大させ、コレクタ電流の減少率を抑制することで、サージ電圧の低減を図るものである。

【0007】

図3の回路によりターンオフ時のサージ電圧を抑えるゲート駆動回路を実現できるが、別の弊害もある。ターンオフ時のゲート抵抗値を常時大きくしているため、ゲート容量を放電する時間が一律に長くなり、ターンオフ遅延時間td(OFF)も増大することになる。これによりパワー変換回路の制御応答が悪化したり、これらの素子をアーム構成で使用する場合はデッドタイムが減少するなど、各種の弊害が発生する。この弊害を回避するには、ターンオフ動作時に、ターンオフ遅延時間の期間ではゲート抵抗を小さく、コレクタ電流下降時間の期間でゲート抵抗を大きくする等、動的にゲート抵抗を変化させることや、能動素子を使用し、ゲート電流をコントロールする方法がある。

【0008】

この問題に対し、特許文献1ではゲート抵抗と絶縁ゲート型スイッチ素子のゲート端子の接続点にゲート電位制御回路を接続し、ターンオン時にはゲート電位制御回路より適量の電荷を放電することでターンオンの速さを抑制し、ターンオフ時にはゲート電位制御回路より適量の電荷を充電することでターンオフの速さを抑制することで、サージ電圧を抑制するものである。しかしながら、ゲート電位制御回路にはゲート電位を検知する回路、ゲート電位を充放電する回路が必要であり、ゲート駆動回路が複雑化し大規模になってしまう難点があった。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2003−70233号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

絶縁ゲート型半導体スイッチ素子のゲート駆動回路において、ターンオフ時の遅延時間の短縮とサージ電圧に関与するdi/dtの抑制との相反する問題を、複雑な回路なしで単純な回路のみで解決するものである。

【課題を解決するための手段】

【0011】

請求項1の発明によれば、絶縁ゲート型半導体スイッチ素子と、該絶縁ゲート型半導体スイッチ素子のゲート端子とゲート補助端子間にオン用ゲート電源とオン用スイッチとオン用ゲート抵抗の直列体よりなるオン回路を接続し、前記絶縁ゲート型半導体スイッチ素子のゲート端子とゲート補助端子間に第1のオフ用ゲート抵抗とオフ用スイッチとオフ用電源の直列体よりなるオフ回路を接続し、該第1のオフ用ゲート抵抗にコンデンサと第2のオフ用ゲート抵抗の直列体を並列接続してなることを特徴とする。

【0012】

請求項2の発明によれば、請求項1に記載のゲート駆動回路において、前記第1のオフ用ゲート抵抗より前記第2のオフ用ゲート抵抗の抵抗値が小さく、前記コンデンサと前記第2オフ用ゲート抵抗で構成するCR回路の時定数が前記絶縁ゲート型半導体スイッチ素子のターンオフ遅れ時間と同等であることを特徴とする。

【発明の効果】

【0013】

本発明のゲート駆動回路によれば、絶縁ゲート型半導体スイッチ素子のターンオフ時において、遅延時間に関する期間はゲート抵抗を小さくして遅延時間を短縮し、di/dtに関与する期間はゲート抵抗を大きくしてdi/dtを抑制する動作を単純な回路で構成できる。

【図面の簡単な説明】

【0014】

【図1】本発明のゲート駆動回路を示す回路図である。

【図2】本発明のゲート駆動回路の動作を説明するタイミングチャートである。

【図3】従来技術のゲート駆動回路を示す回路図である。

【図4】従来技術のゲート駆動回路の動作を説明するタイミングチャートである。

【発明を実施するための形態】

【0015】

ターンオフ時の遅延時間の短縮と、di/dtの抑制という目的を、回路の複雑化を伴わずに実現した。以下、本発明の実施の形態について説明する。

【実施例1】

【0016】

図1は、本発明のゲート駆動回路を示す回路図である。図2は本発明のゲート駆動回路の動作を説明するタイミングチャートである。図1では駆動対象の絶縁ゲート型半導体スイッチ素子としてIGBTを例にした。以下に図1の回路の動作について図2を交えて説明する。

【0017】

駆動対象IGBT5をターンオンさせる場合、オン用スイッチ3を閉に、オフ用スイッチ4を開にする。このとき、オン用電源1の正極からオン用スイッチ3、オン用ゲート抵抗12、ゲート端子6、駆動対象IGBT5のゲート−エミッタ間容量を介し、オン用電源1の負極に至る閉回路が形成される。この状態で時間が経過すると、ゲート−エミッタ間電圧VGEがスレッショルド電圧に達し駆動対象IGBT5はターンオンを始める。ターンオンに関しては従来技術と同様なので以降の説明は省略する。

【0018】

一方、駆動対象IGBT5をターンオフさせる場合、オン用スイッチ3を開に、オフ用スイッチ4を閉にする。このとき、オフ用電源2の正極から駆動対象IGBT5のゲート−エミッタ間容量、ゲート端子6、第1のオフ用ゲート抵抗13、オフ用スイッチ4を介し、オフ用電源2の負極に至る閉回路1と、オフ用電源2の正極から駆動対象IGBT5のゲート−エミッタ間容量、ゲート端子6、コンデンサ15、第2のオフ用ゲート抵抗14、オフ用スイッチ4を介し、オフ用電源2の負極に至る閉回路2の2つの放電経路が形成される。ここで、第1のオフ用ゲート抵抗13を経由する放電電流をIG(OFF1)、コンデンサ15と第2のオフ用ゲート抵抗14を経由する放電電流をIG(OFF2)とする。

【0019】

IG(OFF1)の初期ピーク値は、オン用電源1の電圧V(ON)とオフ用電源2の電圧V(OFF)の和を、第1のオフ用抵抗13の抵抗値RG(OFF1)で除した値となり、減衰は駆動対象IGBT5のゲート容量と第1のオフ用ゲート抵抗13の時定数で決定される。同様にIG(OFF2)の初期ピーク値は、V(ON)+V(OFF)を第2のオフ用抵抗14の抵抗値RG(OFF2)で除した値となり、減衰は駆動対象IGBT5のゲート容量とコンデンサ15の合成容量と第2のオフ用ゲート抵抗14の時定数で決定される。ここで、第1のオフ用ゲート抵抗13と第2のオフ用ゲート抵抗14の抵抗値の大小関係をRG(OFF1)>RG(OFF2)とすると、IG(OFF1)とIG(OFF2)の初期ピーク値の大小関係は図4のとおりとなる。また、コンデンサ15と第2のオフ用ゲート抵抗14の時定数を十分小さくすると、IG(OFF1)とIG(OFF2)の減衰時間の関係も図4のとおりとなる。

【0020】

ターンオフ時のゲート容量放電回路のうち、閉回路2の第2のオフ用ゲート抵抗14の抵抗値を許容できる最小限の値として、なおかつコンデンサ15と第2のオフ用ゲート抵抗14の時定数を所望の遅延時間td(OFF)相当に選定すると、ターンオフ動作開始時からコレクタ電流ICの遮断を始める間に、閉回路1と比較して大量のゲート容量を放電し、ターンオフ遅延時間を大幅に短縮する。ターンオフ動作開始から時間が経過し、コレクタ電流ICの遮断が始まる頃になると、閉回路2のコンデンサ15は十分充電されIG(OFF2)は十分減衰する。この時点で駆動対象IGBT5のゲート容量放電回路は閉回路1のみになり、コレクタ電流ICの遮断開始以降はゲート容量の放電は緩やかになる。ここで、所望のコレクタ電流下降時間tfになるよう閉回路1の第1のオフ用ゲート抵抗13の抵抗値を選定すると、di/dtが抑制されコレクタ−エミッタ間電圧VCEのサージ電圧も十分抑制できる。

【0021】

上記の動作を言い換えると、コンデンサ15と第2のオフ用ゲート抵抗14の直列体は、駆動対象IGBT5のターンオフ遅延時間td(OFF)相当の時間のみ、第1のオフ用ゲート抵抗13をバイパスする回路とみなすことができる。

【産業上の利用可能性】

【0022】

複雑な制御回路や検出回路を用いることなく受動素子の定数選定のみで、ターンオフ時の遅延時間短縮、サージ電圧の低減を実現でき、半導体スイッチ素子を組込んだ装置の制御性の改善、ノイズの低減、スナバ回路の削減による装置の小型化などを目的とした用途に適用できる。

【符号の説明】

【0023】

1 オン用電源

2 オフ用電源

3 オン用スイッチ

4 オフ用スイッチ

5 駆動対象IGBT

6 ゲート端子

7 コレクタ端子

8 エミッタ端子

9 第1のゲート抵抗

10 第2のゲート抵抗

11 ダイオード

12 オン用ゲート抵抗

13 第1のオフ用ゲート抵抗

14 第2のオフ用ゲート抵抗

15 コンデンサ

【特許請求の範囲】

【請求項1】

絶縁ゲート型半導体スイッチ素子と、該絶縁ゲート型半導体スイッチ素子のゲート端子とゲート補助端子間にオン用ゲート電源とオン用スイッチとオン用ゲート抵抗の直列体よりなるオン回路を接続し、前記絶縁ゲート型半導体スイッチ素子のゲート端子とゲート補助端子間に第1のオフ用ゲート抵抗とオフ用スイッチとオフ用電源の直列体よりなるオフ回路を接続し、該第1のオフ用ゲート抵抗にコンデンサと第2のオフ用ゲート抵抗の直列体を並列接続してなることを特徴とするゲート駆動回路。

【請求項2】

請求項1に記載のゲート駆動回路において、前記第1のオフ用ゲート抵抗より前記第2のオフ用ゲート抵抗の抵抗値が小さく、前記コンデンサと前記第2オフ用ゲート抵抗で構成するCR回路の時定数が前記絶縁ゲート型半導体スイッチ素子のターンオフ遅れ時間と同等であることを特徴とするゲート駆動回路。

【請求項1】

絶縁ゲート型半導体スイッチ素子と、該絶縁ゲート型半導体スイッチ素子のゲート端子とゲート補助端子間にオン用ゲート電源とオン用スイッチとオン用ゲート抵抗の直列体よりなるオン回路を接続し、前記絶縁ゲート型半導体スイッチ素子のゲート端子とゲート補助端子間に第1のオフ用ゲート抵抗とオフ用スイッチとオフ用電源の直列体よりなるオフ回路を接続し、該第1のオフ用ゲート抵抗にコンデンサと第2のオフ用ゲート抵抗の直列体を並列接続してなることを特徴とするゲート駆動回路。

【請求項2】

請求項1に記載のゲート駆動回路において、前記第1のオフ用ゲート抵抗より前記第2のオフ用ゲート抵抗の抵抗値が小さく、前記コンデンサと前記第2オフ用ゲート抵抗で構成するCR回路の時定数が前記絶縁ゲート型半導体スイッチ素子のターンオフ遅れ時間と同等であることを特徴とするゲート駆動回路。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−239361(P2012−239361A)

【公開日】平成24年12月6日(2012.12.6)

【国際特許分類】

【出願番号】特願2011−108539(P2011−108539)

【出願日】平成23年5月13日(2011.5.13)

【出願人】(000003115)東洋電機製造株式会社 (380)

【Fターム(参考)】

【公開日】平成24年12月6日(2012.12.6)

【国際特許分類】

【出願日】平成23年5月13日(2011.5.13)

【出願人】(000003115)東洋電機製造株式会社 (380)

【Fターム(参考)】

[ Back to top ]