Fターム[5J056BB00]の内容

論理回路 (30,215) | 目的、効果 (4,057)

Fターム[5J056BB00]の下位に属するFターム

Fターム[5J056BB00]に分類される特許

1 - 20 / 209

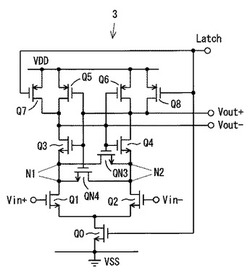

ラッチト・コンパレータ

【課題】差動回路の特性を損なうことなく、高速に信頼性の高いラッチ出力を行うラッチト・コンパレータを提供する。

【解決手段】ラッチト・コンパレータ(1)は、ドレイン・ソース間が、第1の電流経路上の第1のMOSトランジスタ(Q1)と第3のMOSトランジスタ(Q3)との間の第1のノード(N1)と、第2の電流経路上の第2のMOSトランジスタ(Q2)と第5のMOSトランジスタ(Q4)との間の第2のノード(N2)との間に接続されているとともに、ゲートが第1のCMOSインバータの出力に接続された、第7のMOSトランジスタ(QN3)と、ドレイン・ソース間が第1のノード(N1)と第2のノード(N2)との間に接続されているとともに、ゲートが第2のCMOSインバータの出力に接続された、第8のMOSトランジスタ(QN4)と、の少なくとも一方をさらに備えている。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体装置

【課題】積層され、貫通電極で相互に接続された複数の半導体チップの出力インピーダンスのバラツキを抑える。

【解決手段】半導体装置100は、第1の被制御チップ110と、第1の被制御チップ110を制御する制御チップ120とを備える。第1の被制御チップ110は、第1の出力回路と同一の構成を持つ第1のレプリカ出力回路111と、第1のレプリカ出力回路111に接続される第1のZQ端子112と、第1のZQ端子に接続される第1の貫通電極113と、第1のレプリカ出力回路111のインピーダンスを設定する第1の制御回路114と、を含む。制御チップ120は、第1の貫通電極113に接続される第2のZQ端子121と、第2のZQ端子121の電圧と参照電圧Vrefとを比較する比較回路122と、比較回路122からの比較結果に応じて処理を行う第2の制御回路123と、を含む。

(もっと読む)

ソースフォロア回路

【課題】複数段構成におけるソースフォロア回路において入出力レンジを確保する。

【解決手段】ソースフォロア部SF11、SF12間に、ゲートドレイン間がダイオード接続され且つソースフォロア部SF11およびSF12を構成するMOSトランジスタM11およびM12と同一チャネル種類のMOSトランジスタM13とそのドレインに接続された電流源C13とからなる接続部11を設け、前段のソースフォロア部SF11の出力端とMOSトランジスタM13のソースとを接続し、MOSトランジスタM13のドレインと後段のソースフォロア部SF12の入力端とを接続する。接続部11における入出力間の電圧レベルのシフト方向は、ソースフォロア部SF11、SF12における入出力間の電圧レベルのシフト方向と逆となり、電圧シフトを打ち消す方向に作用するため、電圧レベルのシフトにより入出力レンジが狭くなることを抑制することが可能となる。

(もっと読む)

半導体装置

【課題】より少ない調整ステップでキャリブレーションを完了する。

【解決手段】出力端子(DQに相当)と、出力端子と接続され、出力端子を調整可能なインピーダンスで駆動する出力回路(210に相当)と、出力回路のインピーダンスを段階的に調整するキャリブレーション回路(100)と、を備え、キャリブレーション回路は、キャリブレーション動作の実行を指示するコマンドを受けて、インピーダンスの調整を開始し、インピーダンスを変化させる変化幅を、開始直後に対し以降においてより狭めるように調整する。

(もっと読む)

スイッチ回路

【課題】多くの個別素子による回路を用いることなく、容易に簡素な回路構成で端子外れ検出を行うことが可能なスイッチ回路の提供。

【解決手段】ゲートがセンサ回路に接続され、ドレインが第1の電圧制限抵抗に接続された第1の出力ドライバと、物理量検出信号出力端子と接地端子の間に接続された第2の電圧制限抵抗と、非反転入力端子が第1の基準電圧回路に接続され、反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第1の比較器と、反転入力端子が第2の基準電圧回路に接続され、非反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第2の比較器と、ゲートが前記論理回路の出力に接続され、ドレインが断線診断信号出力端子に接続された第2の出力ドライバで構成した。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、エンファシスの有無により消費電流が変動する問題があった。

【解決手段】本発明の半導体装置は、抵抗値を、エンファシスモードにおいて第1の抵抗値とし、非エンファシスモードにおいて第1の抵抗値よりも小さな第2の抵抗値とする可変抵抗30と、出力インピーダンスを、エンファシスモードにおいて第3の抵抗値とし、非エンファシスモードにおいて前記第3の抵抗値よりも大きな第4の抵抗値とする第1の駆動部10と、出力インピーダンスを、エンファシスモードにおいて第5の抵抗値とし、非エンファシスモードにおいて第5の抵抗値よりも大きな第6の抵抗値とする第2の駆動部11と、入力信号に応じて第1、第2の駆動部の導通状態を制御すると共に、エンファシスモードと非エンファシスモードとにおいて第1、第2の駆動部の出力インピーダンスと可変抵抗の抵抗値を切り換える制御部と、を有する。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

電源電圧設定方法及び電源電圧設定プログラム

【課題】チップごとに適正な電源電圧を設定する。

【解決手段】チップのレイアウトデータ20からクリティカルパスのゲート遅延と配線遅延の遅延比を抽出する(ステップS1,S2)。チップのモニタ回路で実測されたゲート遅延及び配線遅延を、その遅延比に基づき合成して第1遅延値を生成し(ステップS3)、モニタ回路のシミュレーションで得られるゲート遅延及び配線遅延を、その遅延比に基づき合成して第2遅延値を生成する(ステップS4,S5)。このようにゲート遅延、配線遅延、クリティカルパスでの遅延比が考慮された第1遅延値及び第2遅延値に基づいて、チップに適用するチップ電源電圧を設定する(ステップS7)。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体装置

【課題】出力インピーダンスを切り替えた場合の出力トランジスタに対する電源配線抵抗等の見かけ上の変動を抑制し、出力インピーダンスを切り替えた際の出力インピーダンスの誤差を低減する。

【解決手段】本発明による半導体装置は、電源端子に接続された電源配線(10)と、出力端子に接続された信号配線(20)と、前記電源配線と前記信号配線との間に並列接続された複数のトランジスタ(TP1〜TP7,TN1〜TN7)と、前記複数のトランジスタのうち、特定のトランジスタ(TP4,TN4)を基準として前記電源配線および前記信号配線の長手方向において相互に対照をなす位置関係にあるトランジスタを単位として前記複数のトランジスタを選択的に活性化させる制御回路とを備える。

(もっと読む)

半導体装置

【課題】トランジスタが仮にディプレッション型である場合でも、安定して動作することができる半導体装置を提供する。

【解決手段】開示する発明の一態様の半導体装置は、第1の電位を第1の配線に供給する機能を有する第1のトランジスタと、第2の電位を第1の配線に供給する機能を有する第2のトランジスタと、第1のトランジスタのゲートに第1のトランジスタがオンをオンにするための第3の電位を供給した後、第3の電位の供給を止める機能を有する第3のトランジスタと、第2の電位を第1のトランジスタのゲートに供給する機能を有する第4のトランジスタと、第1の信号にオフセットを施した第2の信号を生成する機能を有する第1の回路と、を有し、第4のトランジスタのゲートには、第2の信号が入力され、第2の信号の最小値は、第2の電位未満の値である。

(もっと読む)

差動入力回路および差動入力回路の電圧特性調整方法

【課題】ソースが共通接続されそれぞれのゲートが二つの入力端子に接続さた二つのトランジスタを有する差動対を備える差動入力回路において、より適正に入力オフセットをより小さくする。

【解決手段】トランジスタTin1,トランジスタTin2のドレインに高電圧印加回路60を接続し、トランジスタTin1のソースおよびトランジスタTin2のソースと接地電圧印加点GNDとの間にトランジスタTsenを設け、論理ローレベルの電圧の制御信号SENをスイッチング回路70に入力すると共に制御信号Tcとしてクロック信号を入力して入力端子IN1に電圧V1を印加すると共に入力端子IN2に電圧V2を印加し、検出した出力端子OUT,OUTBの電圧に応じてトランジスタTin1,Tin2のドレインに高電圧印加回路60により電源電圧Vddhを印加する

(もっと読む)

半導体装置

【課題】 待機動作時のオフリーク電流を削減した論理回路を含む半導体装置を提供することを目的とする。

【解決手段】 半導体装置100は、第1の動作電圧または第1の動作電圧よりも小さい第2の動作電圧を供給する電源供給部110と、電源供給部110から第1または第2の動作電圧を受け取る低しきい値のP型トランジスタTpと、トランジスタTpと基準電位との間に接続されたN型トランジスタTnとを有し、トランジスタTp、Tnは、ゲートに入力された信号Dinに応じて出力信号Doutを生成する論理回路を構成する。電源供給部110は、通常動作時、第1の動作電圧をトランジスタTpのソースに供給し、待機動作時、第2の動作電圧をトランジスタTpのソースに供給する。第2の動作電圧は、トランジスタTp、Tnそれぞれのゲート・ソース間電圧の振幅がトランジスタTp、Tnのしきい値よりも大きくなるように設定される。

(もっと読む)

半導体装置

【課題】 単極性のトランジスタを用いたデジタル回路であっても、出力信号の振幅が小さくなってしまうことを防ぎ、正常に動作する手段を有する半導体装置を提供する。

【解決手段】 ダイオード接続されたトランジスタ101がオフすることによって、トランジスタ102のゲートが、フローティング状態となる。そのとき、トランジスタ102は、オン状態にあり、そのゲート・ソース間には電位差が生じている。

トランジスタ102がオン状態にあるため、トランジスタ102のソースの電位は上昇するが、トランジスタ102のゲート・ソース間の容量によって、ゲート・ソース間の電位が保持されており、かつトランジスタ102のゲートはフローティングとなっているため、容量結合効果によってトランジスタ102のゲートの電位も上昇する。その結果、出力信号の振幅が小さくなることを防ぐことが出来る。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr1Cで構成されるインバータ回路1において、トランジスタT2のゲートと高電圧線L3との間に接続されたトランジスタT4,T5と、トランジスタT2のゲートと低電圧線L1との間に接続されたトランジスタT3とのオンオフ動作により、全期間に渡ってトランジスタT1,T2が同時にオンしないようになっている。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

レベルコンバータ

【課題】ラッチ回路の初期値が確定可能であり、出力信号の立ち上がり/立ち下がり特性の対称性に優れたレベルコンバータを提供すること。

【解決手段】シフト回路12のラッチ回路31を構成する第1及び第2インバータ回路32,33の出力端子となるノードN1,N2とトランジスタTp1,Tp2との間に初期値設定用のMOSトランジスタTp3,Tp4を挿入接続した。そして、MOSトランジスタTp3のゲートをグランドに接続し、MOSトランジスタTp4のゲートを初期値設定回路34に接続した。初期値設定回路34は、第2の高電位電源VDEが所定レベル以下の場合には該MOSトランジスタTp4のゲート電位を第2の高電位電源VDEとグランドとの間の中間電位に制御し、第2の高電位電源VDEが所定レベルより高い場合には該MOSトランジスタTp4をオンするようそのゲート電位をグランドレベルに制御する。

(もっと読む)

クロックバッファ回路及びクロック分配回路

【課題】クロック源の消費電力を増大させることなく、動作クロック周波数に応じて駆動能力を変化させることにより消費電力低減可能なクロックバッファ回路を提供すること。

【解決手段】クロック信号を伝達するバッファ部102と、クロック信号の参照クロック信号に対する逓倍数をカウントし、バッファ部102に対して逓倍数に基づいたイネーブル信号を出力する駆動能力切替部101と、を備え、バッファ部102は、当該バッファ部102の入力に接続された入力インバータ7と、イネーブル信号によりオンオフが可能であって、それぞれの出力が当該バッファ部の出力に共通に接続された複数の出力インバータ13〜28と、を備え、入力インバータ7が1個のCMOSインバータからなるクロックバッファ回路。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

1 - 20 / 209

[ Back to top ]