Fターム[5J056BB01]の内容

Fターム[5J056BB01]の下位に属するFターム

速度の向上、高速化 (478)

低速化 (1)

入力しきい値の可変、制御 (40)

駆動能力の改善 (144)

消費電力の低減 (646)

動作電圧の低電圧化 (92)

貫通電流の除去・低減 (133)

Fターム[5J056BB01]に分類される特許

1 - 20 / 56

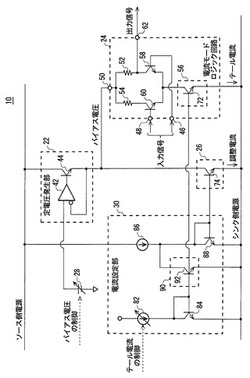

ドライバ回路および試験装置

【課題】出力信号の応答特性および消費電流を一定にする。

【解決手段】入力信号の論理に応じた電圧の出力信号を出力するドライバ回路であって、定電圧のバイアス電圧を発生する定電圧発生部と、内部に流れる定電流の電流値に応じて出力信号の振幅が定まり、バイアス電圧の電圧値に応じて出力信号の電位が定まり、入力信号の論理に応じた電圧の出力信号を出力する電流モードロジック回路と、定電圧発生部におけるバイアス電圧の出力端から、設定された電流値の定電流を流し出す調整用定電流源と、電流モードロジック回路内に流れる定電流の電流値に応じて、調整用定電流源に流す定電流の電流値を予め設定する電流設定部とを備えるドライバ回路を提供する。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファ回路を含む出力回路(101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(150)と、複数の単位バッファ回路のそれぞれのインピーダンスを調整するインピーダンス調整部(130)であって、複数の単位バッファ回路のうちの1つと実質的に同一の調整可能なインピーダンスを有するレプリカ回路(131e)と、当該レプリカ回路と並列に接続され、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数に応じて自身を流れる電流量を変化させる負荷電流生成回路(131f)とを含む、インピーダンス調整部と、を備えることを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

レベルシフト回路

【課題】出力電圧の立ち上がりの遅延時間と立ち下がりの遅延時間との差異を低減することが可能なレベルシフト回路を提供する。

【解決手段】出力電圧の立ち上がりの遅延時間と出力電圧の立ち下がりの遅延時間とが互いに異なるレベルシフト部F1、F2が複数段接続されている。そして、前段のレベルシフト部F1の出力電圧の立ち下がりの遅延時間を後段のレベルシフト部F2の出力電圧の立ち上がりの遅延時間で補償し、前段のレベルシフト部F1の出力電圧の立ち上がりの遅延時間を後段のレベルシフト部F2の出力電圧の立ち下がりの遅延時間で補償する。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファを含む出力回路(出力バッファ101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(出力制御回路150)と、複数の単位バッファのそれぞれのインピーダンスを調整するインピーダンス調整部であって、当該インピーダンス調整部は、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数が変化することに応じて複数の単位バッファのそれぞれのインピーダンスを調整する、インピーダンス調整部(インピーダンス調整部30)と、を備える。

(もっと読む)

半導体装置、及び出力バッファのインピーダンスを調整する方法

【課題】出力バッファのインピーダンスを制御する複数の制御ビットを転送するデータバスの配線面積を削減できる半導体装置、及び出力バッファのインピーダンスを調整する方法を提供する。

【解決手段】インピーダンス制御情報を生成するZQ回路(ZQ回路40)と、前記インピーダンス制御情報を受けて自身のインピーダンスが制御される出力バッファ(出力回路80)と、を備え、前記インピーダンス制御情報を構成する複数の制御ビット情報は前記ZQ回路からシリアルに転送される。

(もっと読む)

スルーレートコントロール装置、スルーレートコントロール方法

【課題】クロック信号の出力バッファにおいて、クロック信号の周波数に応じたスルーレートの調整を行うことによりEMIノイズを抑制することが可能なスルーレートコントロール装置、およびスルーレートコントロール方法を提供すること。

【解決手段】変換ゲインGiに応じて、入力されるVCO入力電圧Viをクロック信号CKoに変換する電圧制御発振器15aを有するPLL回路24aと、VCO入力電圧Viおよび変換ゲインGiの各々に対して正の相関関係を有する制御電流Ibを出力する電圧電流変換器19aと、制御電流Ibに応じてドライブ電流を設定するバッファ制御回路21aと、ドライブ電流で、クロック信号CKoを出力する出力回路22aとを備える。よって、クロック信号CKoの周波数fに比例して出力回路22aのドライブ能力が大きくなる関係を有し、周波数fに応じて好適なスルーレートが決定することができる。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路のデータレートの変化時に発生するスキューを抑制する。

【解決手段】一つの実施形態によれば、レベルシフト回路には第1及び第2のレベルシフタが設けられる。第1のレベルシフタは、第1乃至4のトランジスタが設けられ、レベルシフトされた第1の出力信号を出力する。第2のレベルシフタは、第5乃至8のトランジスタが設けられ、レベルシフトされた第1の出力信号とは逆位相の第2の出力信号を出力する。第1の入力信号が入力される第1のトランジスタと差動対をなす第2のトランジスタに、第1の入力信号とは逆位相のハイレベルの第2の入力信号が入力されると第3及び4のトランジスタも同時にオンする。第2の入力信号が入力される第5のトランジスタと差動対をなす第6のトランジスタに、ハイレベルの第1の入力信号が入力されると第7及び8のトランジスタも同時にオンする。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

差動信号出力装置、および、携帯機器

【課題】出力信号のスルーレートをより適切に制御することが可能な差動信号出力装置を提供する。

【解決手段】差動信号出力装置は、差動信号およびコモンモード信号を重畳して出力するための第1の送信端子および第2の送信端子を備える。差動信号出力装置は、データ信号に応じて前記差動信号を生成し前記第1の送信端子および前記第2の送信端子に出力する差動信号生成回路を備える。差動信号出力装置は、クロック信号に応じて前記コモンモード信号を生成し前記第1の送信端子および前記第2の送信端子に出力し、且つ、制御信号に応じて前記コモンモード信号のスルーレートを制御するコモンモード信号生成回路を備える。

(もっと読む)

半導体装置

【課題】立ち上がり時間と立ち下がり時間の差を解消しつつ、動作に伴う貫通電流の発生が防止されたレベルシフト回路を提供する。

【解決手段】互いに同じ回路構成を有するレベルシフト回路LV1,LV2と、レベルシフト回路LV1,LV2に相補の入力信号をそれぞれ供給する入力回路と、レベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡する出力回路とを備える。本発明によれば、同じ回路構成を有する2つのレベルシフト回路LV1,LV2を用いるとともに、これらレベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡していることから、レベルシフト回路LV1,LV2の動作速度差による貫通電流の発生がほとんど生じない。

(もっと読む)

ドライバアンプ回路および通信システム

【課題】バイアス調整回路やプリドライバ回路が不要で、しかも出力波形の波形歪みを低減することが可能なドライバアンプ回路および通信システムを提供する。

【解決手段】スイッチングトランジスタM11〜M14を駆動するゲート電圧を均一にするため、スイッチングトランジスタM11〜M14を電源およびGND側に配置し、さらに、スイッチングトランジスタM11〜M14の駆動振幅を安定させるために、各スイッチングトランジスタM11のドレインと出力ノードND11、ND12間にそれぞれ第1から第4の抵抗素子R11〜R14を接続している。

(もっと読む)

信号駆動回路

【課題】DCオフセットを低減し、正確な出力アナログ電圧値を得る信号駆動回路を提供する。

【解決手段】信号駆動回路は、デジタルデータに基づいて第一アナログ電圧を発生するデジタル/アナログコンバータ(DAC)と、第一アナログ電圧に基づいてアナログバッファによって第二アナログ電圧をロードに選択的に出力、またはアナログバッファを通過することなしに第一アナログ電圧をロードに選択的に出力する出力回路とを含む。

(もっと読む)

差動信号生成回路

【課題】位相差が減少された差動信号を生成するようにした差動信号生成回路を提供する。

【解決手段】入力信号を順次反転させて複数の遅延信号を生成するように構成されたインバータアレイと、複数の遅延信号のうち、第1の遅延信号と第2の遅延信号とを予め設定された混合比で混合して第1の差動信号を生成するように構成された位相混合器とを備え、複数の遅延信号のうち、第1の遅延信号と第2の遅延信号との中間に該当する遅延時間を持つ第3の遅延信号を第2の差動信号として生成するように構成されることを特徴とする。

(もっと読む)

レベル変換回路

【課題】安定したレベル変換を行う。

【解決手段】回路ブロック21,22は、それぞれ、ノードN14、N15に現れる電位0Vと電位HVとにより2つの論理値0,1が表される高電圧の論理信号を、電位VGと電位(VG+LL)とにより2つの論理値0,1が表される低電圧の論理信号に変換し、出力端子Poutから、この論理信号を出力する。回路ブロック22の各トランジスタは、回路ブロック21のそれらを逆極性の素子で置き換えた形となっており、電位VGを変化させたときに回路ブロック21,22のいずれかの動作が困難になった場合でも、もう一方が正常に動作する。このため、安定したレベル変換を行うことができる。

(もっと読む)

レベルシフト回路

【課題】レベル変換における動作範囲を広くする。

【解決手段】第1の電位(VDD1)の波高値を有する入力パルス信号(VIN)を入力するCMOSインバータ回路(P1、N1)と、第1の電位よりも高電位となる第2の電位(VDD2)の電源で動作し、一端(ND1)をCMOSインバータ回路の出力端に接続し、他端から第2の電位の波高値を有し入力パルス信号と同相の出力パルス信号(VOUT)を出力するラッチ回路(INV1、P3)と、第1の電位以上かつ第2の電位未満の電源供給をCMOSインバータ回路に対して行う電源供給回路(P2、INV2)と、を備え、電源供給回路は、入力パルス信号が少なくとも接地レベルとなる場合に電源供給を制限するように機能する。

(もっと読む)

デューティサイクル補正を行う方法

【課題】不均一なデューティサイクルを有する入力信号のデューティサイクル補正を行う方法を提供する。

【解決手段】不均一なデューティサイクルを有する入力信号をコンデンサ・デジェネレイティング差動対回路に入力し、前記回路内の1つ以上のコンデンサの両端に、前記入力信号のデューティサイクルの正の部分と負の部分との継続時間の差を表わす直流電圧を形成し、差動対回路のスイッチング動作を通じてデューティサイクルを有する出力信号を形成し、それによって出力信号のデューティサイクルの正の部分と負の部分の継続時間が、入力信号とスイッチングレベルとの交差点により規定される。必要に応じて、出力信号のデューティサイクルが少なくとも実質的に均一になるまで、信号(およびスイッチングレベル)が調整される。

(もっと読む)

入力回路

【課題】ヒステリシス電圧や応答速度の電源電圧依存性を緩和し、幅広い範囲の電源電圧条件下で動作するヒステリシス特性を有する入力回路を提供すること。

【解決手段】低電源電圧条件下でヒステリシス電圧が小さくなる回路(PMOSトランジスタ101〜103及び、インバータ501)と、低電源電圧条件下でヒステリシス電圧が大きくなる回路(PMOSトランジスタ101、104及び、インバータ501)とを設けた。

(もっと読む)

半導体装置、出力回路、及び、半導体装置における入出力バッファ回路の制御方法

【課題】異なる電源電圧で使用されることが考えられる半導体装置において、好適な出力回路を有する半導体装置を提供する。

【解決手段】少なくとも出力端子の機能を有する信号端子と、電源端子と、電源端子から電源電圧が供給され内部出力信号を受けて信号端子を駆動する第一及び第二の出力バッファ回路を備えた出力回路と、電源電圧を判定し出力回路の動作を制御する電源電圧判定回路と、を備え、電源電圧判定回路が、第1の電位にあると判定したときには、第1の出力バッファ回路を活性化させると共に、第2の出力バッファ回路を非活性化させ、第2の電位にあると判定したときには、前記第1、第2の出力バッファ回路を共に活性化させる。

(もっと読む)

基準電圧生成回路、集積回路装置、電気光学装置、及び電子機器

【課題】駆動時間を十分に確保し、高精度な電圧を出力する。

【解決手段】基準電圧生成回路11は、電圧生成回路12と電圧生成回路からの出力をインピーダンス変換するアンプ部14を含み、アンプ部に含まれる増幅回路GAM1〜GAMnは、入力ノードNI、第1のノードN1間に設けられる第1のスイッチ素子SW1と、第1のノードN1、サミングノードNEG間に設けられる第1のキャパシタC1と、第1のノードN1、アナログ基準電源AGND間に設けられる第2のスイッチ素子SW2と、第2のノードN2、サミングノードNEG間に設けられる第2のキャパシタC2と、第2のノードN2、出力ノードNQ間に設けられる第3のスイッチ素子SW3と、第2のノードN2、アナログ基準電源AGND間に設けられる第4のスイッチ素子SW4と、出力ノードNQ、サミングノードNEG間に設けられる第5のスイッチ素子SW5とを含む。

(もっと読む)

1 - 20 / 56

[ Back to top ]