Fターム[5J056BB02]の内容

Fターム[5J056BB02]の下位に属するFターム

大電流化による高速化

大電圧化による高速化 (6)

蓄積電荷対策 (3)

プリチャージによる高速化 (3)

しきい値の設定による高速化 (23)

フィードバックによる高速化 (3)

Fターム[5J056BB02]に分類される特許

1 - 20 / 440

レベルシフト回路

【課題】レベルシフト回路を高速動作する。

【解決手段】一つの実施形態によれば、レベルシフト回路は、第一のトランジスタ、第二のトランジスタ、第一のコンデンサ、及び第二のコンデンサが設けられる。第一のトランジスタは、制御端子に入力電圧が入力される。第二のトランジスタは、制御端子に入力電圧の反転信号が入力される。第一のコンデンサは、一端が第一のトランジスタの第一の端子に接続され、他端に入力電圧の反転信号が入力され、入力電圧の立ち上りのときに電荷を蓄積して第一のトランジスタの第一の端子側から一端側へ第一の電流を発生する。第二のコンデンサは、一端が第二のトランジスタの第一の端子に接続され、他端に入力電圧が入力され、入力電圧の立ち下りのときに電荷を蓄積して第二のトランジスタの第一の端子側から一端側へ第二の電流を発生する。

(もっと読む)

レベルシフター回路、集積回路装置、電子時計

【課題】 出力信号にスパイクノイズが乗ることや、応答速度が遅くなることを防止するレベルシフター回路を提供する。

【解決手段】 第1の高電位と第1の低電位とを電源電位とする第1の電位系の入力信号Aを受け取り、第1の電位系の信号である第1の信号XAを出力する第1の回路10と、第2の高電位と第2の低電位とを電源電位とする第2の電位系の、入力信号に応じた出力信号Yを生成する第2の回路20と、入力信号を受け取り、第1の電位系の信号であって入力信号と論理的に等価な第2の信号Bを生成するバッファー回路と、を含み、第2の回路は、第2の信号を受け取り、第3の信号XDを出力する初段インバーターと、第1の信号に基づいて、初段インバーターと第2の高電位を供給する電源又は第2の低電位を供給する電源との接続、切断を切り換える初段スイッチと、を含み、第3の信号に基づいて出力信号を生成する。

(もっと読む)

ラッチト・コンパレータ

【課題】差動回路の特性を損なうことなく、高速に信頼性の高いラッチ出力を行うラッチト・コンパレータを提供する。

【解決手段】ラッチト・コンパレータ(1)は、ドレイン・ソース間が、第1の電流経路上の第1のMOSトランジスタ(Q1)と第3のMOSトランジスタ(Q3)との間の第1のノード(N1)と、第2の電流経路上の第2のMOSトランジスタ(Q2)と第5のMOSトランジスタ(Q4)との間の第2のノード(N2)との間に接続されているとともに、ゲートが第1のCMOSインバータの出力に接続された、第7のMOSトランジスタ(QN3)と、ドレイン・ソース間が第1のノード(N1)と第2のノード(N2)との間に接続されているとともに、ゲートが第2のCMOSインバータの出力に接続された、第8のMOSトランジスタ(QN4)と、の少なくとも一方をさらに備えている。

(もっと読む)

ドライバ回路および試験装置

【課題】出力信号の応答特性および消費電流を一定にする。

【解決手段】入力信号の論理に応じた電圧の出力信号を出力するドライバ回路であって、定電圧のバイアス電圧を発生する定電圧発生部と、内部に流れる定電流の電流値に応じて出力信号の振幅が定まり、バイアス電圧の電圧値に応じて出力信号の電位が定まり、入力信号の論理に応じた電圧の出力信号を出力する電流モードロジック回路と、定電圧発生部におけるバイアス電圧の出力端から、設定された電流値の定電流を流し出す調整用定電流源と、電流モードロジック回路内に流れる定電流の電流値に応じて、調整用定電流源に流す定電流の電流値を予め設定する電流設定部とを備えるドライバ回路を提供する。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、シリアライザの負荷を抑制する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、n×2本の入力信号線から相補な内部データ信号DAT0/DAC0〜DAT3/DAC3を受信し、内部データ信号DT1/DC1をシリアルに出力する。プルアップバッファ回路100とプルダウンバッファ回路200は、内部データ信号DT1/DC1により制御される。

(もっと読む)

半導体装置

【課題】ストローブ信号の変化によって基準電位に重畳するノイズを低減し、これにより、基準電位を用いる入力レシーバ回路の動作マージンの低下を防止する。

【解決手段】ストローブ信号IDQSTによって活性化され、入力信号DQの電位と基準電位VREFとを比較することによって出力信号IDQRを生成する入力レシーバ回路17Rと、ストローブ信号IDQSTの変化によって基準電位VREFに生じるノイズをキャンセルするノイズキャンセラ100Tとを備える。本発明によれば、ノイズキャンセラ100Tによって基準電位VREFに生じるノイズがキャンセルされることから、入力レシーバ回路17Rの動作マージンを十分に確保することができる。これにより、高速なデータ転送を行うことが可能となる。

(もっと読む)

論理回路及びデータ処理システム

【課題】素子数が少なく、遅延が小さく、ドライバ能力を有するXORゲート回路を提供する。

【解決手段】論理回路1は、電源電位VPERIとノードn1の間に接続されたトランジスタT1と、電源電位VPERIとノードn2の間に接続されたトランジスタT2と、電源電位VSSとノードn3の間に接続されたトランジスタT3と、電源電位VSSとノードn4の間に接続されたトランジスタT4と、ノードn1とノードn3の間に直列接続されたトランジスタT5,T7と、ノードn1とノードn3の間に直列接続されたトランジスタT9,T11と、ノードn2とノードn4の間に直列接続されたトランジスタT6,T8と、ノードn2とノードn4の間に直列接続されたトランジスタT10,T12とを備える。出力信号Yは、トランジスタT5,T7の接続点及びトランジスタT6,T8の接続点から取り出される。

(もっと読む)

半導体装置

【課題】出力信号の立ち上がり時間および立下り時間が短い半導体装置を提供する。

【解決手段】このクロックドライバは、クロック信号CLKBの反転信号CLKを出力ノードN2に出力するインバータ1と、電源電圧VCCのラインと出力ノードN2との間に直列接続されたトランジスタP2,P3と、出力ノードN2と接地電圧VSSのラインとの間に直列接続されたトランジスタQ2,Q3と、クロック信号CLKを所定時間だけ遅延させてトランジスタP2,Q3のゲートに与える遅延回路3とを含む。たとえば、クロック信号CLKBが「L」レベルから「H」レベルに変化すると、所定時間だけトランジスタQ2,Q3がともにオンして、出力ノードN2から電流を引き抜く。

(もっと読む)

信号出力回路

【課題】広いダイナミックレンジと良好な周波数特性を得ることができる信号出力回路を提供する。

【解決手段】実施形態の信号出力回路は、ゲート端子へ一定の電圧Vgが印加され、ソース端子へ入力信号INが印加されるゲート接地型のNMOSトランジスタ1と、ゲート端子がNMOSトランジスタ1のドレイン端子に接続され、ソース端子から出力信号OUTが出力されるソースフォロワであるNMOSトランジスタ2とを備える。この信号出力回路は、バックゲートバイアス生成部3が、NMOSトランジスタ1およびNMOSトランジスタ2のバックゲート端子へ印加する共通のバックゲートバイアス電圧Vbを生成する。

(もっと読む)

複数磁束量子出力ドライバ及び電子デバイス

【課題】 複数磁束量子出力ドライバ及び電子デバイスに関し、占有面積やバイアス電流を増加することなく高速のデーターレートや広いパルス幅を有した出力信号を発生する。

【解決手段】 一つの単一磁束量子パルスを複数に分配するスプリッタの一方の出力側の終端に単一磁束量子パルス反射回路からなる第1の磁束量子回路を接続し、スプリッタの他方の出力側に第2の磁束量子回路を接続する。

(もっと読む)

集積回路装置

【課題】断熱動作を行う回路への電源電圧の供給を最適化することで好適な動作特性を実現する。

【解決手段】集積回路装置が、CPU10と電源生成回路40とを具備している。当該集積回路装置が高速モードに設定されると、電源生成回路40が直流の電源電圧をCPU10に供給する。この場合、CPU10は、通常のCMOS動作を行う。一方、当該集積回路装置が小電力モードに設定されると、電源生成回路40が交流の電源電圧をCPU10に供給する。CPU10は、複数の交流の電源電圧が供給されることで断熱動作を行う。該交流の電源電圧の少なくとも2つの電源電圧は、互いに、プルアップ及び/又はプルダウンのタイミングと、デューティ比とが異なっている。

(もっと読む)

半導体装置

【課題】適宜繰り返し行われるキャリブレーションに要する時間を短縮する。

【解決手段】半導体装置は、入力コマンドに応じ、出力ドライバーのインピーダンスを調整するキャリブレーションを、設定値を用いて行うキャリブレーション回路と、温度センサーと、前記出力ドライバーの温度特性情報を記憶する記憶回路と、前記温度センサーからの検出信号と前記記憶回路から読み出した前記温度特性情報とに基づいて前記設定値を変更する設定信号を生成し、前記キャリブレーション回路へ出力する設定回路と、を備える。

(もっと読む)

半導体装置

【課題】信号伝送のより高速化を図る。

【解決手段】入力信号Vinと基準信号Vrefとを入力する第1の差動対(Q3、Q4が相当)と、第1の差動対のそれぞれ負荷となる第1及び第2のトランジスタQ2、Q1と、を含む第1の入力回路を備え、第1の入力回路の出力側となる第1のトランジスタQ2は、第2のトランジスタQ1に比べてゲート幅を長くする。

(もっと読む)

半導体装置

【課題】出力信号を高速に変化させかつオーバーシュートやアンダーシュートを抑制できるようにする。

【解決手段】入力信号を反転して出力する主ドライバ11に加えて、補助ドライバ12を設け、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、変化開始から主ドライバの出力信号がある電圧レベルを超えるまでの期間では信号変化を補助するように制御部15により補助ドライバの動作を制御し、主ドライバの出力信号がある電圧レベルを超えてから第2の電圧レベルになるまでの期間に信号変化を抑制するように制御部により補助ドライバの動作を制御するようにして、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制できるようにする。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】素子面積の増加を抑制しつつ、動作速度が向上する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、ボディ領域11a、11bと、ボディ領域11a、11b上にゲート絶縁層12a、12bを介して配置されるゲート電極13a、13bと、ボディ領域11a、11bを挟んで配置される一対のソース/ドレイン領域14a、14b、14cと、を有する電界効果型トランジスタ10a、10bを複数備え、複数のトランジスタ10a、10bは、ボディ領域11a、11b同士が電気的に接続されており、複数のトランジスタ10a、10bの内の一のトランジスタ10aのゲート電極13aのみが、複数のトランジスタ10a、10bの内の何れかのトランジスタのボディ領域と電気的に接続される。

(もっと読む)

CMOS論理集積回路

【課題】異なる論理レベルの信号を高速に伝達可能なCMOS論理集積回路を提供する。

【解決手段】レベルシフト回路とCMOS論理回路とを備えたことを特徴とするCMOS論理集積回路が提供される。前記レベルシフト回路は、第1の低電位と前記第1の低電位よりも高い第1の高電位との間で変化する第1の論理レベルの信号を前記第1の低電位と前記第1の高電位よりも高い第2の高電位との間で変化する第2の論理レベルの信号に変換する。前記CMOS論理回路は、前記第1の論理レベルの第1の信号がゲートに入力される第1のNチャンネル形MOSFETと、前記第1のNチャンネル形MOSFETに直列に接続され前記第1の信号と反転関係にある前記第2の論理レベルの第2の信号がゲートに入力される第2のNチャンネル形MOSFETとを有する。

(もっと読む)

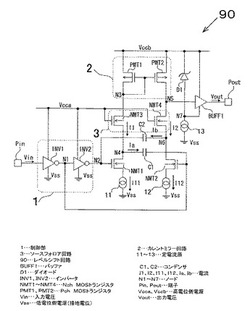

レベルシフト回路

【課題】伝播遅延時間を短縮する。

【解決手段】インバータINV1,INV2と、ラッチ回路1と、反転駆動回路2,3と、セレクタ4を備える。N1=VSS2、N2=VSS2、N3=VSS2、N4=VDD2のとき、入力端子INがVDD1→VSS1に変化したとき、トランジスタMP5をオンして大きな電流をVDD2からノードN1に流し高速にノードN1をVSS1→VDD2に変化させる。その後、トランジスタMP5はオフし、ノードN1はインバータINV4でVDD2に保持される。これで、N1=VDD2、N2=VDD2、N3=VDD2、N4=VSS2となる。次に入力端子INがVSS1→VDD1に変化したとき、トランジスタMN2がオンして大きな電流をノードN1からVSS2に流し高速にノードN1をVDD2→VSS2に変化させる。

(もっと読む)

1 - 20 / 440

[ Back to top ]