Fターム[5J056BB51]の内容

Fターム[5J056BB51]の下位に属するFターム

素子数の低減 (51)

入出力数、ピン数の低減 (94)

電源の簡素化 (16)

クロック数の低減 (1)

チップサイズの小型化 (160)

Fターム[5J056BB51]に分類される特許

1 - 20 / 108

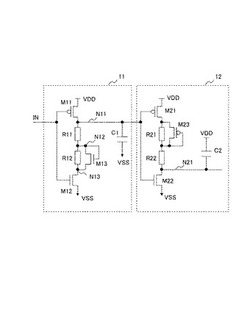

半導体装置

【課題】容量を充放電させ信号を遅延させる回路の遅延時間の温度依存性を緩和し回路規模の増大を抑制可能とした半導体装置の提供。

【解決手段】互いに異なる電源電圧を与える第1の電源(VDD)と第2の電源(VSS)の間に直列に接続され、制御電極が共通に接続された第1及び第2のFET(M11、M12)と、前記第1及び第2のFETの間に接続する第1の回路を有するインバータを備え、前記第1の回路は、互いに並列に接続された第1の抵抗素子(R12)と第3のFET(M13)を備え、前記第1の抵抗素子(R12)の抵抗値は正の温度特性を有し、前記第3のFET(M13)は、その動作範囲に、第3のFET(M13)の端子間抵抗が、第1の抵抗素子(R12)の温度特性と逆極性の負の温度特性を示す領域を含む。

(もっと読む)

省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

半導体装置

【課題】プルアップ又はプルダウンのための専用端子を設けず、ソフトウェアによる初期化を待たずにプルアップ又はプルダウンの有無を設定する。

【解決手段】複数の端子を有する半導体装置であって、複数の端子を任意の数の端子毎に任意の数のグループにそれぞれ区分する第一の区分手段と、区分されたグループのそれぞれに含まれる任意の数の端子を、マスタ端子とスレーブ端子とに区分する第二の区分手段と、マスタ端子に対して論理レベルの設定を行う論理レベル設定手段と、マスタ端子に設定された論理レベルに応じて、スレーブ端子をプルアップ状態又は開放状態に切り替える切り替え手段と、を含む。

(もっと読む)

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

LVDS出力回路

【課題】 1個の基準電圧源を用いて、中間電圧(コモン電圧)及び出力振幅について温度特性がフラットになり、搭載されるICチップの面積増大を防ぐことが出来るLVDS出力回路を提供する。

【解決手段】 中間電圧(コモン電圧)作成用の基準電圧はバンドギャップリファレンス回路1の演算増幅器5の出力部から引き出し、振幅を決める定電流回路の基準電圧はバンドギャップ電圧を作る際に使用する抵抗R41、R42の節点14(中間タップ)から引き出す。そして、引き出し部分は電流検出用抵抗R6の温度特性に合わせる。検出用抵抗の温度特性と中間タップの位置での温度特性を合わせることにより、定電流回路3全体としての温度変化を無くすようにする。このようにして、1つのバンドギャップリファレンス回路1を用いて温度変化無しにLVDS出力回路を駆動できる。

(もっと読む)

出力回路および出力制御システム

【課題】回路面積の縮小を図りつつ、待機電流をカットオフすることが可能な出力回路を提供する。

【解決手段】出力回路は、第1の電源にソースが接続された出力pMOSトランジスタを備える。出力回路は、第1の出力pMOSトランジスタのドレインと接地との間に接続された出力nMOSトランジスタを備える。出力回路は、出力pMOSトランジスタのドレインと前記出力nMOSトランジスタのドレインとの間に接続された出力端子を備える。出力回路は、前記出力pMOSトランジスタのオン/オフを制御するための第1のゲート制御信号を第1のゲート制御端子から出力する第1のレベルシフタ回路を備える。出力回路は、前記出力nMOSトランジスタのオン/オフを制御するための第2のゲート制御信号を第2のゲート制御端子から出力する第2のレベルシフタ回路と、を備える。

(もっと読む)

レベル変換回路及び半導体装置

【課題】低面積化を図ること。

【解決手段】各信号BDT1〜BDTmをレベルシフトする回路として、クロックトレベルシフト回路(CLS回路)36(361〜36m)を用いた。CLS回路361は、ダイナミックコンパレータ回路(DC回路)411と、ラッチ回路421とを備える。DC回路411は、Lレベルのクロック信号ACKに応答してリセット状態となり、Lレベルの信号CDTm,XCDTmを出力する。また、CLS回路361は、Hレベルのクロック信号ACKに応答して比較状態となり、H1レベルの信号BDTm,XBDTmをH2レベルの信号CDTm,XCDTmにレベル変換する。ラッチ回路421は、相補な信号CDTm、XCDTmに応じた信号ADTm,XADTmを出力し、Lレベルの信号CDTm,XCDTmに応答して出力レベルを保持する。

(もっと読む)

ドライバアンプ回路および通信システム

【課題】バイアス調整回路やプリドライバ回路が不要で、しかも出力波形の波形歪みを低減することが可能なドライバアンプ回路および通信システムを提供する。

【解決手段】スイッチングトランジスタM11〜M14を駆動するゲート電圧を均一にするため、スイッチングトランジスタM11〜M14を電源およびGND側に配置し、さらに、スイッチングトランジスタM11〜M14の駆動振幅を安定させるために、各スイッチングトランジスタM11のドレインと出力ノードND11、ND12間にそれぞれ第1から第4の抵抗素子R11〜R14を接続している。

(もっと読む)

半導体集積装置

【課題】高速インターフェースのAC特性を測定する場合において、簡単な回路構成で信号種による差動入力回路での遅延時間差の発生をなくして、安価で低速なLSI検査装置で測定を行うことができる半導体集積装置を提供する。

【解決手段】第1、第2の差動入力回路13、20を含むデータ入出力を行う高速インターフェース回路を備えた半導体集積装置において、第1、第2の差動入力回路13、20の一方の入力側にデータ入力又は基準電圧のいずれか一方を選択入力するための選択器22を有し、AC特性を測定するテストモード時は、選択器22による入力選択により第1、第2の差動入力回路13、20の一方の入力側へ基準電圧を入力し、第1、第2の差動入力回路の他方の入力側へ高速インターフェース回路からの出力データを入力する。

(もっと読む)

二段電圧レベルシフト

【課題】追加の大きなハードウェア要件なしに、ブースト電圧レベルを提供できるようにする。

【解決手段】第1の電圧レベルから第2の電圧レベルに、次に追加のブーストされた第2の電圧レベルに出力信号をシフトするための電圧レベルシフタが開示される。電圧レベルシフタは、入力信号を受信するための入力、出力信号を出力するための出力、前記第1の電圧レベルを供給する第1の電圧源に接続するための第1のパワーサプライ入力、前記第2の電圧レベルを供給する第2の電圧源に接続するための第2のパワーサプライ入力、前記ブーストされた第2の電圧レベルを供給する第3の電圧源に接続するための第3のパワーサプライ入力を含み、前記電圧レベルシフタは、前記出力から前記第1のパワーサプライ入力を隔離するため、及び前記出力に前記第2のパワーサプライ入力を接続するために前記入力信号の所定の変化に応える。

(もっと読む)

容量性結合を用いる低電圧から高電圧へのレベル変換

【課題】高電圧出力トランジスタまたは回路のゲートを駆動するのに必要な電圧に達することができる。

【解決手段】電圧レベル変換回路は、デジタル論理回路と、第1および第2接続部を有するキャパシタであって、第1および第2接続部のうちの一方がデジタル論理信号へ電気的に結合された、少なくとも1つの高電圧キャパシタと、インバータ対であって、インバータ対のうちの少なくとも1つのインバータの出力が、少なくとも1つの高電圧キャパシタの他方の接続部へ電気的に結合された、たすき掛け結合型インバータ対とを備える。高電圧駆動回路は、2つの低電圧入力信号と、2つの信号であって、第1信号が高位側駆動信号であり、第2信号が低位側駆動信号である、2つの高電圧出力信号と、2つのレベル変換部であって、第1レベル変換部が高位側駆動信号に対応し、第2レベル変換部が低位側駆動信号に対応する。

(もっと読む)

レベル変換回路及び電子機器

【課題】小型かつ低消費電力を実現したレベル変換回路及び電子機器を提供する。

【解決手段】センサーデバイス3は、ソースからドレインに電流を流すNMOSトランジスタMN1が接続されるとともに、デジタル信号Sig1がドレインに入力され、デジタル信号Sig2がソースから出力されるPMOSトランジスタMP1を有しており、センサーデバイス3は、デジタル信号Sig1がローレベルからハイレベルに変化した場合、PMOSトランジスタMP1をONすることによって、デジタル信号Sig2をハイレベルにし、デジタル信号Sig1がハイレベルからローレベルに変化した場合、PMOSトランジスタMP1をOFFするとともにNMOSトランジスタMN1に電流を流すことによって、デジタル信号Sig2をローレベルにする。

(もっと読む)

回路装置、電子機器及び電源回路

【課題】実装面積を削減できる回路装置、電子機器及び電源回路等を提供すること。

【解決手段】回路装置は、共振回路を有する電源回路と、論理回路と、を含む。共振回路は、第1のコイルL1と、第1のコイルL1とコア部を共有する第2のコイルL2と、を有する。論理回路は、共振回路により生成された電源電圧VP、VMが供給されることで断熱的回路動作を行う。

(もっと読む)

入出力端子制御回路

【課題】フローティングかどうかの識別信号が不要な入出力端子制御回路を提供する。

【解決手段】フローティング検出回路51は、半導体チップの内部回路に対し外部信号を入出力する入出力端子Tに接続され、当該入出力端子Tの電気的なフローティング状態を検出する。電位固定スイッチSWは、フローティング検出回路51の検出結果に基づいて、当該入出力端子Tをハイレベルまたはローレベルの電源電圧で電位固定する。

(もっと読む)

OFDM方式モデム

【課題】OFDM方式モデムにおいて、受信信号の最大値以上の電圧を発生する高電圧生成回路を設けることなく受信スイッチの動作の信頼性を確保できるようにする。

【解決手段】制御部2が変調および復調を行い回線接続部4を介して通信の回線10に接続されるOFDM方式モデムにおいて、受信通信路11に設けられ子機の受信インピーダンスを親機に対して子機を複数台接続したときの通信性能の低下を抑える高インピーダンスとする高インピーダンス受信部20、および受信通信路の開閉を行うフォトモスリレー21,211,212を備え、前記高インピーダンス受信部が前記フォトモスリレーの出力回路のMOS FETにながれる電流を許容電流以下とし、前記制御部が前記フォトモスリレーを開閉制御する。

(もっと読む)

ディプレッション型FET用バイアス印加回路

【課題】単電源駆動の構成において常に所望のバイアス条件が得られると共に、生産性の向上、コストの低減を図ることができるようにする。

【解決手段】N−chディプレッション型FET1を単一の正電源3で駆動する構成において、FET1のソースと接地との間に、ソース電圧を制御するための第1(NPN)トランジスタQ1 が接続され、この第1トランジスタQ1 のベースには、このベースにFET1のドレイン電流の大きさに応じた調整用電流を供給するための第2(PNP)トランジスタQ2 が接続される。また、FET1のドレインと正電源3との間に、ドレイン電流検出用の抵抗R3が接続され、上記第1トランジスタQ1 によりFET1のソース電圧を制御することで、FET1のドレイン電流が常に一定となるように自動調整を行う。

(もっと読む)

レベルシフト回路

【課題】変換する電位差が大きくても、小規模な回路で、高速に、低電圧から高電圧へ信号レベルを変換することのできるレベルシフト回路を提供する。

【解決手段】低電圧電源電圧VDDLで動作する低電圧部100からは、入力信号Sinと同相の同相信号Sおよび逆相の逆相信号SNが出力され、能動バイアス制御部1は、入力された逆相信号SNの信号レベルに応じて、出力するバイアス信号VMの電位を、高電圧電源電圧VDDHに近い電位、または接地電位GNDに近い電位に、能動的に制御し、出力部2は、高電圧電源線VDDHと反転出力端VQとの間の導通が同相信号Sおよびバイアス信号VMにより制御され、接地電位電源線GNDと反転出力端VQとの間の導通が同相信号Sにより制御され、反転出力端VQの信号の極性がインバータINV1により反転される。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】低コストで実現でき、小型化、低消費電力化及び高周波化に資するとともに、フリップフロップ回路の誤動作を防止するレベルシフト回路及びレベルシフト回路を用いたスイッチング電源装置を提供する。

【解決手段】それぞれ一端がレベルシフト電源に接続された抵抗R1、R2と、抵抗R1の他端にドレインが接続されたトランジスタMN3と、抵抗R2の他端にドレインが接続されたトランジスタMN4と、入力信号に基づいてトランジスタMN3,MN4のオン/オフを制御するパルス発生回路10と、トランジスタMN3がオンである場合にセット信号、トランジスタMN4がオンである場合にリセット信号を生成する制御部と、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12とを備える。

(もっと読む)

レベルシフト出力回路

【課題】レベルシフタによる面積の増加や電力の増加がなく、高耐圧P型FETの電流能力を分散させるレベルシフト出力回路を提供すること。

【解決手段】レベルシフタ40は、電源NVDD3と電源NGND間に接続され、入力信号Sin1“L”に応じて出力信号“L”を出力し、入力信号Sin2“H”に応じて出力信号“H”を出力する。高圧インバータ50−1〜50−zは、電源NVDD3と電源NGND間に接続され、制御信号Sctr1“L”とレベルシフタ40からの出力信号“L”とに応じて出力信号“H”を出力し、制御信号Sctr2“H”とレベルシフタ40からの出力信号“H”とに応じて出力信号“L”を出力する。高耐圧P型FET60−1〜60−zは、電源NVDD3と電源出力ノードNVDD2間に接続され、それぞれ、高圧インバータ50−1〜50−zからの出力信号“L”に応じて電圧VDD3を供給する。

(もっと読む)

1 - 20 / 108

[ Back to top ]