Fターム[5J056BB52]の内容

Fターム[5J056BB52]に分類される特許

1 - 20 / 51

信号送信回路

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

論理回路及びデータ処理システム

【課題】素子数が少なく、遅延が小さく、ドライバ能力を有するXORゲート回路を提供する。

【解決手段】論理回路1は、電源電位VPERIとノードn1の間に接続されたトランジスタT1と、電源電位VPERIとノードn2の間に接続されたトランジスタT2と、電源電位VSSとノードn3の間に接続されたトランジスタT3と、電源電位VSSとノードn4の間に接続されたトランジスタT4と、ノードn1とノードn3の間に直列接続されたトランジスタT5,T7と、ノードn1とノードn3の間に直列接続されたトランジスタT9,T11と、ノードn2とノードn4の間に直列接続されたトランジスタT6,T8と、ノードn2とノードn4の間に直列接続されたトランジスタT10,T12とを備える。出力信号Yは、トランジスタT5,T7の接続点及びトランジスタT6,T8の接続点から取り出される。

(もっと読む)

半導体集積回路

【課題】記憶装置の消費電力を低減すること、記憶装置の面積を低減すること、記憶装置を構成するトランジスタの数を低減する。

【解決手段】第1の出力信号及び第2の出力信号の電位を比較する比較器と、第1の酸化物半導体トランジスタ及び第1のシリコントランジスタを有する第1のメモリ部と、第2の酸化物半導体トランジスタ及び第2のシリコントランジスタを有する第2のメモリ部と、当該第1の出力信号及び当該第2の出力信号の電位を確定する出力電位確定器とを有し、当該第1の酸化物半導体トランジスタのソース又はドレインの一方は、当該第1のシリコントランジスタのゲートに電気的に接続されており、当該第2の酸化物半導体トランジスタのソース又はドレインの一方は、当該第2のシリコントランジスタのゲートに電気的に接続されている記憶装置に関する。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置

【課題】電源制御領域を電源遮断状態から電源供給状態に切り換えた際に生じる突入電流と電源ノイズを低減した半導体装置を提供する。

【解決手段】第1、第2のスイッチセルSWa、SWbと、を有し、第1のスイッチセルSWaは、制御信号CNTに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第1のスイッチトランジスタ11と、制御信号CNTを伝達する第1の信号伝達部と、を有し、第2のスイッチセルSWbは、制御信号CNTの論理レベルに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第2のスイッチトランジスタ21と、ローカル電源配線LVDDの電圧値が閾値電圧に達するまでの期間、制御信号CNTの後段回路への伝達を遮断する第2の信号伝達部と、を有する。

(もっと読む)

半導体集積回路の出力バッファ回路、及び半導体集積回路

【課題】半導体集積回路の出力バッファ回路において電流の流れ込みを防止し、動作を高速化し、回路規模を削減する。

【解決手段】出力バッファ回路11は、常時オンの電源VDD、オン/オフ制御される電源VDD1、電源VDD1の電位を反転した反転信号INVOUTを出力するインバータ回路41、トランジスタP1A1,PP2,PP3、トランジスタP1A1を制御するドライブ回路51を備える。トランジスタP1A1は、入出力端子E1Aに接続されたドレイン、電源VDD1に接続されたソース、電源VDDに接続されたバックゲート、ドライブ回路51に接続されたゲートを有する。トランジスタPP2,PP3のバックゲート及びトランジスタPP2のソースは電源VDDに接続され、トランジスタPP2のゲート及びトランジスタPP3のソースは電源VDD1に接続され、トランジスタPP3のゲートには反転信号INVOUTが入力される。

(もっと読む)

送信回路

【課題】従来の送信回路に対して、補正回路の不要、要素回路占有面積の低減の2点において有利であり、出力レベルのHigh側とLow側でエンファシス量のアンバランスを解消することができる送信回路を提供する。

【解決手段】送信回路において、ドライバ回路17は、送信データ信号の電圧値により制御される差動信号入力用のMOSトランジスタM1p,M1nにカスコード接続され、バイアス電圧の電圧値により制御され、駆動電流を流すバイアス電圧印加用のMOSトランジスタM3p,M3nを有し、ドライバ回路16,18は、送信データ信号を遅延した信号の電圧値により制御される差動信号入力用のMOSトランジスタM1p,M1nにカスコード接続されて負荷部に接続され、バイアス電圧の電圧値により制御され、駆動電流を流すバイアス電圧印加用のMOSトランジスタM3p,M3nを有する。

(もっと読む)

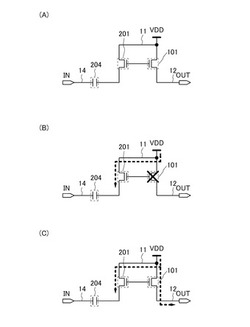

反転電圧出力回路

【課題】入力信号の変化に応じて直流電源の非接地電圧と接地電圧の間で反転する電圧を出力する回路であり、非接地端子に接続されている電源線に生じる電圧変動を抑制する。

【解決手段】電流制限素子14とスイッチング回路16が直列に接続されており、電流制限素子とスイッチング回路の中間点22の電圧を出力する。スイッチング回路の導通時にスイッチング回路を流れる電流が電流制限素子によって制限される。直流電源の非接地端子に接続されている電源線12に生じる電圧変動が抑制され、電源線12に接続されているアナログ回路等の動作が安定する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】伝送線路の特性インピーダンスと終端抵抗のインピーダンス整合を容易とする。

【解決手段】差動終端抵抗回路3は直列の第1と第2の素子Q1、Q2を含み、レプリカ抵抗回路4は直列の第3と第4の素子Q3、Q4を含み、制御電圧生成回路5は制御差動増幅器DA2と直列の制御素子Q8と第1と第2の電圧降下回路R7、8;R9とを含む。増幅器DA2の非反転入力と反転入力に、基準電圧Vrefと回路4の素子Q3、Q4のレプリカ抵抗電圧Vrcmがそれぞれ供給される。回路5の第1と第2のレプリカ抵抗制御電圧Vcont0、1は、回路4の素子Q3、Q4の制御入力にそれぞれ供給される。差動終端抵抗回路3の素子Q1、Q2は、第2のレプリカ抵抗制御電圧Vcont1と第2の電圧降下回路R9の電圧降下との合計電圧である差動終端抵抗制御電圧Vcont1.5に基づく制御出力電圧Voutによって制御される。

(もっと読む)

半導体集積回路およびその動作方法

【課題】多ビットの差動受信回路および差動終端抵抗を内蔵して、半導体チップ面積と消費電流の増大を軽減する。

【解決手段】複数の差動受信回路2A、B〜Nと複数の差動終端抵抗回路3A、B〜Nと複数の制御電圧供給回路6A、B〜Nに、レプリカ抵抗回路4と制御電圧生成回路5が共用される。複数の回路6A、B〜Nの各回路は、第1非反転入力と第1反転入力と出力を有する差動増幅器DA1を含む。第1供給回路6Aの第1差動増幅器の第1非反転入力と、第2供給回路6Bの第2差動増幅器の第1非反転入力と、第N供給回路6Nの第N差動増幅器の第1非反転入力とに、生成回路5から生成される差動終端抵抗制御電圧Vcont1.5が共通に供給される。第1差動増幅器の出力電圧VoutAと第2差動増幅器の力電圧VoutBと第N差動増幅器の出力電圧VoutNとは、第1と第2と第Nの差動終端抵抗回路3A、3B、3Nにそれぞれ供給される。

(もっと読む)

出力回路

【課題】入力信号が電源電圧の半分程度である場合に、低耐圧のトランジスタを用いながら高電圧の信号を出力する回路を提供する。

【解決手段】入力信号が電源電圧の半分程度である場合には、図1に示すような第3の第1導電型トランジスタを備える出力回路を考える。図1において、入力信号が電源電圧の半分程度まで上昇すると、第1及び第2の第2導電型トランジスタはオン状態になる。すると、出力信号は0Vに向かって低下を始める。その際に、出力信号の低下に伴って第3の第1導電型トランジスタがオン状態になり、第2の第1導電型トランジスタをオフすることができる。その結果、出力信号に対する電源電圧の影響を排除し、ロウレベルとして0Vを出力する出力回路が提供される。

(もっと読む)

レベルシフト回路

【課題】 簡単な回路構成にて、3.3Vのハイレベルと0Vローレベルとを有する第1制御信号を、5Vのハイレベルと0Vのローレベルとを有する第2制御信号に変換して出力する。

【解決手段】 レベルシフト回路1は、抵抗R1と、ダイオードD1と、コンデンサC1、C2と、トランジスタQ1〜Q4とを備える。レベルシフト回路1は、マイコンからの第1制御信号がローレベルのときにコンデンサC1、C2を、+3.3V電源電圧によって別個に充電させ、かつ、ローレベルの第2制御信号を出力する。レベルシフト回路1は、第1制御信号がハイレベルのときにコンデンサC1、C2の充電電圧を加算した値のハイレベルの第2制御信号を出力する。

(もっと読む)

半導体集積回路

【課題】低消費電力で動作し、かつ、端子数を減らすことが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第1の回路と、第2の回路と、信号伝播制御回路と、を備える。第2の回路は、前記第1の回路の電源端子とは独立の電源端子を有する。信号伝播制御回路は、前記第2の回路に電源が投入されてから所定期間、所定の固定値を前記第2の回路へ入力し、前記所定期間経過後、前記第1の回路からの出力信号および前記所定の固定値のいずれを前記第2の回路へ入力するかを制御する。

(もっと読む)

クロック負昇圧回路

【課題】回路構成が簡易、小型でウェル・バイアス電圧の立ち上がり時間が短く、安定した負昇圧クロックを供給することが可能なクロック負昇圧回路を提供する。

【解決手段】クロック負昇圧回路部301、クロック負昇圧回路部302、クロック負昇圧回路部301、クロック負昇圧回路部302のウェル層上に設けられたNMOSトランジスタ107に電圧を供給するキャパシタ403、NMOSトランジスタ104を備え、クロック負昇圧回路部301が備えるNMOSトランジスタ104とキャパシタ403とを接続する電圧ライン303、クロック負昇圧回路部302が備える2つのNMOSトランジスタ104の出力を接続する電圧ライン303によってクロック負昇圧回路を提供する。

(もっと読む)

入出力回路及びシステム

【課題】 1つの入出力回路により差動信号またはシングルエンド信号を伝達することで、回路規模を削減する。

【解決手段】 入出力回路は、一端が第1の基準電位に結合される第1の負荷と、第1の負荷の他端にドレイン端が結合された第1のMOSトランジスタと、一端が第1の基準電位に結合される第2の負荷と、第2の負荷の他端にドレイン端が結合された第2のMOSトランジスタと、第1のMOSトランジスタのソース端及び第2のMOSトランジスタのソース端との間にソース端またはドレイン端が接続された第3のMOSトランジスタと、第1のMOSトランジスタのソース端と第2の基準電位との間に結合される第1の定電流源と、第2のMOSトランジスタのソース端と第2の基準電位との間に結合される第2の定電流源とを有する。

(もっと読む)

ダイナミック回路の初期化方法

【課題】ダイナミック回路において、評価制御トランジスタを省略してトランジスタのスタック段数を削減するとともに評価制御トランジスタの省略に伴う初期化動作時の貫通電流の発生を抑制する。

【解決手段】ダイナミック回路の初期化方法は、所定の条件でダイナミックノードの初期化を開始するステップと、複数の入力信号の少なくとも一部について論理評価を行うステップと、論理評価の結果が真のとき、ダイナミックノードの初期化を停止するステップとを備えている。

(もっと読む)

レベルコンバータ回路を備えたMOSトランジスタ回路

【課題】動作上の欠点を除去し、また、用いるトランジスタ数が少ない静的動作のレベルコンバータ回路を備えたMOSトランジスタ回路を提供する。

【解決手段】高電源電圧回路側の第一のCMOSインバータの遷移領域TRHが、低電源電圧回路側の第二のCMOSインバータの出力論理信号の変化範囲に含まれるように前記第一のCMOSインバータと前記第二のCMOSインバータの動作を設定し、第一のCMOSインバータをレベル変換回路とし、第一のCMOSインバータを第二のCMOSインバータの出力で駆動するように構成する。

(もっと読む)

パストランジスタを用いた論理回路、セレクター回路、多入力ルックアップテーブル回路または多入力マルチプレクサー回路、および集積回路

【課題】パストランジスタを流れる漏洩電流の削減、また入力数の増加に対するトランジスタ数の増加の割合が小さいパストランジスタを用いた論理回路、および集積回路を提供する。

【解決手段】低電源電圧回路の低論理信号振幅の第一の論理信号がドレインに印加され、ゲートに第二の論理信号で制御するパストランジスタMN1を用いた論理回路であって、低電源電圧回路の低論理信号振幅の第三の論理信号を入力ノードに印加して高電源電圧で動作する第一のCMOSインバータINVH1を有し、第三の論理信号の電圧変化範囲が高電源電圧の高電源電位と低電源電位に挟まれ、かつINVH1の遷移領域を含むように高電源電圧の高電源電位と低電源電位が設定され、かつ高電源電圧の高電源電位と低電源電圧回路の高電源電位との差がパストランジスタのしきい値電圧よりも大きく設定されたINVH1の出力信号を第二の論理信号とする。

(もっと読む)

バス絶縁型PLC

【課題】フォトカプラ等の絶縁素子の必要数を大幅に削減可能として上記実装装置の規模の小型化とコストの大幅な削減化を可能とすること。

【解決手段】CPU2と、CPUとの間で信号の入力伝送および出力伝送の少なくとも一方の伝送をする複数の入/出力回路6,7と、CPUからの信号はシリアル/パラレル変換し、入/出力回路からの信号はパラレル/シリアル変換するバスI/F3a,3bと、CPUとバスI/Fとの間に配されて信号をシリアル伝送する信号伝送バス8a,8bと、バスI/Fと各入/出力回路との間に配されて信号をパラレル伝送する信号伝送バス9a,9b,10a,10bと、を備え、シリアル信号伝送バス8a,8b内に、絶縁回路部20a,20bを設けた構成。

(もっと読む)

1 - 20 / 51

[ Back to top ]