Fターム[5J056BB21]の内容

Fターム[5J056BB21]の下位に属するFターム

雑音発生の防止 (225)

使用環境に対するもの (89)

雑音入力による誤動作防止 (130)

入力しきい値の安定化、変動の防止 (29)

製造時のばらつきの補償 (127)

経年変化の補償 (28)

電源変動対策 (145)

保護 (187)

リーク対策 (223)

電荷再分配の対策 (3)

Fターム[5J056BB21]に分類される特許

1 - 20 / 170

半導体集積回路

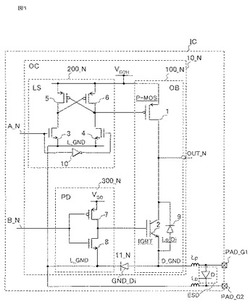

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

半導体装置

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及

びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジ

スタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャ

ネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタ

のW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは

、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトラン

ジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス

信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

集積回路及び集積回路の制御方法

【課題】回路若しくは装置が、仕様或いは規格に適用しない部分があったとしても、使用することに問題がない場合の対応方法のひとつを提供する。

【解決手段】集積回路が入出力回路とタイミング測定回路とを含み、前記入出力回路の第1の入力端子に入力される第1の信号と、前記入出力回路の第1の出力端子から出力される第2の信号とが前記タイミング測定回路に入力され、前記第2の信号は、前記入出力回路の第1の入出力端子における信号が前記第1の出力端子から出力されたものであり、前記タイミング測定回路において、前記第1の信号における第1の変化を検出し、前記第2の信号における前記第1の変化に対応する第2の変化を検出し、前記第1の変化を検出したときと前記第2の変化を検出したときとの間の時間間隔の計測を行うことを特徴とする。

(もっと読む)

レベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置

【課題】向上された信頼性を有するレベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置が提供される。

【解決手段】本発明のレベル変換器は、入力ノードを通じて受信される第1電圧ドメインの入力クロックに応じて第2電圧ドメインの出力クロックを発生する第1及び第2電圧変換回路を含み、第1及び第2電圧変換回路は同一の構造を有し、入力ノード及び出力ノードの間に並列に連結される。

(もっと読む)

論理否定型電子回路

【課題】 ブートストラップ機能を有する電子回路に関し、出力電圧の降下を防止して、論理否定型電子回路の誤作動を阻止し、また、長い作動時間を確保する。

【解決手段】 負荷トランジスタ、駆動トランジスタ部、充電用トランジスタ並びにブートストラップ容量を具備し、入力電圧の位相を出力部から反転せしめて出力する論理否定型電子回路について、入力される電圧の位相を反転させて出力するインバータ回路をさらに設け、このインバータ回路の入力節点を前記出力部に、出力節点を前記充電用トランジスタのゲートにそれぞれ接続する。

(もっと読む)

レベルシフト回路

【課題】低電圧側の電源が遮断された時にレベルシフト回路を電源電圧と切り離すことなくロウレベルまたはハイレベルに出力を固定する。

【解決手段】レベルシフト回路にはレベルシフタ11と、イネーブル回路12とが設けられている。レベルシフタ11は、低電圧入力を高電圧出力に変換する。イネーブル回路12は、低電圧入力の代わりにイネーブル信号Bをレベルシフタ11に入力し、レベルシフタ11の出力信号Zをロウレベルまたはハイレベルに固定する。

(もっと読む)

信号変換装置、波形測定装置および半導体試験装置

【課題】シングルエンド信号および差動信号を入力してシングルエンド信号を出力するときに、広帯域でノイズや歪みが少ない高品質なシングルエンド信号を出力することを目的とする。

【解決手段】信号変換装置3にパルストランス12を用い、シングルエンド信号を入力したときには、パルストランス12の1次入力側と2次入力側とのうちシングルエンド信号を入力した入力側および1次出力側と2次出力側とのうち何れか一方の出力側をパルストランス12に接続し、差動信号を入力したときには、1次入力側および2次入力側との両方の入力側および1次出力側と2次出力側とのうち何れか一方の出力側をパルストランス12に接続する制御を行っている。

(もっと読む)

デューティ比自動調整コンパレータ回路

【課題】電源電圧などの回路の動作条件の変動に関わらず、デューティ比の変動を抑圧、低減する。

【解決手段】差動増幅回路1と、この差動増幅回路1において差動対を構成する2つのMOSトランジスタ21,22のソース同士の接続点における電位に基づいて閾値電圧を生成する閾値電圧生成回路2と、インバータ動作における閾値電圧を、閾値電圧生成回路2により生成された閾値電圧に設定可能に構成された閾値電圧可変インバータ回路3とが設けられることにより、インバータ動作における閾値電圧が、差動増幅回路1の出力振幅の中心電圧に設定でき、電源電圧の変動などが生じてもインバータの入出力間におけるデューティ比の変動が抑圧、低減できるものとなっている。

(もっと読む)

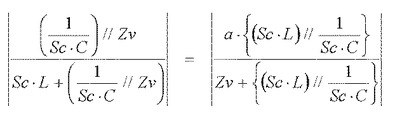

スイッチング回路のノイズ低減装置

【課題】ノイズ低減効果が大きく、小型化が可能なスイッチング回路のノイズ低減装置を提供する。

【解決手段】第1のスイッチングドライバの入力端に入力されるパルス信号と逆位相のパルス信号に基づいて動作する第2のスイッチングドライバと、一端が第2のスイッチングドライバの出力端に接続されるとともに他端がスイッチング回路の出力端子と接続されるインピーダンス素子とを具備し、インピーダンス素子のインピーダンス値Zvと、第1のコイルのインダクタンス値Lと、コンデンサの静電容量値Cと、第1及び第2のスイッチングドライバのスイッチング周波数fcとが、aを0以外の任意の定数として、(数3)の関係を満たす。 (もっと読む)

(もっと読む)

電子回路

【課題】

内部電源電圧を遮断するパワーダウンモードへの移行を誤動作無く確実に実行するパワーダウンモードの移行シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧から降圧してシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する第1の内部回路30と、電源電圧を供給されて動作する入出力回路24と、第1の内部回路30からの信号を入力し、電源電圧の電圧レベルに変換するレベルシフタ23と、システム電圧発生回路10を制御する制御回路40とを備え、制御回路40は起動信号P4を入力し、この起動信号に所定の遅延時間を与えた短絡制御信号P5を出力する遅延回路100を有し、起動信号はレベルシフタ23を非活性又は活性として制御し、短絡制御信号はシステム電圧発生回路10を停止状態又は動作状態として制御する構成とした。

(もっと読む)

半導体装置およびフリップフロップの制御方法

【課題】リテンション機能を備えるフリップフロップにデータを保持する際に意図しないデータのラッチが発生することを抑制することである。

【解決手段】本発明にかかる半導体装置は、フリップフロップRFF2と、フリップフロップRFF2に供給されるクロック信号を制御するクロック制御回路3と、フリップフロップRFF2にデータ保持信号を供給すると共に、クロック制御回路3を制御するコントローラ2とを備える。フリップフロップRFF2がクロック信号のネガティブエッジで駆動し、かつクロック信号がハイレベルの時にデータを保持する場合、コントローラ2は入力クロック信号を固定した後、フリップフロップRFF2がデータを保持する前に、フリップフロップRFF2にハイレベルのクロック信号が供給されるようにクロック制御回路3を制御する。

(もっと読む)

デジタル信号入力装置

【課題】動作が安定するとともに、後段に接続されるCMOSのLSIの安定な動作を実現するデジタル信号入力装置を提供する。

【解決手段】外部から入力された信号を増幅する増幅部と、前記増幅部で増幅された信号を波形整形する波形整形部と、オフセット電圧を保持するコンデンサと、前記波形整形部の出力をハイレベル状態に固定するように、前記コンデンサの充電と放電を制御して前記オフセット電圧を決定する制御部とを備える。

(もっと読む)

半導体集積回路

【課題】被監視回路の動作を監視し故障している可能性がある場合にアラーム信号を出力する構成とする場合に、監視機能の喪失を招来する共通原因故障が発生しにくい監視回路を備えた半導体集積回路を提供すること。

【解決手段】処理経路に少なくとも1つ以上のフリップフロップ回路が存在する被監視回路と、処理経路に前記被監視回路のフリップフロップ回路に対応するフリップフロップ回路を有し、前記被監視回路の動作を模擬する模擬回路、および前記被監視回路の出力と前記模擬回路の出力とを比較し、比較結果に基づきアラーム信号を出力する比較回路を有する監視回路とを備え、前記被監視回路および前記模擬回路において互いに対応する前記各フリップフロップ回路は、同一のタイミングで動作するとともに、互いに論理を反転した信号をそれぞれ対応する後続回路へ出力するように制御されることを特徴とする。

(もっと読む)

レベル変換回路及びバッテリ装置

【課題】基準電位の異なるTTLレベルの信号をCMOSレベルの信号へ正しく変換が行えるレベル変換回路及びバッテリ装置を提供する。

【解決手段】第1電源と第3電源の間に設けられTTLレベルの信号を入力し第1電源の電圧または第3電源の電圧に反転して出力する反転回路を備えた入力部と、第1電源と第3電源の間に設けられ入力部の出力信号を反転して出力するインバータ回路と、第1電源と第2電源の間に設けられ入力部の出力信号とインバータ回路の出力信号を入力しインバータ回路の出力信号をCMOSレベルの信号に反転して出力するレベル変換部と、を備え、入力部の反転回路は直列に接続したPMOSトランジスタと電流リミット回路とNMOSトランジスタを備えた。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

レベル変換回路

【課題】第1及び第2入力信号の電圧レベルが変化する範囲に拘わらず、常時、適切なレベルで振幅する出力信号を出力することが可能なレベル変換回路を提供する。

【解決手段】N型トランジスタ21、22を入力差動対として有し、外部から入力される第1及び第2入力信号IN1、IN2をN型トランジスタ21、22のゲートに受ける第1差動増幅部2と、P型トランジスタ31、32を入力差動対として有し、第1及び第2入力信号IN1、IN2をP型トランジスタ31、32のゲートに受ける第2差動増幅部3と、第1及び第2入力信号IN1、IN2の電圧レベルを所定の基準電位VREFと比較し、各々の電圧レベルが基準電位VREFよりも高いか否かを判定する入力判定部4と、入力判定部4の判定結果に応じて第1及び第2差動増幅部2、3のいずれか一方の出力を選択する出力選択部5とを備えたレベル変換回路1。

(もっと読む)

出力ドライバ回路

【課題】通信速度の高速化に加えて、消費電力の低減や、あるいは伝送波形品質の向上が図れる出力ドライバ回路を提供する。

【解決手段】例えば、正極および負極出力ノード(TXP,TXN)を電圧で駆動する電圧信号生成回路ブロックVSG_BKと、データ入力信号DIN_P,DIN_Nの遷移を受けてパルス信号を生成するパルス信号生成回路PGEN1,PGEN2と、当該パルス信号のパルス幅の期間でTXP,TXNを電流で駆動する電流信号生成回路ブロックISG_BKp1,ISG_BKn1を備える。電流信号生成回路ブロックは、TXP,TXNの寄生容量(Cp1,Cp2)を高速に充電すると共に、パルス幅に応じたプリエンファシスを行う。VSG_BKは、TXP,TXNにおける定常状態の電圧レベルを定めると共に、TXP,TXNをインピーダンスZ0で終端する。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

バッファ回路

【課題】出力の反射を抑制しつつスルーレートを高い自由度を持って調整可能なバッファ回路を提供する。

【解決手段】

複数の出力トランジスタPOA1〜POE1は、電源端子(電源電圧VCCQ)と出力端子DoutP1との間に電流経路を並列接続され導通することにより出力端子DoutP1の電圧を変化させる。ゲート制御用トランジスタTA1〜TE1は、接地端子Dgndと出力トランジスタPOA1〜POE1のゲートとの間、又は2つの出力トランジスタのゲートの間に電流経路を形成するように接続され、出力トランジスタにゲート電圧を与える。ゲート制御用トランジスタTA1〜TE1のゲートは、ゲート制御用トランジスタTA1〜TE1のソースの電圧が変化したときにゲート−ソース間の電位差が閾値電圧以上となって導通するよう、所定の電圧を与えられている。

(もっと読む)

1 - 20 / 170

[ Back to top ]