Fターム[5J056BB32]の内容

Fターム[5J056BB32]の下位に属するFターム

入力線からの雑音対策 (17)

出力線からの雑音対策 (18)

電源線からの雑音対策 (30)

空間からの雑音対策 (5)

Fターム[5J056BB32]に分類される特許

1 - 20 / 60

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、インバータ、第1パス制御回路、及び第2パス制御回路を備える。インバータの入力は第1ノードに接続される。ターゲット反転電位は、インバータの反転電位よりも高い。第1パス制御回路は、入力電位がターゲット反転電位より低い場合、入力端子と第1ノードとの間の電気的接続を遮断し、入力電位がターゲット反転電位より高い場合、入力端子と第1ノードとを電気的に接続する。第2パス制御回路は、入力電位がターゲット反転電位より低い第2反転電位より低い場合、グランド端子と第1ノードとを電気的に接続し、入力電位が第2反転電位より高い場合、グランド端子と第1ノードとの間の電気的接続を遮断する。

(もっと読む)

ブートストラップ回路

【課題】飛び込みの影響を軽減できるブートストラップ回路を提供する。

【解決手段】同一導電型の第1乃至第4TRから構成され、第1TRにおいて、一方のS/D領域は第2TRの一方のS/D領域に接続され、他方のS/D領域には、2相のクロックのうち一方のクロックが印加され、ゲート電極は、第3TRの一方のS/D領域に接続され、第2TRにおいて、他方のS/D領域は電圧供給線に接続され、第3TRにおいて、他方のS/D領域には入力信号が印加され、ゲート電極には他方のクロックが印加され、第1TRのゲート電極と第3TRの一方のS/D領域とは、第3TRがオフ状態になると浮遊状態となるノード部を構成し、第4TRにおいて、一方のS/D領域は、反転回路の入力側に接続されると共に、該反転回路の出力側と第2TRのゲート電極とが接続されており、他方のS/D領域は入力信号が印加され、ゲート電極には他方のクロックが印加される。

(もっと読む)

半導体回路

【課題】本発明は、ハイレベルの入力信号に混入されたローレベルのノイズ及びローレベルの入力信号に混入されたハイレベルのノイズをより効果よく取り除くことができる半導体回路を提供する。

【解決手段】 入力信号を所定時間遅延して出力する遅延部120、220、320と、該入力信号のレベルによって電圧を充放電させる電圧調整部140、240、340と、該入力信号のレベル及び遅延部120、220、320から出力される信号のレベルを用いて生成された信号によって、電圧調整部140、240、340の充放電動作を制御する組合せ部160、260、360とを含む。

(もっと読む)

電子回路

【課題】高い精度で所定の検査を行うことができる電子回路を提供する。

【解決手段】本実施の形態に係る電子回路1は、図1(a)に示すように、主に、主回路2への電圧Vccの供給を切り替えるスイッチ素子としてのp型トランジスタ3と、p型トランジスタ3を駆動する第1の駆動信号を出力する駆動部4と、入力側が駆動部4に電気的に接続され、出力側がp型トランジスタ3に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて第2の駆動信号を出力する第1のインバータ部5と、入力側が駆動部4に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて検査のための検査信号を出力する第2のインバータ部6と、第2のインバータ部6の出力側に電気的に接続され、検査信号を出力する第1のパッドとしての検査パッド7と、を備えて概略構成されている。

(もっと読む)

信号処理装置

【課題】従来よりもノイズに妨害されることなく入力信号から値を読み取る。

【解決手段】信号処理装置Aは、外部からデジタル信号dsを受信する入力端子1と、異なる複数のサンプリング周期を合わせてデジタル信号dsの値を読み取る入力信号読み取り部5とを具備する。

(もっと読む)

動作クロック生成装置及び処理装置

【課題】周波数の切換が可能な動作クロックを生成する動作クロック生成装置、及び、その動作クロック生成装置が生成する動作クロックによって動作する回路を複数備えた処理装置において、グリッジによって余分な動作クロックが出力されるのを抑制すること。

【解決手段】カウンタ7は、カウンタ値が所定数に設定された後、基準クロックPS0を1つ計数する毎に1つカウンタ値を減算し、カウンタ値が「0」になると、carry端子7dからHレベルのキャリー信号C−SEL(基準クロックPS0の1周期分)を出力する共に、前記カウンタ値を前記所定数にリセットする。また、前記所定数は、カウンタ7のval_max端子7cに切換値が入力されると、その値に変更される。クロックゲーティングセル9は、キャリー信号C−SELがHレベルのときに立ち上がった基準クロックPS0のみを、動作クロックBCLKとして出力する。

(もっと読む)

レベルシフト回路並びにレベルシフト回路を備えたインバータ装置

【課題】VM電位のdv/dtに起因する上アーム電力用スイッチング素子の誤動作を抑制できるレベルシフト回路並びにこれを備えたインバータ装置を提供する。

【解決手段】支持体Si基板上にBOX酸化膜を介しN型Si活性層を形成したSOI基板により構成し、分離酸化膜により分離されN型MOSFETを形成する第1のN型Si活性層、分離酸化膜により分離されP型拡散層による拡散抵抗を形成する第2のN型Si活性層、分離酸化膜により分離され上アーム制御電源の一端側に接続する第4のN型Si活性層から構成され、第1のN型Si活性層を形成する分離酸化膜と第4のN型Si活性層を形成する分離酸化膜は、隣接配置されるとともに、N型MOSFETのドレイン電極と拡散抵抗の第一の電極を接続し、拡散抵抗の第2の電極を上アーム制御電源の他端側に接続した。

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

プログラマブルデバイス回路

【課題】スイッチノードのデータ転送時間を極小として動作を高速化することができるプログラマブルデバイス回路を提供する。

【解決手段】二次元アレイ状に配置されている複数の回路ブロックに個々に接続されている複数のスイッチノード100が相互接続により二次元の可変自在な接続網を形成する。このスイッチノード100が、回路ブロックがデータ出力を実行しているときに並行してプリチャージ動作を実行するプリチャージロジック回路からなる。プリチャージロジック回路はプリチャージ動作に多分に時間を必要とすることでデータ転送時間を短縮できる。そのプリチャージ時間は回路ブロックのデータ出力時間と重複しているのでタイムロスとならない。

(もっと読む)

半導体集積回路

【課題】デジタル回路とアナログ回路とを混載して成る半導体集積回路において、前記デジタル回路によってメモリなどの外部負荷を駆動するにあたって、グランドバウンスによるアナログ回路への影響を抑えつつ、前記外部負荷がデジタル回路からの矩形波パルスを受信するにあたって、ON/OFF(「1」/「0」)判定のマージンを最大にする。

【解決手段】外部負荷3を駆動するメインドライバ回路7を、複数段のインバータINV1〜INV3を備える多段階電圧制御型のプリドライバ回路6を介して駆動するようにし、そのインバータINV1〜INV3の使用段数を切換え回路12で切換えられるようにする。そして、雑音検出回路13によって検出されるグランドバウンスのレベルが、小さいときにはインバータINV3のみを使用して前記矩形波パルスの鈍りを小さくし、大きいときにはインバータINV1〜INV3を使用して、グランドバウンスを抑える。

(もっと読む)

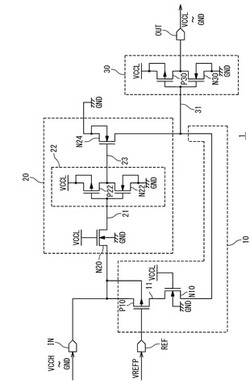

電圧範囲判断回路

【課題】電圧範囲判断回路を提供すること。

【解決手段】電圧範囲判断回路は対象電圧生成部、選択電圧生成部、比較電圧選択部及び出力信号生成部を含む。対象電圧生成部は、入力電圧に基づいて対象電圧を生成する。選択電圧生成部は、基準電圧に基づいて第1〜第2選択電圧を生成する。比較電圧選択部は、出力信号に基づいて、第1〜第2選択電圧の中で1つを選択して比較電圧に出力する。出力信号生成部は、対象電圧と比較電圧を比べて出力信号を生成する。電圧範囲判断回路は外部ノイズが流入する場合も入力電圧の電圧範囲を正確に判断することができる。

(もっと読む)

半導体回路

【課題】低消費電流でノイズ耐性に優れた高圧側パワートランジスタを駆動する回路を提供する。

【解決手段】低圧側入力信号(HIN)に従って短い期間活性状態となるワンショットパルス(ON_B)を生成するワンショット回路(11)を設ける。第1および第2の電流供給部(14,16)により、入力信号およびワンショットパルスの発生するワンショットパルス信号に従って内部ノード(15)に電流を供給する。第1の内部ノードを流れる電流をウイルソンカレントミラー回路(20)で受け、電流検出部(R3)により電圧信号に変換し、ゲートドライバ(DRV)により、スイッチングパワートランジスタの駆動信号を生成する。

(もっと読む)

車載通信装置

【課題】ネットワークの幹線や支線を含むワイヤハーネスの構成や配線の取り回しに関する自由度が高く、装置全体のコストの上昇を抑制可能な車載通信装置を提供する。

【解決手段】3以上の通信ノード及びこれらの間を接続する通信線路を備える車載通信装置であって一端に第1の通信ノード21が接続され他端に第2の通信ノード24が接続される幹線31と、第1の通信ノードに接続された第1の幹線終端抵抗51と、第2の通信ノードの位置に接続された第2の幹線終端抵抗52と、線路の長さが幹線31よりも短く規制され前記幹線の線路の中間部に一端が接続された支線35と、支線35の他端と接続され入力インピーダンスが第1の幹線終端抵抗51及び第2の幹線終端抵抗52よりも十分に大きい信号中継部30とを設けた。

(もっと読む)

入力回路および半導体集積回路

【課題】電磁波による誤動作を低減することのできる入力回路および半導体集積回路の提供を図る。

【解決手段】入力端子2に供給される入力信号を受け取る入力回路10aであって、一端が前記入力端子に接続された容量42と、前記入力信号を、当該入力信号と同じ正論理の信号に変換し、前記容量の他端に供給して駆動する容量駆動回路51,52,41と、を有するように構成する。

(もっと読む)

レベルシフト回路、スイッチング素子駆動回路及びインバータ装置

【課題】レベルシフト回路の電圧変動等に起因するコモンモードノイズ発生時でもクランプすることなく、信号を伝達できるレベルシフト回路、スイッチング素子駆動回路及びインバータ装置を提供する。

【解決手段】セットパルス及びリセットパルスを発生するパルス発生回路と、セットパルスを電流に変換する第1スイッチング素子及びリセットパルスを電流に変換する第2スイッチング素子と、浮動電位側にあり、第1スイッチング素子で電流に変換された信号を電圧に変換するセット用負荷及び第2スイッチング素子で電流に変換された信号を電圧に変換するリセット用負荷と、セット用負荷の信号レベルおよびリセット用負荷の信号レベルから、制御パルス信号を再生するパルス再生回路を備えるレベルシフト回路において、セット用負荷及びリセット用負荷として非線形の負荷特性を有する回路を用いる。

(もっと読む)

ラッチ回路、フリップフロップ回路および半導体装置

【課題】ラッチ回路およびフリップフロップ回路のソフトエラー耐性の向上。

【解決手段】複数の回路ユニットIV1-IV4を有し、複数の回路ユニットの出力が他の反転回路の入力にフィードバックされ、2以上の入力端子1,2を有するデータ保持回路11と、2以上のクロックCK01,XCK01;CK02,XCK02にそれぞれ同期して、データ保持回路の2以上の入力端子に入力信号を入力する2以上の入力回路TG1,TG2と、を備え、データ保持回路は、2以上の入力端子に同時に入力信号Dinが入力されかつ2以上のクロックが同時に変化した時のみ、2以上の入力端子に正帰還がかかる。

(もっと読む)

電子回路

【課題】電子回路(例えば、マイクロコンピュータ)の動作モードに応じて、低周波数の発振器について適切な電源インピーダンスを設定することにより、前記発振器の誤動作を防止しながら、消費電力を適切に低減することができる。

【解決手段】システムクロックのクロック源として、高速発振器11、中速発振器12、低速発振器13が設けられる。また、時計用クロックを発生する水晶発振器30が設けられる。そして、高速発振器11が動作している時は、水晶発振器30の電源インピーダンスを低くして、耐ノイズ性を高める。一方、高速発振器11、中速発振器12、低速発振器13がすべて停止している待機時には、水晶発振器30の電源インピーダンスを高くして消費電力を抑える。

(もっと読む)

レベルシフト回路

【課題】外的要因による誤動作を防止して確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態をセットするセット信号を送信するセットレベル回路21と、第2電圧レベルの論理電圧状態をリセットするリセット信号を送信するリセットレベル回路22と、第2電圧レベルでセット信号及びリセット信号を検出するための基準値を設定する基準レベル回路C3とを有し、セットレベル回路とリセットレベル回路と基準レベル回路との各々は、それぞれコンデンサC1〜C3を介して第1電圧レベルから第2電圧レベルに信号を伝達する。

(もっと読む)

シュミットトリガ型インバータ

【課題】さらに入力ノイズ耐性を有するシュミットトリガ型インバータを提供すること。

【解決手段】入力側ノードへの供給電圧が増加して第1の基準電圧に達するに従い出力側ノードから出る電圧が比較高電圧レベルから比較低電圧レベルに遷移し、入力側ノードへの供給電圧が減少して第1の基準電圧より低い第2の基準電圧まで減少するに従い出力側ノードから出る電圧が比較低電圧レベルから比較高電圧レベルに遷移するインバータと、インバータの入力側ノードに一方端が接続された第1の抵抗素子と、インバータの入力側ノードに一方端が接続された、該一方端の電圧が上昇するほどに抵抗値が減じる可変抵抗素子と、可変抵抗素子の他方端に一方端が接続された第2の抵抗素子と、ドレインが第2の抵抗素子の他方端に接続され、ゲートがインバータの出力側ノードに接続され、ソースが接地電位に接続されたnチャネルMOSトランジスタとを具備する。

(もっと読む)

半導体装置、シフトレジスタ、電子機器

【課題】パルス出力回路内のノイズを低減し、より確実な動作を保証する半導体装置を提供する。

【解決手段】クロック信号等の振幅を有する信号に接続されたTFTが、パルス出力が無い期間にもON、OFFが確定する構成とする。具体的には、第1の振幅補償回路110の有する二つの入力部のうち一つを、トランジスタ106のゲート電極と電気的に接続させ、且つ第2の振幅補償回路120の出力部とも電気的に接続させる。また、第3の入力端子は、第1の振幅補償回路110には入力されず、第2の振幅補償回路120のみに入力される。この構成により、TFT105のゲート電極はTFT102,106を介してLレベルに確定され、従来例のようなノイズが発生することもない。

(もっと読む)

1 - 20 / 60

[ Back to top ]