Fターム[5J056BB34]の内容

論理回路 (30,215) | 目的、効果 (4,057) | 信頼性の向上 (1,356) | 雑音入力による誤動作防止 (130) | 出力線からの雑音対策 (18)

Fターム[5J056BB34]に分類される特許

1 - 18 / 18

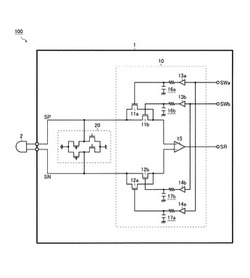

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

半導体集積回路および高周波モジュール

【課題】出力波形のリップルを低減可能な半導体集積回路を提供する。

【解決手段】例えば、高周波スイッチ回路RFSWと、そのオン・オフを制御するスイッチ制御回路SWCTLを備え、SWCTLは、2個のダウンコンバータ回路VGEN1,VGEN2と、レベルシフト回路LS[1]〜LS[4]を備える。各LS[n]は、レベルシフト段LSSG[n]とその後段に接続された出力段OTSG[n]を持ち、RFSWは、OTSG[n]からの制御信号OUT[n]によって制御される。LSSG[n]は、VGEN1からの負の電源電圧(−VSS1)を用いて動作し、OTSG[n]は、VGEN2からの負の電源電圧(−VSS2)を用いて動作する。−VSS1では、LSSG[n]のレベルシフト動作に伴いリップルが生じ得るが、−VSS2ではOTSG[n]の動作がスイッチング動作であるためリップルが生じ難い。

(もっと読む)

半導体メモリのデータ出力回路及びその制御方法

【課題】カップリングノイズを減少させることができる半導体メモリのデータ出力回路およびその制御方法を提供すること。

【解決手段】複数のグローバルラインと、複数のデータを互いに異なるタイミングで複数のグローバルラインに出力するように構成されたセンスアンプブロックと、複数のグローバルラインを介して伝送された複数のデータを互いに異なるタイミングでラッチするように構成されたパイプラッチブロックと、アドレス信号を用いてセンスアンプブロックの出力タイミングとパイプラッチブロックのラッチタイミングとを制御するように構成された制御部とを備えることを特徴とする。

(もっと読む)

半導体装置

【課題】終端抵抗のオンオフの切り替え時に外部端子にインピーダンスの急激な変化が生じることを低減する。

【解決手段】外部端子(図2のDQに相当)と、外部端子に接続され、出力信号を外部端子に出力可能とする出力回路(図2の21に相当)と、外部端子に終端抵抗をオンオフ可能に接続する終端回路(図2の22に相当)と、終端抵抗がオフ状態又はオン状態のいずれか一方の状態から他方の状態に変化するまでの時間を、データ出力時に出力信号が一方の論理レベルから他方の論理レベルへ変化するまでの時間以上となるように制御する第1のスルーレート制御回路(図2の23aに相当)と、を備える。

(もっと読む)

同期化結晶発振器ベースのクロックを採用するシステム

【課題】改良された同期クロックシステムを提供する。

【解決手段】同期クロック信号を必要とする複数のシステムノードを有する電子システム用の同期クロックシステム。クロックシステムは、第1の同期バスと第1の同期バスから絶縁された第2の同期バスと、交互にバスに接続された少なくとも1対、そして好ましくは複数対のSXOモジュールを含む。システムノードの各々は、第1のバスに沿った任意の場所において適宜選択されたあらゆる接続点のうちの異なる1つで接続される。SXOモジュールが接続されるバスに沿った点は、およそ等間隔で隔てられる。システムノードは信号調整回路を用いてバスに接続され、信号調整回路は、補正回路、増幅器、周波数逓倍器、論理変換器、およびファンバッファを含んでいてもよい。

(もっと読む)

ドライバ回路及びドライバ回路の調整方法

【課題】受信状態の劣化を抑制すること。

【解決手段】分圧部32は、出力部31に接続された可変抵抗器VR1と出力部31との間の第1電圧V1を、固定抵抗器R2と可変抵抗器VR3とによる分圧比にて分圧して第3電圧V3を生成する。入力部33は、第2電圧V2から第3電圧V3を減算して第4電圧V4を生成する。極性検出回路35は、第4電圧V4の極性と第3電圧V3の極性を比較し、比較結果に応じた検出信号SR1を出力する。そして、調整回路37は、極性検出回路36から出力される検出信号SR1に基づいて、極性が一致するように分圧部32に含まれる可変抵抗器VR3を調整する。

(もっと読む)

半導体装置及びそのデータ出力方法

【課題】本発明は、より安定的なデータ出力動作を実現する半導体装置及びそのデータ出力方法を提供する。

【解決手段】本発明の半導体装置は、イネーブル信号とデータの入力を受けてプルアップソース信号とプルダウンソース信号を生成し、前記プルアップソース信号又は前記プルダウンソース信号の生成タイミングを遅延させる駆動制御部;前記プルアップソース信号と前記プルダウンソース信号を駆動して駆動データを生成するドライバ;及び前記ドライバの出力端に接続され、可変的な抵抗値を有するPOD(Pseudo Open Drain)インピーダンス制御部;を含む。

(もっと読む)

デジタルデータ伝送装置

【課題】電源電圧や接地レベルの変動に伴う信号の振幅変動やジッター等の非対称歪の発生が抑えられるようにしたデジタルデータ伝送装置を提供すること。

【解決手段】システムLSIから出力されるデジタルデータを、バッファ回路3(1)を介して波形整形回路4に供給し、ここで立上り部と立下り部にオーバーシュートがかけられたデジタルデータが、駆動電源ライン25から伝送路に供給されるようにし、このとき、調整電圧発生回路31により駆動電源ライン25の電圧を調整し、伝送系の波形歪みによる影響の除去に適したオーバーシュートがえられるようにしたもの。

(もっと読む)

出力回路、出力方法、出力回路の製造方法、および電子機器

【課題】 ノイズを発生させ難い出力回路等を提供する。

【解決手段】 出力回路(10)は、入力ノード(IN)と、出力ノード(OUT)と、入力ノードと出力ノードとの間に配置され、第1のゲート(13)を有する第1の出力トランジスタ(12)と、入力ノードと出力ノードとの間に配置され、第2のゲート(16)を有する第2の出力トランジスタ(15)と、入力ノードと出力ノードとの間に配置され、第3のゲート(19)を有する第3の出力トランジスタ(18)と、を備える。第1のゲート(13)および第2のゲート(16)は、第1の方向(DR1)に、第3のゲート(19)を介さず、互いに接続される。第2のゲート(16)および第3のゲート(19)は、第1の方向とは異なる第2の方向(DR2)に、第1のゲート(13)を介さず、互いに接続される。第1のゲート(13)および第3のゲート(19)は、第2のゲート(16)を介して接続される。

(もっと読む)

信号伝送回路及びその特性調整方法、メモリモジュール、並びに、回路基板の製造方法

【課題】伝送線路間のインピーダンス不整合を検出する。

【解決手段】メモリモジュール104とMCH102とを相互に接続する伝送線路301,302と、伝送線路301のインピーダンスを記憶するBIOS108と、伝送線路302のインピーダンスを記憶するSPDチップ220とを備え、CPU101は、BIOS108に記憶されたインピーダンスとSPDチップ220に記憶されたインピーダンスとの整合情報をMCH102に出力する。MCH102は、これに応じてDRAM200へのモードレジスタセットを実行し、DRAM200のODTインピーダンスを変化させる。

(もっと読む)

半導体集積回路

【課題】 出力バッファのスイッチングノイズによる誤動作を防止した半導体集積回路を提供する。

【解決手段】 出力バッファトランジスタ103のソース電極と、上記出力バッファトランジスタが形成されるウェルには、同じ電源204から電圧が供給されるが配線経路を分離して別配線で電源を供給する。出力バッファトランジスタ103のスイッチングによって、ソース電極の電位が変動してもウェルの電位変動が抑えられる。特に、おなじウェルに形成された出力バッファトランジスタ以外のトランジスタや、半導体基板を経由して電気的に接続された他のウェルに形成されたトランジスタへのノイズの影響を防ぐことができる。

(もっと読む)

半導体素子駆動装置、電力変換装置、及びモータ駆動装置、並びに半導体素子駆動方法、電力変換方法、及びモータ駆動方法

【課題】直列接続IGBT3,4の接続点7のdV/dtによる誤動作発生時に、上下アーム短絡などの事故を回避できる高信頼性IGBT駆動装置を提供する。

【解決手段】高低圧側IGBT3,4は、デッドタイムを挟み相補的にオン/オフ制御される。これらデッドタイム期間中に、高圧側IGBT3をオフさせるリセットパルスRSを、例えば、次のような要領で発生させる。(1)低圧側IGBT4のオン指令LDの直前に、(2)低圧側IGBT4のオン指令LDの直前から、このオン指令LDと重なる期間tdをもつように、(3)デッドタイムDT期間中、継続して、(4)低圧側IGBT4がオンとなる直前のデッドタイム期間中、継続して、(5)高圧側IGBT3のオン状態を観測したとき、低圧側IGBTのオン指令を無効とするように、リセットパルスを生成する。

(もっと読む)

出力回路

【課題】従来の出力回路は、出力端子から入力するノイズに対する耐性が低い問題があった。

【解決手段】本発明にかかる出力回路は、入力信号を受ける入力端子と、第1の電源gndと出力端子との間に接続される出力トランジスタMNoutと、入力端子及び出力トランジスタMNoutのゲートに接続され、入力信号に基づいて出力トランジスタMNoutのゲートに対する電流の吐き出し又は引き込みを制御する電流制御回路10と、第1の電源gndに接続される電圧生成回路11と、出力トランジスタMNoutのゲートと電圧生成回路11との間に接続され、入力信号により開閉状態が制御されるスイッチ回路S1とを備え、出力トランジスタMNoutのゲートと第1の電源gndとの電位差が所定の値以下になると、入力信号の電圧レベルにかかわらず、スイッチ回路S1はオフ状態となることを特徴とするものである。

(もっと読む)

出力回路

【課題】動作環境に関らず安定にリンギングを生じさせることなく、内部読出データに従って出力データを生成する。

【解決手段】出力回路は、出力許可信号OEMと入力信号ZDDとに応答して第1のノードに入力信号の論理に対応する論理を有する信号を伝達するゲート4と、ゲートの出力信号に応答して、出力ノード6を入力信号の論理に対応する電位レベルに駆動する第1のドライブ素子2aと、ゲートの出力信号を遅延して出力する遅延回路100と、この遅延回路の出力信号に従って出力ノードを第1のドライブ素子よりも速い速度で駆動する第2のドライブ素子2bとを備える。この遅延回路の遅延時間が、出力許可信号と入力信号出力指示信号DOTとに従って調整される。

(もっと読む)

帯域幅制限負荷用のトライステートドライバ

CMOS駆動回路が所定の回数の同値データビットが伝送された後に、トライステート状態を提供するように構成され、伝送チャネルに沿った符号間干渉(ISI)の存在を低減させる。伝送チャネルが帯域制限される場合、トライステート技術の使用が所定のビット期間中の供給線路への完全な移行を可能にする。 (もっと読む)

入出力共用端子制御回路

【課題】ソフトウェアシーケンスを組むことなく、汎用I/Oピンからのハザード出力を防止する入出力共用端子制御回路を提供する。

【解決手段】データ選択手段101は、複数の回路からの複数のデータ信号の中から、データ信号を選択し、方向選択手段102は、それらの回路からの複数の方向制御信号の中から、同じ回路の方向制御信号を選択する。データ保持手段103および方向保持手段104は、選択されたデータ信号および方向制御信号をそれぞれ保持する。データ選択手段105は、データ選択手段101またはデータ保持手段103からのデータ信号を選択し、方向選択手段106は、方向選択手段102または方向保持手段104からの方向制御信号を選択する。出力手段107は、方向選択手段106からの方向制御信号に従って、データ選択手段105からのデータ信号を入出力共用端子108に出力する。

(もっと読む)

ノイズ低減高周波回路

【課題】 伝送線路の特性を問わず、常にノイズフィルタの諸元上の阻止域でノイズ除去効果を発揮させる。

【解決手段】 抵抗3および電源4からなる終端回路により伝送線路1のインピーダンス整合が図られるため、伝送線路1に電流・電圧の定在波が生じない。一般に定在波の発生は、その周波数におけるノイズフィルタのノイズ除去効果を減殺するものであるから、電流レベル・電圧レベルの変化のないフラットな特性を得ることで、伝送線路1の特性を問わず、ノイズフィルタ2の諸元上の阻止域でノイズ除去効果を発揮させることができる。

(もっと読む)

1 - 18 / 18

[ Back to top ]