Fターム[5J056BB49]の内容

Fターム[5J056BB49]に分類される特許

1 - 20 / 223

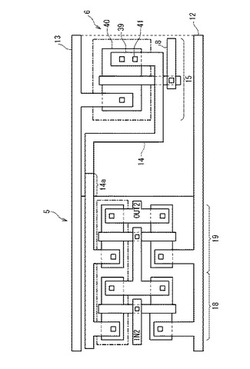

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

半導体装置及び表示装置

【課題】より良い動作を実現する半導体装置を提供する。

【解決手段】第1のトランジスタと、第1のトランジスタのゲートに電気的に接続される

第2のトランジスタとを有し、第1のトランジスタの第1の端子は第1の配線に電気的に

接続され、第1のトランジスタの第2の端子は第2の配線に電気的に接続され、第1のト

ランジスタのゲートは第2のトランジスタの第1の端子又は第2の端子に電気的に接続さ

れることにより半導体装置が構成されるものである。上記において、第1乃至第2のトラ

ンジスタは、少なくともチャネル領域に酸化物半導体を有し、かつ、オフ電流が小さなも

のを用いることができる。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、第1及び第2の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

半導体装置

【課題】新たな構成の半導体装置を提供する。

【解決手段】半導体装置は、p型の第1のトランジスタ、n型の第2のトランジスタ、第3のトランジスタ及び第4のトランジスタを有する。第3のトランジスタのソース又はドレインの一方は、第1の電位を供給することができる機能を有する配線に接続され、他方は、第1のトランジスタのソース又はドレインの一方に接続される。第2のトランジスタのソース又はドレインの一方は、第1のトランジスタのソース又はドレインの他方と接続され、他方は、第4のトランジスタのソース又はドレインの一方に接続される。第4のトランジスタのソース又はドレインの他方は、第1の電位よりも低い第2の電位を供給することができる機能を有する配線に接続される。第3のトランジスタ及び第4のトランジスタのチャネル形成領域には酸化物半導体材料が用いられる。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、複数の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

半導体装置

【課題】 待機動作時のオフリーク電流を削減した論理回路を含む半導体装置を提供することを目的とする。

【解決手段】 半導体装置100は、第1の動作電圧または第1の動作電圧よりも小さい第2の動作電圧を供給する電源供給部110と、電源供給部110から第1または第2の動作電圧を受け取る低しきい値のP型トランジスタTpと、トランジスタTpと基準電位との間に接続されたN型トランジスタTnとを有し、トランジスタTp、Tnは、ゲートに入力された信号Dinに応じて出力信号Doutを生成する論理回路を構成する。電源供給部110は、通常動作時、第1の動作電圧をトランジスタTpのソースに供給し、待機動作時、第2の動作電圧をトランジスタTpのソースに供給する。第2の動作電圧は、トランジスタTp、Tnそれぞれのゲート・ソース間電圧の振幅がトランジスタTp、Tnのしきい値よりも大きくなるように設定される。

(もっと読む)

コンパレータ、及びそれを用いた半導体装置

【課題】新たな構成のチョッパ型のコンパレータを提供する。

【解決手段】コンパレータは、インバータと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、インバータの入力端子と出力端子とは、第1のスイッチを介して電気的に接続され、インバータの入力端子は、容量素子の一対の電極のうちの一方と電気的に接続され、容量素子の一対の電極のうちの他方は、第2のスイッチを介して参照電位が与えられ、入力された信号電位は第3のスイッチを介して容量素子の一対の電極のうちの他方に与えられ、インバータの出力端子から出力される電位を出力信号とし、第1のスイッチは、チャネルが酸化物半導体層に形成されるトランジスタを用いて構成される。

(もっと読む)

半導体装置

【課題】スタンバイ時のリーク電流と回路面積の増大を抑制する。

【解決手段】第1電源に接続する第1の回路11の入力対に出力が夫々接続された第2及び第3の回路12、13と、前記第1の回路の入力、又は、前記第1の回路の内部ノードに接続された第4の回路14と、を含み、前記第2の回路及び前記第3の回路は、第2電源と第3電源間に接続され、スタンバイ時にパワーゲーティングされる回路を有し、前記第2の回路は、前記第2及び第3電源電位を振幅範囲とする信号を入力し、前記第2の回路の出力は前記第3の回路の入力に接続され、前記第1の回路の出力信号の振幅範囲は、前記第1電源電位と、前記第2又は第3電源電位とされ、前記第4の回路は、パワーゲーティング時に前記第1の回路の前記入力対、又は前記内部ノードの論理値を保持し、スタンバイ時にも前記第1の回路の出力信号の論理を前記入力信号に関連した論理に維持する。

(もっと読む)

半導体装置

【課題】リーク電流を従来よりも抑えること。

【解決手段】本発明の半導体装置1は、外部から信号を供給可能な入力端子10と、内部回路30と、制御部40と、バッファ回路20とを具備している。制御部40は、起動時から所定時間が経過するまでの間にマスク解除信号MASK“H”を出力する。バッファ回路20は、入力端子10に供給される電圧VDD又は電圧GNDを表す信号をマスク解除信号MASK“H”に応じて内部回路30に出力する。本発明の半導体装置1では、外部から入力端子10に信号が供給されているときにノイズが発生しても、バッファ回路20が入力端子10から内部回路30への伝送を有効にする時間以外は無効にしている。このため、マスク回路26によるバッファ回路20と内部回路30との切り離しにより、内部回路30への貫通電流を防止することができる。

(もっと読む)

半導体集積回路及び半導体集積回路の電源制御方法

【課題】製造プロセス条件の変動に関わらず短い電源立ち上げ時間を確保することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第1の電源線と第2の電源線との間に並列に配置された複数の電源スイッチと、複数の電源スイッチを設定時間間隔で順次導通させる駆動回路と、第2の電源線と第3の電源線との間に配置される内部回路と、第2の電源線と第3の電源線との間の電圧が上昇して所定値に到達すると検知信号をアサートする昇圧検知回路と、検知信号のアサート時において導通状態にある複数の電源スイッチの数に応じて設定時間間隔を変化させる制御回路とを含む。

(もっと読む)

スイッチ回路

【課題】リーク電流がスイッチ回路に接続される回路に影響を与えることを抑制することが可能なスイッチ回路の提供。

【解決手段】第1の電位と第2の電位の間の接続状態をオンオフする第1のトランジスタと、該第1のトランジスタのドレインにソースが接続され、前記第1のトランジスタと略同一の特性を有する第2のトランジスタとを備え、前記第1のトランジスタをオフした時に、前記第1のトランジスタのゲート−ソース間電圧VGS1と、前記前記第2のトランジスタのゲート−ソース間電圧VGS2が略等しくなることを特徴とするスイッチ回路。

(もっと読む)

CMOS回路及び半導体装置

【課題】しきい電圧VTが小さくてもリーク電流が小さく、また高速にかつ小さな電圧振幅で動作するCMOS回路さらには半導体装置を提供することである。

【解決手段】ゲートとソースを等しい電圧にしたときにドレインとソース間に実質的にサブスレショルド電流が流れるようなMOST(M)を含む出力段回路において、その非活性時には、前記MOST(M)のゲートとソース間を逆バイアスするように該MOST(M)のゲートに電圧を印加する。すなわち、MOST(M)がpチャンネル型の場合にはp型のソースに比べて高い電圧をゲートに印加し、また、MOST(M)がnチャンネル型の場合にはn型のソースに比べて低い電圧をゲートに印加する。活性時には、入力電圧に応じて該逆バイアス状態を保持するかあるいは順バイアス状態に制御する。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】スタンバイ状態への設定と解除が頻繁に繰り返されることにより、消費電力が増大することを避けることのできる半導体装置を提供する。

【解決手段】内部回路50と、第1制御信号を受けて内部回路への電源供給を制御する電源制御回路40と、第2制御信号を受けて第1制御信号を出力する制御信号発生回路30と、を備え、制御信号発生回路30は、第2制御信号の非活性期間が第1の期間未満であるときに第1制御信号を非活性状態とせず、第1の期間以上であるときに第1制御信号を非活性状態とする。

(もっと読む)

半導体集積回路

【課題】他の回路のタイミングに影響を与えずに、動作モードにおける組み合わせ回路のオフリーク電流を低減させる半導体集積回路を提供する。

【解決手段】組み合わせ回路32と、組み合わせ回路の出力信号をクロック信号CKに同期して保持する順序回路100と、を備え、順序回路は、クロック信号のエッジを検出してパルスを生成するパルス生成回路と、出力信号をパルスに同期してラッチするラッチ回路と、クロック信号とパルスとから組み合わせ回路の電源制御信号を生成する電源制御信号生成回路と、電源制御信号により導通非導通が制御され、導通するときに組み合わせ回路に電源を供給する電源スイッチと、を備える。

(もっと読む)

半導体装置及び半導体装置の制御方法

【課題】半導体装置の消費電力を削減する。

【解決手段】回路動作スケジュール補正部14が、回路動作スケジュールを入力し、複数の回路動作期間を連続するように、回路動作期間の開始時刻または終了時刻を補正し、電源スイッチ制御部15が、補正された回路動作スケジュールにしたがって、回路11へ電源を供給するか否かを切り替える電源スイッチ12をオンまたはオフすることで、電源スイッチ12の動作回数が減少し、電源スイッチ12をオフからオンする際の、電源復帰時のエネルギー損失が減少し、消費電力が低減される。

(もっと読む)

半導体集積回路装置

【課題】簡易な構造により、MOSFETのサブスレショールドリーク電流を低減することができる半導体集積回路装置を提供すること。

【解決手段】本発明にかかる半導体集積回路装置は、被制御回路5と基板バイアス制御回路101を有する。被制御回路5は、基板上に形成される1以上のMOSFETを有する。基板バイアス制御回路101は、出力端から被制御回路5の基板に供給する基板バイアスを制御する。基板バイアス制御回路101は、N型MOSFET1及び2を有する。N型MOSFET2は、被制御回路5のMOSFETと同じ電流−電圧特性を有し、サブスレショールドリーク電流を接点Bの電圧VBに変換する。N型MOSFET1は、一端が基板バイアス制御回路101の出力端と接続され、接点Bの電圧VBに応じて基板バイアスを接地電位以下に制御する。

(もっと読む)

半導体集積回路装置

【課題】被制御回路のソース電位を精度良く制御する回路構成を小面積で実現する。

【解決手段】電源線6及び接地線4に接続された被制御回路1のソース線5と、前記接地線4との間に、前記ソース線5の電位を制御するソース制御回路2と、前記ソース線5と前記接地線4とを導通、非導通状態へ制御する、前記ソース制御回路2と並列に接続された遮断スイッチ回路3とを有する。ソース制御回路2は、ダイオード回路2aと、前記ダイオード回路2aと並列に接続された抵抗回路2bとを有する。

(もっと読む)

1 - 20 / 223

[ Back to top ]