Fターム[5J056BB38]の内容

Fターム[5J056BB38]に分類される特許

1 - 20 / 127

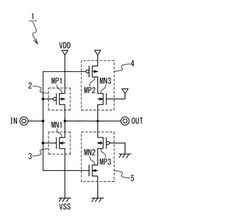

集積回路、集積回路装置及び伝送システム

【課題】回路遅延の増大を抑制しながら、回路しきい値電圧のバラツキを抑制できる集積回路を提供する。

【解決手段】

集積回路1は、高位側電源VDDと出力端子OUTの間に接続されたPMOSトランジスタMP1と、低位側電源VSSと出力端子OUTの間に接続されたNMOSトランジスタMN1と、高位側電源VDDと出力端子OUTの間に直列に接続されたPMOSトランジスタMP2及びNMOSトランジスタMN3と、低位側電源VDDと出力端子OUTの間に直列に接続されたNMOSトランジスタMN2及びPMOSトランジスタMP3とを備えている。PMOSトランジスタMP1、MP2、及びNMOSトランジスタMN1、MN2のゲートが入力端子INに接続されている。また、NMOSトランジスタMN3のゲートは高位側電源に接続され、PMOSトランジスタMP3のゲートは低位側電源に接続されている。

(もっと読む)

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

半導体装置

【課題】しきい値電圧のばらつきの影響を低減する。

【解決手段】トランジスタのゲート・ソース間に設けられた容量素子に電荷を充電し、その後容量素子に充電された電荷を放電することで該トランジスタのしきい値電圧を取得し、その後負荷に電流を流す半導体装置において、容量素子の一方の端子の電位は、ソース線の電位より大きく設定し、ソース線の電位は電源線の電位及び負荷のカソード側の電位よりも小さい電位に設定する。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

出力回路

【課題】差動出力電圧の振幅のばらつきを抑制した出力回路を提供する。

【解決手段】出力回路は,定電圧ノードと基準電源との間に,複数のスイッチ素子のオン,オフにより合成抵抗値が可変制御可能な複数の抵抗を有し,定電圧ノードに第1の電流を生成する定電流生成回路と,第1の電流をカレントミラーにより生成した第2の電流を,内部回路から供給される内部差動信号に応じて,出力端子対に出力する出力駆動回路と,出力端子対の出力差動電圧の差が所望の電圧差と一致するように,定電流生成回路の複数のスイッチ素子を制御するスイッチ素子制御信号を生成する出力振幅調整部とを有する。

(もっと読む)

イネーブル信号生成回路

【課題】後段のイネーブル回路を確実に制御し、また電源電圧が高くなっても消費電流が増大しないようにする。

【解決手段】制御入力端子1にゲートが接続されソースがトランジスタMN2を介して接地に接続されたトランジスタMN1と、トランジスタMN1のドレインと電源VDDとの間に接続された抵抗R2と、抵抗R2の両端にソースとドレインが接続されたトランジスタMP1と、トランジスタのMP1ゲートとソース間に接続された抵抗R3と、ソースがトランジスタMP1のゲートに接続されゲートがトランジスタMP1のドレインに接続されドレインが負荷回路3に接続されたトランジスタMP2とを備え、トランジスタMP2のゲートを制御出力端子2に接続した。

(もっと読む)

差動入力回路および差動入力回路の電圧特性調整方法

【課題】ソースが共通接続されそれぞれのゲートが二つの入力端子に接続さた二つのトランジスタを有する差動対を備える差動入力回路において、より適正に入力オフセットをより小さくする。

【解決手段】トランジスタTin1,トランジスタTin2のドレインに高電圧印加回路60を接続し、トランジスタTin1のソースおよびトランジスタTin2のソースと接地電圧印加点GNDとの間にトランジスタTsenを設け、論理ローレベルの電圧の制御信号SENをスイッチング回路70に入力すると共に制御信号Tcとしてクロック信号を入力して入力端子IN1に電圧V1を印加すると共に入力端子IN2に電圧V2を印加し、検出した出力端子OUT,OUTBの電圧に応じてトランジスタTin1,Tin2のドレインに高電圧印加回路60により電源電圧Vddhを印加する

(もっと読む)

電圧レギュレータ回路

【課題】複雑な制御を必要とせず、集積回路のトランジスタの閾値電圧バラツキに応じて所望の動作速度に適した電源電圧を提供することができる。

【解決手段】被安定電圧が入力される入力端子1と、安定化された電圧が出力される出力端子2と、入力端子1および出力端子2と電位差を有する一定電圧に設定される共通端子3と、正入力端子および負入力端子を有する差動増幅器4と、差動増幅器4の出力に基づいて入力端子1から出力端子2に流れる電流を制御する電流制御素子5と、出力端子2と共通端子3との間の電位差を分圧し、差動増幅器4の正入力端子に帰還させる分圧回路6と、出力端子2から電力を供給されるが出力端子2の電圧に依存せず、共通端子3の電圧を基準とする当該集積回路のトランジスタの閾値電圧に比例した電圧を差動増幅器4の負入力端子に出力する閾値参照電圧源7とを備える。

(もっと読む)

集積回路及び集積回路の制御方法

【課題】回路若しくは装置が、仕様或いは規格に適用しない部分があったとしても、使用することに問題がない場合の対応方法のひとつを提供する。

【解決手段】集積回路が入出力回路とタイミング測定回路とを含み、前記入出力回路の第1の入力端子に入力される第1の信号と、前記入出力回路の第1の出力端子から出力される第2の信号とが前記タイミング測定回路に入力され、前記第2の信号は、前記入出力回路の第1の入出力端子における信号が前記第1の出力端子から出力されたものであり、前記タイミング測定回路において、前記第1の信号における第1の変化を検出し、前記第2の信号における前記第1の変化に対応する第2の変化を検出し、前記第1の変化を検出したときと前記第2の変化を検出したときとの間の時間間隔の計測を行うことを特徴とする。

(もっと読む)

半導体装置

【課題】可変抵抗回路の抵抗値の調整可能範囲が大きな半導体装置を提供する。

【解決手段】この半導体装置は、複数組の抵抗素子RA,RBおよび複数組のトランジスタP,Qを含む出力バッファDOBと、複数のレプリカ回路RPと、複数組の演算増幅器AP,ANとを備え、出力バッファDOBの出力インピーダンスZp,Znが所定値になるように、複数組のトランジスタP,Qのドレイン電流を調整する。したがって、製造プロセスなどの変動によって抵抗素子RA,RBの抵抗値が大きく変動した場合でも、出力インピーダンスZp,Znを所定値に設定できる。

(もっと読む)

出力回路

【課題】負荷容量の要求仕様に適合する出力回路を提供する。

【解決手段】出力回路1は,第1の電源VDDと出力トランジスタP1のソースとの間に設けられた電流調整用トランジスタP2と,出力信号EXが,第2の電位から第1の電位に変化する途中で,電流調整用トランジスタP2の電流を増大させるよう,出力信号EXの電位に応じて,電流調整用トランジスタP2のゲートを制御する電流調整回路11とを有する。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

出力バッファ回路

【課題】出力信号のデューティを保ちつつ消費電流の変化を低減する。

【解決手段】出力バッファ回路は、出力回路(300)と、第1入力回路(210)と、第2入力回路(220)と、第1クランプ回路(110)と、第2クランプ回路(120)とを具備する。出力回路(300)は、第1出力トランジスタ(P301)と第2出力トランジスタ(N301)とを備え、出力信号(VOUT)を出力する。第1クランプ回路(110)および第2クランプ回路(120)のそれぞれは、カスコード接続される第1導電型のトランジスタ(P111/P121)と、第2導電型のトランジスタ(N111/N121)とを備える。第1クランプ回路(110)は、所定の期間第1入力回路(210)の出力電圧(VA1)をクランプする。第2クランプ回路(120)は、所定の期間第2入力回路(220)の出力電圧(VA2)をクランプする。

(もっと読む)

レベルシフト回路

【課題】入力信号のレベルが低電圧であっても、信号レベルの変換を高速かつ確実に行うことのできるレベルシフト回路を提供する。

【解決手段】 実施形態のレベルシフト回路は、厚膜のPMOSトランジスタTP1(TP2)および厚膜のNMOSトランジスタTN1(TN2)からなる一対の相補回路を有し、厚膜のNMOSトランジスタTN1(TN2)のゲートに入力された低電圧レベルの信号A(/A)を、厚膜のPMOSトランジスタTP2(TP1)を介して昇圧し、高電圧レベルの信号Z(/Z)を出力する。この一対の相補回路のそれぞれの出力端子と接地端子GNDとの間には、ブースター回路11(12)がそれぞれ接続されている。ブースター回路11(12)は、高電圧レベルの出力信号/Z(Z)の立ち下りを加速する。

(もっと読む)

内部電源電圧生成回路

【課題】ロジック回路の動作時、貫通電流が、製造ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタと、前記ゲートに与えられる電圧をソースフォロワ出力するトランジスタの最大電流を制限する電流制限回路と、を備え、ロジック回路への最大電流、及び消費電流を抑えることが可能な構成とした。

(もっと読む)

内部電源電圧生成回路

【課題】ロジック回路の動作時の貫通電流が、ロジック回路を構成するP型トランジスタとN型トランジスタの閾値電圧ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタを有し、内部電源電圧の値が、N型トランジスタの閾値電圧と、P型トランジスタの閾値電圧の絶対値の和に基づいて与えられ、前記N型トランジスタは、前記ロジック回路内部のN型トランジスタと同一の製造プロセスで形成され、前記P型トランジスタは、前記ロジック回路内部のP型トランジスタと同一の製造プロセスで形成される、内部電源電圧生成回路、とした。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

半導体集積回路及び半導体集積回路の電源制御方法

【課題】製造プロセス条件の変動に関わらず短い電源立ち上げ時間を確保することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第1の電源線と第2の電源線との間に並列に配置された複数の電源スイッチと、複数の電源スイッチを設定時間間隔で順次導通させる駆動回路と、第2の電源線と第3の電源線との間に配置される内部回路と、第2の電源線と第3の電源線との間の電圧が上昇して所定値に到達すると検知信号をアサートする昇圧検知回路と、検知信号のアサート時において導通状態にある複数の電源スイッチの数に応じて設定時間間隔を変化させる制御回路とを含む。

(もっと読む)

差動出力回路

【課題】ゲート電圧に対する遅延調整を行わずに、クロスポイントの変動を抑えること。

【解決手段】駆動部100と出力部101は、カレントミラー構成により、プロセス、電圧、温度条件が変動しても共に同一の変動となるため、入力信号INTの信号レベルが“H”から“L”に切り替わる際、MOSFET3、6がオンしているときに、MOSFET5、4がオフ状態からオン状態に速く切り替わることはない。従って、クロスポイントの変動を抑えることができる。また、この構成により、ゲート電圧PL、PR、NL、NRは、電源電圧VSSからVDDまでフルスイングされないため、MOSFET3、6をオンさせ、MOSFET5、4をオフさせる場合、ゲート電圧PLの立ち下がりに対してゲート電圧NLの立ち下がりに遅延をもたせたり、ゲート電圧NRの立ち上がりに対してゲート電圧PRの立ち上がりに遅延をもたせたりする必要がない。

(もっと読む)

1 - 20 / 127

[ Back to top ]