Fターム[5J056BB22]の内容

Fターム[5J056BB22]の下位に属するFターム

入力線へ発生する雑音の防止 (16)

出力線へ発生する雑音の防止 (76)

電源線へ発生する雑音の防止 (53)

空間へ発生する雑音の防止 (12)

Fターム[5J056BB22]に分類される特許

1 - 20 / 68

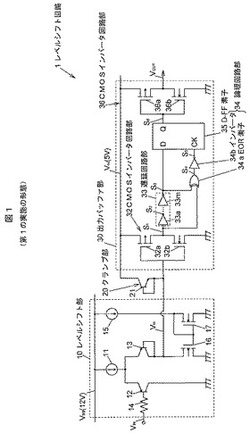

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法

【課題】電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法を提供する。

【解決手段】本発明の電力制御回路は、電源電圧とロジック回路との間に連結されてロジック回路への電源供給をスイッチングする回路であって、外部から並列的にモード転換信号を受信する複数の第1パワーゲーティングセルと、第1パワーゲーティングセルのうちの何れか1つと連結される少なくとも1つの第2パワーゲーティングセルと、第2パワーゲーティングセルと直列連結される複数の第3パワーゲーティングセルと、直列連結された複数の第3パワーゲーティングセルのうち、先端の第3パワーゲーティングセルと並列連結される複数の第4パワーゲーティングセルとを含み、モード転換信号は、第1パワーゲーティングセルのうちの何れか1つ、第2及び第3パワーゲーティングセルを経て第4パワーゲーティングセルに伝達され、第1ないし第4パワーゲーティングセルのそれぞれは、各自のセルに入力されるモード転換信号に応答して電源供給をスイッチングする。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】トランシーバ回路30等の通信回路に接続される通信線10を構成するHライン通信線10H,Lライン通信線10L間にリンギング抑制回路1が設けられる。リンギング抑制回路1において、バイポーラトランジスタT1のエミッタはHライン通信線10Hに接続され、コレクタはLライン通信線10Lに接続され、ベースはコンデンサC1の一方電極及び抵抗R1の一端に接続され、コンデンサC1の他方電極はLライン通信線10Lに接続され、抵抗R1の他端はHライン通信線10Hに接続される。

(もっと読む)

スルーレートコントロール装置、スルーレートコントロール方法

【課題】クロック信号の出力バッファにおいて、クロック信号の周波数に応じたスルーレートの調整を行うことによりEMIノイズを抑制することが可能なスルーレートコントロール装置、およびスルーレートコントロール方法を提供すること。

【解決手段】変換ゲインGiに応じて、入力されるVCO入力電圧Viをクロック信号CKoに変換する電圧制御発振器15aを有するPLL回路24aと、VCO入力電圧Viおよび変換ゲインGiの各々に対して正の相関関係を有する制御電流Ibを出力する電圧電流変換器19aと、制御電流Ibに応じてドライブ電流を設定するバッファ制御回路21aと、ドライブ電流で、クロック信号CKoを出力する出力回路22aとを備える。よって、クロック信号CKoの周波数fに比例して出力回路22aのドライブ能力が大きくなる関係を有し、周波数fに応じて好適なスルーレートが決定することができる。

(もっと読む)

情報処理装置および情報処理装置の制御方法

【課題】通信時に発生するノイズを抑制しつつ、高速な通信を可能とする情報処理装置を提供する。

【解決手段】情報処理装置1には、2本1組の信号線7a,7bで構成される信号線対7と信号線対7に対して入力された2進数の複数ビットのデータに応じた電圧レベルに設定するためのドライバ2と、信号線対7の他端側に接続され、信号線対7の電圧レベルに応じて2進数の複数ビットのデータに変換するためのレシーバ3とが設けられる。ドライバ2は、信号線対7に電圧を印加するための定電圧源4と、2進数の複数ビットのデータに応じて信号線対の入出力インピーダンスを調整するスイッチSW6a,6bと、2進数の複数ビットのデータに応じて信号線対のそれぞれの信号線に流す電流の向きを切り替えるスイッチSW9a,SW9b,SW10a,SW10bとを含む。

(もっと読む)

差動入力バッファ

【課題】動作モード切り換え時におけるノイズを抑制する。

【解決手段】差動入力バッファ1は、動作モードを通常状態又は省電力状態のいずれかに切り換える電源回路MN1,MN2と、ソースフォロア回路を構成する半導体素子MP1,MP3及びMP2,MP4のそれぞれの寄生容量の合計である第1の寄生容量に対応する第2の寄生容量を有する半導体素子MP7,MP8により構成されるダミー回路とを有し、動作モードの切り換え時に第1の寄生容量に起因して発生する電流の流通方向と、動作モードの切り換え時に第2の寄生容量に起因して発生する電流の流通方向とが共通の配線において相反する構成を有する。

(もっと読む)

プリエンファシス電圧ジッターを減少させる装置および方法

【課題】データ送信における電圧ジッターを減少させる送信器回路を提供すること。

【解決手段】第一の電流源と、該第一の電流源と第一のノードとの間に結合されている第一のフィルタと、該第一の電流源と第二のノードとの間に結合されている第二のフィルタと、第二の電流源と、該第二の電流源と第三のノードとの間に結合されている第三のフィルタと、該第二の電流源と第四のノードとの間に結合されている第四のフィルタと、該第一のノード、該第二のノード、該第三のノードおよび該第四のノードに結合されているドライバースイッチ回路などを含む、送信器回路。

(もっと読む)

電気信号の伝送回路、IC、プリント配線板、機器およびシステム

【課題】CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制した電気信号の伝送回路を提供する。

【解決手段】本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、CMOSドライバのPMOS FET1と並列にアノード電極がドライバ出力端子につながれるように第1のダイオード6を接続し、CMOSドライバのNMOS FET2と並列にカソード電極がドライバ出力端子につながれるように第2のダイオード7を接続し、PMOS FET1のデバイストランスコンダクタンスと第1のダイオード6の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、NMOS FET2のデバイストランスコンダクタンスと第2のダイオード7の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

(もっと読む)

スキュー調整回路

【課題】

LSIの動作状態などに適合したスキューを複数の信号に与えることができるスキュー調整回路を提供する。

【解決手段】

第1及び第2の信号をそれぞれ伝播する第1及び第2の信号線と,第1及び第2の信号線を伝播する第1及び第2の信号がそれぞれ入力される第1及び第2のバッファ回路とを有する集積回路に設けられるスキュー調整回路であって,第1及び第2のバッファ回路の前段にそれぞれ設けられた第1及び第2の遅延回路と,第1及び第2の信号の間のスキューを測定するスキュー測定回路と,スキュー測定回路が測定した測定スキューに基づいて前記第1,第2の遅延回路の遅延量を決定し,当該決定した遅延量を前記第1,第2の遅延回路に設定する遅延調整回路とを有する。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

複数の集積回路にインタフェース信号を供給する方法および回路

【課題】複数の集積回路間にインタフェース信号を供給する方法を提供する。

【解決手段】第1および第2の集積回路(IC)間にインタフェース信号を発生する回路で、基準信号を供給する基準回路と、インタフェース回路と、回路要素とを含む。インタフェース回路は、第1のICに実装され、作動するように基準回路に結合し、基準信号およびデータ入力を受信し、インタフェース信号を発生する。回路要素は、第2のICに実装され、作動するように制御回路に結合し、インタフェース信号を受信し、出力信号を供給する。基準信号は、電圧あるいは電流信号であってもよく、第1あるいは第2のICで発生できる。インタフェース回路は、スイッチアレイに結合される電流ミラーで実装でき、フィルタリング要求を容易にするために過サンプリングできる。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】低コストで実現でき、小型化、低消費電力化及び高周波化に資するとともに、フリップフロップ回路の誤動作を防止するレベルシフト回路及びレベルシフト回路を用いたスイッチング電源装置を提供する。

【解決手段】それぞれ一端がレベルシフト電源に接続された抵抗R1、R2と、抵抗R1の他端にドレインが接続されたトランジスタMN3と、抵抗R2の他端にドレインが接続されたトランジスタMN4と、入力信号に基づいてトランジスタMN3,MN4のオン/オフを制御するパルス発生回路10と、トランジスタMN3がオンである場合にセット信号、トランジスタMN4がオンである場合にリセット信号を生成する制御部と、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12とを備える。

(もっと読む)

供給ノイズおよび終端ノイズの低減方法およびシステム

【課題】 SSNに関連する問題を軽減するシステムおよび方法を提供すること。

【解決手段】 シングルエンドの通信チャネルを介して第1の集積回路(IC)が第2のICと通信する通信システムを開示する。双方向基準チャネルは、第1のICおよび第2のIC間に延在し、両エンドで終端される。基準チャネルの各エンドにおける終端インピーダンスは、信号を異なる方向に通信するための異なるモードをサポートする。基準チャネルの終端インピーダンスは、それぞれの信号方向に最適化されることができる。

(もっと読む)

シリアル出力回路、半導体装置およびシリアル伝送方法

【課題】 高速シリアル伝送で使用するデエンファシスを備えた出力回路において、出力振幅で発生するコモンモード電位の変動を抑制する回路を提供する。

【解決手段】 デエンファシスを備える差動伝送のシリアル伝送装置の出力回路のP極とN極とに、送信するデータのパターンの検出装置と送信するデータの反転パターンの検出装置の出力とをそれぞれ差動入力とする、差動回路の出力を接続する。接続される差動回路によって、特定の送信するデータのパターンおよびその反転パターンの出現時に出力回路の電流が補われ、コモンモードノイズを防ぐことができる。

(もっと読む)

半導体集積回路

【課題】広い周波数範囲で高調波電流成分を削減して高周波ノイズを低減することのできる半導体集積回路の提供を図る。

【解決手段】クロック信号CKに同期して動作する複数のデジタル回路11,12を含む半導体集積回路であって、前記各デジタル回路は、周波数が同じで位相が異なる第1および第2クロック信号CKa,CKbの一方を受け取り、前記第1および第2クロック信号の位相差は、m,nを自然数として、ほぼ[2m−1]/2nであるように構成する。

(もっと読む)

電子回路

【課題】 充電回路の動作を安定化させる。

【解決手段】 充電回路(100)は、第1出力信号を出力するTr制御回路(24)と、第1出力信号が入力されて動作するトランジスタ(Tr)及びコンデンサ(C1)と、その状態を検出し、その結果としての第2出力信号を出力するコンパレータ(21)と、第2出力信号に基づいて、Tr制御回路をして前記第1出力信号を出力させるかどうかを決定する第3出力信号をTr制御回路に供給するフリップフロップ(24)と、を備え、フリップフロップの入出力特性の遷移帯は、Tr制御回路の入出力特性の遷移帯と重ならない。

(もっと読む)

半導体チップ及び半導体チップを搭載する半導体装置

【課題】入力回路を、所望の期間にわたって、常時活性化させること。

【解決手段】本発明に係る半導体チップ1は、複数のパッドと、パッドと電気的に接続される入力回路又は出力回路と、外部回路又は内部回路からの信号の読み出しを制御するリードアクセス信号を出力する主制御部と、リードアクセス信号に基づいて、外部回路又は内部回路から信号が印加されるパッドと電気的に接続される入力回路又は出力回路の活性化を制御する活性化制御部と、を備える。

(もっと読む)

低位相雑音増幅回路

【課題】低い位相雑音の増幅回路を提供する。

【解決手段】増幅回路には、第1のカレント・ミラーのダイオード接続されたトランジスタに並列に接続され且つ差動対の第1のトランジスタにインバータの形態で接続された、第2タイプの導電性をもつ第1の相補形トランジスタが含まれ、第1の相補形トランジスタのゲートまたはベースが差動対の第1のトランジスタのゲートまたはベースに接続され、さらに前記増幅回路には、第2のカレント・ミラーのダイオード接続されたトランジスタに並列に接続され且つ差動対の第2のトランジスタにインバータの形態で接続された、第2タイプの導電性をもつ第2の相補形トランジスタが含まれ、第2の相補形トランジスタのゲートまたはベースが差動対の第2のトランジスタのゲートまたはベースに接続される。

(もっと読む)

半導体装置

【課題】装置の使用中にタイミングマージンを最適化可能な半導体装置を提供する。

【解決手段】入力クロック信号の位相の遅延角度と遅延素子の段数との関係を示す遅延素子段数信号を出力するマスタDLL回路101と、遅延素子段数信号に基づいて、位相制御信号を生成する位相制御回路102と、位相制御信号に基づいて、クロック信号の位相を所定角度分シフトさせたクロック信号を出力するスレーブDLL回路103と、スレーブDLL回路から出力されたクロック信号に同期したデータ信号を生成するデータ信号生成回路111と、遅延素子段数信号、又はマスタDLL回路のロックアップ時間を示すロックアップ時間信号に基づいて、データ信号のスルーレートを制御するための制御信号を生成するスルーレート制御回路121と、スルーレート制御信号に基づいて、データ信号のスルーレートを制御するデータ信号出力回路112とを備える。

(もっと読む)

出力バッファ回路

【課題】出力バッファ回路の出力ノイズを低減し、かつ、応答速度を速くする。

【解決手段】出力電圧VOUTが接地電圧VSSからNORの反転電圧VLに変化する場合、及び、電源電圧VDDからNANDの反転電圧VHに変化する場合、2個のMOSトランジスタの両方が出力電圧VOUTを制御するので、出力電圧VOUTのスルーレートが急峻になる。よって、出力バッファ回路の応答速度が速くなる。また、出力電圧VOUTが電圧(VDD/2)付近で変化する上記以外の場合、1個のMOSトランジスタだけが出力電圧VOUTを制御するので、出力電圧VOUTのスルーレートが緩やかになる。よって、出力バッファ回路の応答速度が遅くなるので、出力ノイズが低減する。

(もっと読む)

1 - 20 / 68

[ Back to top ]