Fターム[5J056BB25]の内容

Fターム[5J056BB25]に分類される特許

1 - 20 / 53

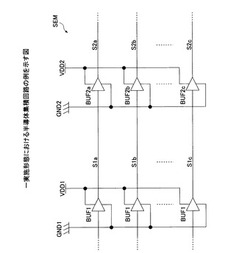

半導体集積回路、半導体集積回路の制御方法

半導体集積回路

【課題】 複数のバッファに供給される信号が同時に同じレベルに変化するときに発生する電源ノイズを低減する。

【解決手段】 半導体集積回路は、動作モードに応じて信号を互いに同期してまたは非同期に出力する複数の第1バッファと、複数の第1バッファから出力される信号をそれぞれ受け、伝搬遅延時間が互いに異なる複数の第2バッファとを有している。

(もっと読む)

出力回路、信号伝送回路及び信号伝送方法

【課題】電源ノイズの低減を図ることができる出力回路を提供する。

【解決手段】本発明の実施の形態に係る出力回路Oは、論理信号を出力するCMOS回路OAと、CMOS回路OAと同じ論理信号を出力する、CMOS回路OAと並列に設けられた電流一定回路OBと、入力される選択信号Sに応じて、CMOS回路OAと電流一定回路OBのいずれか一方にデータDを入力し、データDに応じた論理信号を出力させる選択回路SLとを備え、電源ノイズを許容値以下に抑える必要がある場合に、電流一定回路OBを選択する。

(もっと読む)

補償装置および試験装置

【課題】消費電力を抑制する。

【解決手段】電源装置から印加された電源電圧により動作する対象回路の消費電流を補償する補償装置であって、電源装置から対象回路へと電源電圧を供給するための電源配線に接続され、電源配線に流れる電流を消費する電流消費部と、電流消費部に印加される電源電圧に応じて電流消費部により消費される電流を変化させる電流制御部と、電流消費部の基準電流量を変更する設定部と、を備え、設定部は、対象回路がスタンバイ状態において、基準電流量を低減する補償装置を提供する。

(もっと読む)

半導体集積回路及びその電源制御方法

【課題】電源遮断状態からの復帰の際に、周辺回路の動作に影響を与えない半導体集積回路及び電源制御方法が、望まれる。

【解決手段】半導体集積回路は、第1及び第2の電源線と、サブ電源線と、第1の電源線とサブ電源線との間に配置される第1のスイッチ回路と、第2の電源線とサブ電源線との間に配置される論理回路と、第1の端子が第1の電源線と接続される容量素子と、容量素子の第1の端子の他方の第2の端子の接続を、第1の電源線、又は、サブ電源線、のいずれかに切り替える第2のスイッチ回路と、論理回路を非活性化状態から活性化状態に遷移させる場合に、第1のスイッチ回路により、第1の電源線及びサブ電源線の接続を遮断しつつ、第2のスイッチ回路により、第2の端子の接続を少なくても1回以上、サブ電源線に接続した後、第1の電源線に接続する制御回路と、を備えている。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

電源回路

【課題】本発明は、電源回路を提供することを目的とする。

【解決手段】本発明の電源回路は、複数のロードに電力を供給するために用いられ、複数の制御端を有する制御回路、第一電力供給回路、第二電力供給回路及び第三電力供給回路を備え、各々の電力供給回路は、それぞれ制御回路の1つの制御端に接続され、各々の電力供給回路は、全てスイッチングユニットを備え、スイッチングユニットは、第一端、第二端、第一端と第二端との間の接続及び切断を制御するスイッチング端を備え、第一端は、電源に接続され、第二端は、1つのロードに接続され、スイッチング端は、制御端に接続され、第二電力供給回路及び第三電力供給回路は、全て遅延回路をさらに備え、遅延回路は、制御回路の制御端とスイッチングユニットのスイッチング端との間に接続され、第三電力供給回路の遅延回路の遅延時間は、第二電力供給回路の遅延回路の遅延時間より大きい。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

差動出力バッファ

【課題】送信状態とスタンバイ状態との間の遷移時間の増大を抑制しつつ、電流の変動を低減する。

【解決手段】メインドライバ1は、差動信号PREP、PRENのレベル変換を行い、バイパス回路2は、メインドライバ1の動作状態とスタンバイ状態との間の遷移時に高電源電位VDDから低電源電位VSSに流れる電流I5の変化量が一定の範囲内に収まるようにメインドライバ1に流れる電流I5をバイパスさせる。

(もっと読む)

反転電圧出力回路

【課題】入力信号の変化に応じて直流電源の非接地電圧と接地電圧の間で反転する電圧を出力する回路であり、非接地端子に接続されている電源線に生じる電圧変動を抑制する。

【解決手段】電流制限素子14とスイッチング回路16が直列に接続されており、電流制限素子とスイッチング回路の中間点22の電圧を出力する。スイッチング回路の導通時にスイッチング回路を流れる電流が電流制限素子によって制限される。直流電源の非接地端子に接続されている電源線12に生じる電圧変動が抑制され、電源線12に接続されているアナログ回路等の動作が安定する。

(もっと読む)

半導体装置

【課題】出力バッファを制御する制御回路部において発生する電源ノイズを低減する。

【解決手段】データ出力端子14を駆動する単位バッファ501〜507と、単位バッファ501〜507を制御するインピーダンス制御回路511〜513と、インピーダンス制御回路511〜513を制御する制御回路部400とを備える。インピーダンス制御回路511〜513と制御回路部400は互いに異なる電源によって動作し、制御回路部400は、互いに逆相であるプルアップデータ及びプルダウンデータをインピーダンス制御回路511〜513に供給し、インピーダンス制御回路511〜513は、逆相であるプルアップデータ及びプルダウンデータを同相に変換して単位バッファ501〜507に供給する。これにより、制御回路部400にて使用する電源VDDにノイズが生じにくくなる。

(もっと読む)

半導体集積回路

【課題】 内部回路の内部ノードが初期状態に設定されたことを精度よく検出し、内部回路が動作を開始するまでの復帰時間を短縮する。

【解決手段】 第1電源スイッチは、内部電源電圧を受けて動作する内部回路の動作を開始させるための第1電源オン信号の活性化中に、外部電源線を内部電源電圧が供給される内部電源線に接続する。第2電源スイッチは、第2電源オン信号の活性化中に、外部電源線を内部電源線に接続する。検知部は、第1電源スイッチのオンにより上昇する内部電源電圧を受けて動作する回路を含む。検知部は、内部電源電圧が第1電圧を超えることにより、内部回路の内部ノードが初期状態に設定されたことを検出したときに第2電源オン信号を活性化する。

(もっと読む)

スキュー調整回路およびスキュー調整方法

【課題】

LSIの動作状態などに適合したスキューを複数の信号に与えることができるスキュー調整回路を提供する。

【解決手段】

集積回路装置内に設けられ,複数の信号をそれぞれ伝播する複数の信号線と,前記複数の信号線を伝播する複数の信号がそれぞれ入力される複数のバッファ回路と,前記複数のバッファ回路の前段にそれぞれ設けられた複数の遅延回路と,前記複数の信号線の信号変化を監視する監視回路と,前記監視回路の監視結果出力に基づいて前記複数の遅延回路の遅延量を決定し前記複数の遅延回路に設定する遅延調整回路とを含み,前記監視回路は,監視期間内において信号変化が生じた信号線の数である信号変化本数を前記監視結果として検出し,前記遅延調整回路は,前記信号変化本数に基づいて前記遅延量を決定するスキュー調整回路。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

半導体集積回路

【課題】半導体集積回路のチップ面積とコストの増加や、電気的特性の問題を招くことなく、出力バッファ回路の出力電圧のリンギングを抑制する。

【解決手段】半導体集積回路200は、電源線10、電源抵抗11、接地線12、接地抵抗13、出力バッファ回路14,15,16、電源端子PVdd、接地端子PVss、出力端子PO1,PO2,PO3、及びリード端子17,18を含んで構成される。電源抵抗11は、電源線10と出力バッファ回路14の電源電位入力端との接続点N1と電源端子PVddとの間に接続されている。接地抵抗13は、接地線12と出力バッファ回路14の接地電位入力端との接続点N4と接地端子PVssとの間に接続されている。

(もっと読む)

情報処理装置

【課題】 電源遮断機能を有するLSIにおいて、電源遮断をオンオフするときにリーク電流による電流が急激に変化すると電源線にノイズを生ずる。

【解決手段】 情報処理装置であって、回路ブロックと、前記回路ブロックに電源を供給するためのローカル電源線と、電源線と、前記電源線と前記ローカル電源線の間にそのソース―ドレイン経路が設けられる第1のトランジスタとを有し、前記第1のトランジスタは、第1の状態においてはオフ状態に制御され、第2の状態においてはオン状態に制御され、前記第1の状態から前記第2の状態に移行する際に、前記第1のトランジスタは、前記第1のトランジスタのソース―ドレイン経路を流れる電流の変化率が、所定の値を超えないように制御されることを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】スリープ状態の論理回路ブロックにおける寄生容量を用いることにより、電源共振雑音などの電源ノイズを大幅に低減する。

【解決手段】電源ノイズ測定回路9によって電源電圧VDDをモニタし、電源電圧VDDが任意の基準電圧以上となると、制御信号CONを出力し、スイッチコントローラ8は、仮想基準電位VSSAに蓄積された電荷を放出し、その後、任意の期間が経過すると、仮想基準電位VSSAに電荷を蓄積するようにスイッチ部6を制御することによって、基準電位VSS、および電源電圧VDDの電位を下降/上昇させ、電源電圧VDDの電源共振雑音をキャンセルする。

(もっと読む)

半導体装置及び電源スイッチ回路

【課題】電源スイッチがオフからオンの状態に遷移するときの突入電流を防ぐことにより電源スイッチオンに起因する電源ノイズの発生を防止する半導体装置及び電源スイッチ回路を提供する。

【解決手段】電源スイッチ回路が、ソースが第1の電源にドレインが前記機能回路に接続された電源スイッチトランジスタと、電源スイッチトランジスタのオンオフを制御する制御信号を入力とし、電源スイッチトランジスタのドレインと、ソースと、ゲートとにそれぞれ接続され制御信号に基づいて電源スイッチトランジスタをオフからオンの状態にスイッチさせるとき、電源スイッチトランジスタのソースドレイン間電圧が小さくなるほど電源スイッチトランジスタのソースゲート間電圧が大きくなるように電源スイッチトランジスタのゲート電圧を制御する電源スイッチトランジスタ制御回路と、を備える。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路は、データの送信を精度良く行うことができないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、複数の信号線を介してパラレルに送信データを送信するSoC回路100と、送信データを受信するSDRAM回路101と、を備える。SoC回路100は、各信号線に対して設けられ、送信データを出力するためのデータ送信モードと、出力をハイインピーダンスにするためのハイインピーダンスモードと、が切り替わる複数のデータ出力回路203と、データ出力回路203に対して、送信データと予め設定された固定データとのいずれかを選択して出力するデータ選択回路256と、各データ出力回路203において、ハイインピーダンスモードからデータ送信モードへモードが切り替わってから実際に送信データの出力を開始するまでの間、固定データを出力するように制御する制御回路205と、を備える。

(もっと読む)

半導体集積回路

【課題】回路部が停止状態から動作状態に移行するときに、チップ内電源に対する電圧降下を低減すること。

【解決手段】動作期間T10で、回路部210内の寄生容量221の電位とデカップリング容量220の電位は、チップ内電源201の電位に維持され、停止期間T11で、寄生容量221の電位は徐々に降下してゼロになり、デカップリング容量220の電位はチップ内電源201の電位に維持される。移行期間T12〜T14で、デカップリング容量220の電位が第2スイッチSW2を介して寄生容量221に充電され、デカップリング容量220の電位は徐々に降下し、寄生容量221の電位は徐々に上昇していく。移行期間T12〜T14で、回路部210の電位がゼロの状態であるときに、回路部210が第1スイッチSW1を介してチップ内電源201と接続しないようにすることで、チップ内電源201に対する電圧降下を低減することができる。

(もっと読む)

1 - 20 / 53

[ Back to top ]