Fターム[5J056BB40]の内容

Fターム[5J056BB40]に分類される特許

1 - 20 / 145

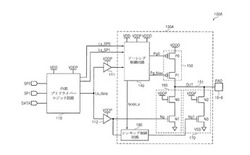

出力バッファ回路の動作方法、その動作方法を用いる出力バッファ回路、その出力バッファ回路を含むシステムオンチップ、及びその出力バッファ回路を含む携帯用データ処理装置。

【課題】 供給電圧または動作電圧に無関係に信頼性を保証可能な出力バッファ回路の動作方法を提供する。

【解決手段】 出力バッファ回路130Aのソーシング制御回路140は、DCレベルを指示する指示信号に基づいて第1ソーシング制御信号Pg0を生成する。ソーシング制御回路140は、指示信号に基づいて第2ソーシング制御信号Pg_biasを生成する。ソーシング回路150は、第1ソーシング制御信号Pg0と第2ソーシング制御信号Pg_biasとに応じて第1電圧VDDOを出力端子151に供給する。第1シンキング回路160は、第2バッファ112から出力されたデータNgのレベルに基づいて出力端子151に接地電圧VSSを供給する。これにより、メインドライバーとして使われるPMOSトランジスタP0、P1のゲート酸化物の信頼性を保証しながら、高速で出力データをバッファリングすることができる。

(もっと読む)

論理回路、半導体集積回路

【課題】供給される電源電圧の変動を抑制することができる論理回路及び当該論理回路が搭載される半導体集積回路を提供すること。

【解決手段】本発明の一態様であるバッファ回路100は、バッファ部11、電圧検出部12及びスイッチ部13を有する。バッファ部11は、電源端子Ts1又は電圧レギュレータ1と電源端子Ts2との間に接続されることにより電源供給され、入力信号INと同論理の信号を出力端子Toutへ出力する。電圧検出部12は、出力端子Toutの電圧を検出し、検出結果に基づく検出信号Sdetを出力する。スイッチ部13は、検出信号Sdetに応じて、バッファ部11を電源端子Ts1又は電圧レギュレータ1と接続する。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

レベルシフト回路

【課題】レベルシフト基準電位が下がった場合にスイッチング素子を安全且つ確実に停止できるレベルシフト回路。

【解決手段】レベルシフト電源に接続された抵抗R1にドレインが接続されソースがグランドに接続されたMOSFETMN3、R1と同じ抵抗値を有しレベルシフト電源に接続された抵抗R2にドレインが接続されソースがグランドに接続されたMOSFETMN4、入力信号に基づきMN3,MN4のオン/オフを制御するパルス生成回路10、MN3がオンである場合にセット信号を生成しMN4がオンである場合にリセット信号を生成する制御部MN1,MN2,R5,R6、制御部で生成されたセット信号とリセット信号とに基づき入力信号をレベルシフトした出力信号を出力しスイッチング素子Q1を動作させるフリップフロップFF1、レベルシフト基準電位が負電位に下がったことを検出してスイッチング素子を停止させるスイッチング動作停止部INV3,FF2,AD1を備える。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを出力する電圧出力回路100と、制御信号SCに基づいて電圧出力回路100を制御する制御回路210と、第1の電源電圧VP及び第2の電源電圧VMに基づいて制御信号SCを生成して制御回路210に出力する制御信号生成回路240とを含み、制御回路210は、制御信号SCに基づいて、電圧出力回路100から出力される第1の電源電圧VP及び第2の電源電圧VMの振幅を可変に制御する。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを共振により出力する電圧出力回路100と、電圧出力回路100の発振を制御する発振制御回路210とを含む。発振制御回路210は、第1の電源電圧VPが出力されるノード及び第2の電源電圧VMが出力されるノードのいずれか一方のノードである第1のノードN1に接続される駆動回路220と、駆動回路220を制御する制御回路230とを含む。発振制御回路210は、制御信号SCに基づいて、第1、第2の電源電圧VP、VMの振幅を可変に制御する発振制御を行う。

(もっと読む)

イネーブル信号生成回路

【課題】後段のイネーブル回路を確実に制御し、また電源電圧が高くなっても消費電流が増大しないようにする。

【解決手段】制御入力端子1にゲートが接続されソースがトランジスタMN2を介して接地に接続されたトランジスタMN1と、トランジスタMN1のドレインと電源VDDとの間に接続された抵抗R2と、抵抗R2の両端にソースとドレインが接続されたトランジスタMP1と、トランジスタのMP1ゲートとソース間に接続された抵抗R3と、ソースがトランジスタMP1のゲートに接続されゲートがトランジスタMP1のドレインに接続されドレインが負荷回路3に接続されたトランジスタMP2とを備え、トランジスタMP2のゲートを制御出力端子2に接続した。

(もっと読む)

半導体装置

【課題】処理実行中に電源をオフしてもデータが保持され、且つ従来よりも占有面積が小さいDフリップフロップ回路を有する半導体装置を提供する。

【解決手段】入力端子が、第1のトランスミッションゲートの第1の端子に電気的に接続され、第1のトランスミッションゲートの第2の端子が、第1のインバータの第1の端子及び機能回路の第2の端子に電気的に接続され、第1のインバータの第2の端子及び機能回路の第1の端子が、第2のトランスミッションゲートの第1の端子に電気的に接続され、第2のトランスミッションゲートの第2の端子が第2のインバータの第1の端子及びクロックドインバータの第2の端子に電気的に接続され、第2のインバータの第2の端子及びクロックドインバータの第1の端子は出力端子に電気的に接続されており、機能回路にはオフ電流が小さいトランジスタと容量素子との間にデータ保持部を有する半導体装置とする。

(もっと読む)

出力インタフェース回路

【課題】多量の電流が消費されるのを防止しつつ、電源電圧の変動を抑制することができる出力インタフェース回路を提供する。

【解決手段】第1のトランジスタTr1は、電源とグランドとの間に設けられ、制御電極が第1のノードに接続される。第1のキャパシタ43は、第1のノードBとグランドとの間に設けられる。制御用バッファ41は、出力バッファ110と同じタイミングで外部から入力されたデータの各ビットを受け、出力が第1のノードBに接続される。第2のトランジスタTr2は、電源とグランドとの間に設けられ、制御電極が第2のノードCに接続される。第2のキャパシタ44は、第2のノードCとグランドとの間に設けられる。制御用インバータ42は、出力バッファ110と同じタイミングで外部から入力されたデータの各ビットを受け、出力が第2のノードCに接続される。

(もっと読む)

出力バッファ回路及び入出力バッファ回路

【課題】流入電流の発生を抑制することができる出力バッファ回路を提供する。

【解決手段】出力バッファ回路1は、第1の高電位電源VDD1レベル又は低電位電源VSSレベルの出力信号OUT1を出力する第1出力回路10と、第1出力回路10とワイヤードオア接続され、第1の高電位電源VDD1よりも低電位である第2の高電位電源VDD2レベル又は低電位電源VSSレベルの出力信号OUT2を出力する第2出力回路20とを有している。また、出力バッファ回路1は、第1の高電位電源VDD1及び第2の高電位電源VDD2のうち第2の高電位電源VDD2のみが投入される場合に、第1出力回路10の高電位側の第1出力トランジスタT16及び第2出力回路20の高電位側の第2出力トランジスタT26の少なくとも一方のトランジスタのゲート電圧及びバックゲート電圧を第2の高電位電源VDD2レベルに設定する制御回路50を有している。

(もっと読む)

レベル生成回路

【課題】 耐圧の低いMOSFETを保護するためにゲート接地として動作する、MOSFETのゲート電圧を生成するための外部電源を不要にする。

【解決手段】 第1電源電圧から一定の大きさの第1電流を生成する定電流生成部と、第1薄膜NMOSFETと第2薄膜NMOSFETから構成され、第1電流に比例した大きさの第2電流を出力する第1カレントミラー回路部と、第2薄膜NMOSFETを保護するためにゲート接地として用いる第3薄膜NMOSFET及び第1厚膜PMOSFETと、第1電源への電流の逆流を防ぐための第1ダイオードと、第3薄膜NMOSFETのゲート−ソース間電圧がマイナスになることを防ぐための第2ダイオードとからなる保護回路部と、第2電流に比例した大きさの第3電流を出力する第2カレントミラー回路部と、第3電流により第1定電圧を生成する第1ツェナーダイオード部とを備える。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

信号伝達回路及びこれを用いたスイッチ駆動装置

【課題】入力信号をレベルシフトして出力するレベルシフト回路を有しながらも、電源の電圧変動等による誤信号の出力を抑えることが可能となる信号伝達回路を提供する。

【解決手段】第1入力信号および第2入力信号の各々をレベルシフトし、それぞれ第1シフト済み信号および第2シフト済み信号として出力する、レベルシフト回路を備え、レベルシフト回路は、第1入力信号に応じて開閉するスイッチング素子と抵抗を有する第1直列回路、および、第2入力信号に応じて開閉するスイッチング素子と抵抗を有する第2直列回路が、電源と接地端との間において互いに並列に設けられており、第1直列回路上の電圧を第1シフト済み信号として、第2直列回路上の電圧を第2シフト済み信号として、それぞれ出力するようになっており、接地端から第1直列回路および第2直列回路に向かって逆電流が流れることを防止する、逆流防止部を備えた信号伝達回路とする。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

半導体出力回路及び外部出力信号生成方法並びに半導体装置

【課題】電源電圧の低下による外部出力信号のばらつきを抑制する。

【解決手段】内部入力信号Aの電位がグランド側からVDD側、あるいはVDD側からグランド側へ変化するのに応じて、出力部1は外部出力信号EBの電位を変化させる。差動部2は、外部出力信号EBと、所定の基準信号VREFとに応じた出力信号を出力し、外部出力信号EBが所定の基準信号VREFに応じた電位となるようボルテージフォロアとして機能する。これにより、外部出力信号EBの低電圧側出力電圧VOLのばらつきを抑制する。

(もっと読む)

差動出力回路

【課題】ゲート電圧に対する遅延調整を行わずに、クロスポイントの変動を抑えること。

【解決手段】駆動部100と出力部101は、カレントミラー構成により、プロセス、電圧、温度条件が変動しても共に同一の変動となるため、入力信号INTの信号レベルが“H”から“L”に切り替わる際、MOSFET3、6がオンしているときに、MOSFET5、4がオフ状態からオン状態に速く切り替わることはない。従って、クロスポイントの変動を抑えることができる。また、この構成により、ゲート電圧PL、PR、NL、NRは、電源電圧VSSからVDDまでフルスイングされないため、MOSFET3、6をオンさせ、MOSFET5、4をオフさせる場合、ゲート電圧PLの立ち下がりに対してゲート電圧NLの立ち下がりに遅延をもたせたり、ゲート電圧NRの立ち上がりに対してゲート電圧PRの立ち上がりに遅延をもたせたりする必要がない。

(もっと読む)

キャリブレーション回路および半導体装置に関する。

【課題】出力バッファのI−V特性が出力バッファ用の電源電圧に応じて変化しても、出力バッファのI−V特性に対して規定を満足させることを可能にする。

【解決手段】レプリカ回路(110、120、130)は、インピーダンスが可変であり、当該インピーダンスに応じた電圧を出力する。参照電圧生成部(141、142)は、出力バッファ用の電源電圧に依存する参照電圧を出力する。比較部(151、152)は、レプリカ回路の出力電圧と参照電圧とを比較する。調整部(160、170、180、191、192、110a、120a、130a)は、比較部の比較結果に応じて、レプリカ回路のインピーダンスを調整する調整部(160、170、180、191、192、110a、120a、130a)。

(もっと読む)

半導体装置

【課題】データ出力タイミングの設計を簡略化出来る半導体装置を提供すること。

【解決手段】第1クロックCLKに同期してデータを連続的に出力する半導体装置であって、外部から与えられる前記第1クロックCLKから第2クロックICLKを生成するクロック生成回路50、51と、前記第2クロックICLKに同期して動作し、前記データが入力されるフリップフロップ回路52と、前記フリップフロップ回路52から出力される前記データを外部へ出力する出力バッファ回路54と、バンドギャップリファレンス回路22を含み、該バンドギャップリファレンス回路22により制御される電圧VBGRを発生し、該電圧VBGRを前記クロック生成回路50、51、前記フリップフロップ回路52及び前記出力バッファ回路54へ電源電圧として供給する電源回路とを備える。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスからの検出信号の精度の高いA/D変換を実現できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、電源電圧VDDAを生成する電源回路60と、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAに基づいて動作し、電源電圧VDDAにより規定されるA/D変換範囲で、センサーデバイス30からの検出信号に対応する信号についてのA/D変換を行うA/D変換器ADCと、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAをセンサーデバイス30に供給する電源端子PVDAを含む。

(もっと読む)

1 - 20 / 145

[ Back to top ]