Fターム[5J055AX31]の内容

Fターム[5J055AX31]の下位に属するFターム

スイッチ素子の保護 (499)

通常動作時の監視、モニタによる故障検出 (52)

Fターム[5J055AX31]に分類される特許

1 - 20 / 22

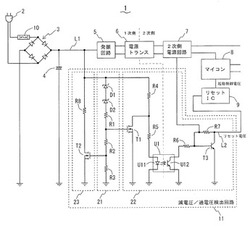

電子機器装置

【課題】電子機器装置において、減電圧状態になった場合及び過電圧状態になった場合に、より確実に回路を保護する。

【解決手段】電子機器装置1は、第1の規定電圧値以下の電圧が電子機器装置1に供給される減電圧状態になった場合に、マイコン8をリセットさせ、第2の規定電圧値以上の電圧が電子機器装置1に供給される過電圧状態になった場合に、ヒューズ10を溶断させる減電圧/過電圧検出回路11を備える。減電圧/過電圧検出回路11は、平滑用のコンデンサ4により平滑化された電圧(1次側電圧出力ラインL1から出力された電圧)を監視し、平滑用のコンデンサ4により平滑化された電圧に基いて、減電圧状態、及び過電圧状態を検出する。そして、減電圧/過電圧検出回路11は、過電圧状態を検出した場合には、マイコン8をリセットさせ、過電圧状態を検出した場合には、ヒューズ10を溶断させる。

(もっと読む)

半導体スイッチの制御装置

【課題】半導体スイッチ素子に並列に接続される保護回路の異常を検出できる半導体スイッチ素子の制御回路を得る。

【解決手段】半導体スイッチに印加される電圧を抑制するために半導体スイッチに並列に接続された保護回路と、駆動回路の出力ゲート電圧が予め設定された電圧以上あることを検出し、半導体スイッチのオン・オフ状態を判別するゲート電圧検出手段と、半導体スイッチの主端子電圧を検出する主電圧検出手段と、駆動回路に与えられた駆動信号により、駆動指令がオン指令の場合はゲート電圧状態を選択し、駆動指令がオフ指令の場合は主電圧状態を選択する選択手段と、選択手段の出力を絶縁して低圧回路に伝達する第一の信号絶縁手段と、選択手段が選択して出力したゲート電圧状態・主電圧状態と半導体スイッチの駆動指令とを比較し、半導体スイッチの正常又は異常を判別する判別手段とを備える。

(もっと読む)

機器の修理方法および修理用基板

【課題】入手困難なリレーを複数使用した制御基板のいずれかのリレーが故障すると、通常であれば制御基板を新たな制御基板と交換することによって修理を行うが、1個のリレーが故障しただけで、すべてのリレーを交換することになり、リレーの入手が困難なため修理自体が困難になるという問題が生じる。

【解決手段】故障したリレーの代わりとして機能する修理用リレーを備えた修理用基板を検査用コネクタに接続し、故障したリレーへのオンオフ指令を常時監視して、故障したリレーに対するオンオフ指令に連動して修理用リレーをオンオフさせるようにした。

(もっと読む)

電力制御器システム

【課題】落雷などの故障過渡電流が流れる間はスイッチング装置を開いて過電流が流れるのを防止する一方、その間、負荷電流が中断されない電力制御器システムを提供する。

【解決手段】電力制御器システム10は、電気経路31内に設けられた、負荷20に電流を供給するスイッチング装置30を備える。スイッチング装置30の両端間の電圧または電流が所定のレベルを超えたとき、制御器50がスイッチング装置10を開くように構成する。スイッチング装置30が開いているときも、並列電気経路60を負荷に接続する回路11内の誘導素子32に蓄積された誘導エネルギーの放散により、負荷電流61が並列電気経路60および負荷20に流れ続ける。

(もっと読む)

駆動回路及び表示装置

【課題】高圧側オペアンプ及び低圧側オペアンプのいずれかに過電流が発生することを防止できる駆動回路を提供する。

【解決手段】駆動回路は、高圧側オペアンプ37B、低圧側オペアンプ37A及びスイッチ回路381を備える。高圧側オペアンプ37Bは、VMM電源ラインに接続されたアノードと高圧側オペアンプ37Bの出力端子NBに接続されたカソードとを有する寄生ダイオード70と、スイッチ回路381により出力端子NBの接続先がデータ線31Bからデータ線31Aに切り替えられるときに、寄生ダイオード70のアノードを電源電圧VMMよりも低い電圧VSSを供給する第1の電圧供給ラインに接続する保護スイッチ回路62とを含む。

(もっと読む)

エレベータ制御用半導体リレー装置

【課題】スイッチング動作に際して音を発生するエレベータ制御用半導体リレー装置を提供する。

【解決手段】一対の出力側端子と、出力端子に出力段が接続され、出力端子間をオン/オフ状態間で切り換える半導体スイッチング手段と、一対の入力側端子に入力される切換指示入力信号が出力端子間をオンまたはオフ状態のいずれに切り換える信号であるのかを判定する入力判定手段と、判定された結果に応じた出力切換制御信号を半導体スイッチング手段に伝達する出力切換制御手段とを備える。また、判定された結果に基づいて可聴音の出力を指示する音出力指示手段と、指示に応じて、可聴音に対応する電気信号である音響信号を出力する音響信号出力手段と、出力された音響信号を音波に変換する電気/音波変換手段とを備える。

(もっと読む)

送受信モジュール

【課題】大きなパルス幅を有する大電力の高周波信号が入力された場合であっても、リミタ回路および受信回路の増幅器が破壊されることを抑制することができる送受信モジュールを提供する。

【解決手段】アンテナ11と、リミタ回路16および受信系電力増幅器17を備えた受信回路14と、送信系電力増幅器20を備えた送信回路15とが、送受信切替スイッチ13により接続され、アンテナ11と送受信切替スイッチ13の間に設けられた検波回路12により、送受信切替スイッチ13を制御する制御信号を生成する。送受信切替スイッチ13は、制御信号が入力されない状態ではアンテナ11と受信回路14とを導通させ、制御信号が入力されるとアンテナ11と送信回路15とを導通させる。制御信号は、送受信切替スイッチ13に信号が入力された時から、リミタ回路16の熱時定数よりも短い時間までの間に送受信切替スイッチ13に入力される。

(もっと読む)

短絡検出回路

【課題】本発明は、コストアップや電力損失を招くことなく、プッシュプル回路の出力短絡を検出することが可能な短絡検出回路を提供することを目的とする。

【解決手段】本発明に係る短絡検出回路は、パルス信号Vxと同期したダミーパルス信号Vyを生成し、両信号間に所定の位相差が生じているか否かに応じて、OUT1P端子の短絡検出を行う構成とされている。

(もっと読む)

耐放射線性のための回路アーキテクチャ

【課題】総線量の電離放射線又はバイアス効果によって引き起こされるデバイス特性の変化は望ましくない。

【解決手段】総線量の電離放射線及び/又はバイアスによる劣化によって引き起こされる欠陥の影響を受けやすいデバイスの動作寿命を延ばすシステム及び方法が記載される。そのデバイスは少なくとも一度だけ複製され、1つのデバイスだけが正常に動作しているように、少なくとも1つのスイッチング機構を用いて、それらのデバイス間で反復して用いられる。第1のデバイスが正常に動作しているとき、他のデバイスはバイアスをかけられる。そのバイアス条件は、総線量の電離放射線又はバイアス効果に起因して生じるデバイス変化を、遅くするか、解消するか、又はさらには逆に変化させることができる。

(もっと読む)

ヒューズ回路

【課題】従来のヒューズ回路では、ヒューズが再癒着した場合に確実に導通状態を検出できない問題があった。

【解決手段】本発明のヒューズ回路は、第1の電源ラインGNDと、第2の電源ラインVDDと、第1の電源ラインGNDと出力端子DETとの間に接続される第1の電流源11と、第2の電源ラインVDDと出力端子DETとの間に接続され第1の電流源11の電流供給能力又は電流引き抜き能力より大きな電流引き抜き能力又は電流供給能力を有する第2の電流源12と、第2の電源ラインVDDと出力端子DETとの間に第2の電流源12と直列に接続されるヒューズF1とを備えるものである。

(もっと読む)

遅延時間生成回路、それを用いた二次電池保護用半導体装置、バッテリパックおよび電子機器

【課題】高速クロックを用いることなしにテスト時間の大幅な短縮が行え、ICチップ面積の増加を抑えることが可能な遅延時間生成回路、それを用いた二次電池保護用半導体装置、バッテリパックおよび電子機器を提供すること。

【解決手段】入力されたクロック信号CLKのパルス数を計数するための縦続接続された複数のフリップフロップ回路FF1〜FFnからなるカウンタ回路12を備え、該カウンタ回路12の最終段FFnまたは所定の段のフリップフロップ回路の出力が反転した信号を遅延時間信号(Delay)として利用する遅延時間生成回路において、電子回路のテスト時に、前記カウンタ回路の最終段または前記所定の段のフリップフロップ回路より前段のフリップフロップ回路の出力信号を用いて遅延時間を生成するようにしたもので、これにより、特別な高速クロックを使用することなしに遅延時間の短縮が可能となった。

(もっと読む)

半導体素子のゲート電源供給装置

【課題】 ゲート電源自給回路で健全なゲート電源を得ることができなかったとしても半導体素子へのゲート電源を確保できる半導体素子のゲート電源供給装置を提供することである。

【解決手段】 ゲート電源自給回路12a、12b、12cは半導体素子のオフ時の電圧を分圧してコンデンサCa、Cb、Ccに電荷を蓄積し半導体素子のゲート駆動回路13a、13b、13cにゲート電圧を供給する。一方、バックアップ電源供給回路14は、半導体素子のオフ時の電圧が低下しゲート電源自給回路12a、12bのコンデンサCa、Cbにゲート電圧を維持するだけの電荷が蓄積できなくなったとき、他のゲート電源自給回路からコンデンサCa、Cbに電荷を供給する。

(もっと読む)

半導体集積回路

【課題】電源投入時にパワースイッチ回路に流れるラッシュ電流の値を高精度に設定すること。

【解決手段】LSIの内部回路Int_Cirには、パワースイッチ回路PSWCのレギュレータVRegの出力トランジスタMP1から内部電源電圧Vintが供給される。パワースイッチ回路PSWCは、制御回路CNTRLRと、起動回路STCを含む。外部電源の投入の初期期間Tintには起動回路STCは、出力トランジスタMP1の出力電流Isupが時間変化に対して略一定の増加量となるように出力トランジスタMP1を制御して、1次のラッシュ電流を低減する。起動回路STCにより制御された出力電流Isupによる負荷容量Cの充電による内部電源電圧とレギュレータVRegからの電源電圧Vintとの差ΔVを所定の範囲に設定して、2次のラッシュ電流を低減する。

(もっと読む)

車両灯具用過電圧保護回路およびこれを備える車両用灯具点灯回路

【課題】コストの増大を招くことなく、過電圧が供給されても光源の点灯状態を維持しつつ過電圧から光源を保護することができる車両灯具用過電圧保護回路を提供する。

【解決手段】車両の灯具に用いられる光源12と光源12に電力を供給する電力供給源14との間に設けられ、電力供給源14からの供給電圧が光源12の許容電圧を超える過電圧であるとき、光源12に印加される電圧を抑制して光源12を保護する車両灯具用過電圧保護回路10である。光源12に印加される電圧が過電圧となることを検知する過電圧検知手段20と、過電圧検知手段20により過電圧が検知されると光源12に供給される電流の一部を分流させるバイパス手段30と、バイパス手段30よりも電力供給源14側で電力供給源14からの供給電圧を降下させる電圧降下手段40とを備える。

(もっと読む)

携帯情報端末

【課題】 リセット動作を制限する。

【解決手段】 携帯電話1は、アプリケーションプログラムを実行可能なCPU21と、電源をオンした状態とオフした状態とに切換える指示を受付けるための電源スイッチ14Bと、電源スイッチ14Bが所定時間閉ざされると、CPU21を再起動させるためのリセット信号を出力するリセット検出回路20とを備え、CPU21は、リセット可能な状態とリセット不可能な状態とのいずれかを示す状態信号SL1を出力し、リセット検出回路20は、状態信号SL1がリセット可能な状態を示すこことを条件に、ハイの信号S4(リセット信号)をリセット回路41に出力する論理積素子27を含む。リセット回路41は、リセット検出回路20からハイの信号S4(リセット信号)が入力されると、CPU21にローの信号SL5(リセット信号)を出力する。

(もっと読む)

インターフェース回路

【課題】電源がオンの場合に、サージ等から内部回路を保護しつつ、電源がオフの場合に、接続された外部回路の電源がオンであっても、リーク電流を削減できるようにする。

【解決手段】保護回路103と電源(VDD)との間にリーク電流遮断用としてトランジスタ109を設ける。また、Highレベルの信号の出力時に外部信号用入出力端子をHighレベルにドライブするトランジスタ102と電源(VDD)との間にリーク電流遮断用としてさらに、トランジスタ110を設ける。2つのリーク電流遮断用トランジスタの各ゲート端子には、昇圧回路111によって、電源(VDD)よりも高い電圧を印加する。

(もっと読む)

絶縁ゲート型半導体素子のゲート回路

【課題】 負側電源の故障が発生しても、絶縁ゲート型半導体素子が誤オン動作しないような安全な絶縁ゲート型半導体素子のゲート回路を得る。

【解決手段】 正側電源2Aと負側電源2Bで動作し、絶縁ゲート型半導体素子3のゲート駆動を行うFET12A及びFET12Bから成るトーテムポール回路と、ゲート制御IC11と、ゲート制御ICの出力とFET12Aのゲート間に設けたツェナーダイオード15A及び抵抗14Aから成る直列回路と、ゲート制御ICの出力とFET12Bのゲート間に設けたツェナーダイオード15B及び抵抗14Bから成る直列回路とで構成し、ツェナーダイオード15Aの降伏電圧は、正側電源の電圧からFET12Aのゲートしきい値電圧を減算した値より大きく、ツェナーダイオード15Bの降伏電圧は、負側電源の電圧からFET12Bのゲートしきい値電圧を減算した値より小さく選定する。

(もっと読む)

誘導性負荷の異常検出装置

【課題】 誘導性負荷の異常検出装置を小規模化する。

【解決手段】 電磁弁を制御する装置では、電磁弁のコイルLの一端がバッテリ電圧VBに接続され、コイルLの他端がコネクタ端子3を介してソース接地のNチャネルMOSFET5のドレインに接続されている。また、FET5のドレイン・ゲート間には、カソードをドレイン側にした消弧用ツェナーダイオード13と、CPU7からFET5のゲートへの駆動信号SDがドレインへと回り込むのを防止するダイオード15とが接続されている。更に、この装置には、ツェナーダイオード13にコイルLのフライバック電圧によるツェナー電流が流れることでオンするNPNトランジスタ23が設けられており、CPU7は、FET5をオフさせるべく駆動信号SDをローレベルに変化させた時にトランジスタ23のオン/オフを示すモニタ信号SMがレベル変化しなければ、コイルLの故障と判定する。

(もっと読む)

半導体装置

【課題】一つの外部入力端子に接続される複数の入力回路を備える半導体装置を安定的に動作させる。

【解決手段】外部入力端子PADに抵抗素子R1、R2、R3、R4をそれぞれ介して接続される入力回路10、11、12、13は、それぞれ供給されるクロック信号CK10、CK11、CK12、CK13のレベル遷移に応じて活性化して入力信号を取り込む。外部入力端子PADに印加される信号を入力するために、それぞれの入力回路には、それぞれ位相の異なるクロック信号が供給される。外部入力端子に供給されるシリアルデータを位相の異なるクロック信号で順次入力回路に振り分けて入力することで一つの入力回路のサイクルタイムを長くすることができる。この時、抵抗素子R1、R2、R3、R4で各入力回路が分離されているため、各入力回路の初段で発生するキックバック信号の、他の入力回路への影響を極めて小さくすることができる。

(もっと読む)

多用途電子機器システム

【課題】 故障箇所を特定するための信号線の配線を簡易にして回路規模を小さくし、モジュールの再構築を容易にして、稼働率を向上させることができる多用途電子機器システムを提供する。

【解決手段】 モジュール2内の機能実行部を信号線で連結すると共に、モジュール2間の機能実行部を横断的に連結して全ての機能実行部をマトリクス状に信号線で接続し、当該マトリクス状の信号線をホスト1が監視することで、信号線の配置を複雑にすることなく、故障部位を検出し、更に代替可能な機能実行部を表示することでモジュール構成の再構築を容易に実現できるとする多用途電子機器システムである。

(もっと読む)

1 - 20 / 22

[ Back to top ]