Fターム[5J055AX32]の内容

Fターム[5J055AX32]の下位に属するFターム

制御端子側の保護 (8)

主端子側の保護 (290)

CMOSラッチアップ対策 (7)

Fターム[5J055AX32]に分類される特許

1 - 20 / 194

負荷駆動装置

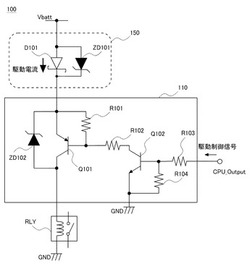

リレー装置

【課題】バッテリ逆接続でのリレー動作防止を実現するとともに、リレー回路の駆動電流経路の電圧降下を抑制する技術を提供する。

【解決手段】リレー装置100では、電源電圧VbattからグランドGNDに向けて、逆流防止回路150、リレー駆動回路110及びリレー回路RLYが直列に配置されている。逆流防止回路150は、ショットキーダイオードD101とツェナーダイオードZD101とを備えている。ショットキーダイオードD101とツェナーダイオードZD101とは並列に接続されており、順方向が同じである。

(もっと読む)

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】電源投入後から外部リセット信号が最初にアクティブになるまでの期間にリセット信号をアクティブにすることが可能なリセット信号生成回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路101は、外部リセット信号が最初にアクティブになったことを検出する外部リセット検出回路102と、外部リセット検出回路102の検出結果が、外部リセット信号が最初にアクティブになる前であることを示す場合、外部リセット信号に関わらずリセット信号をアクティブにする制御回路と、を備える。

(もっと読む)

スイッチング回路及び電源装置

【課題】 半導体スイッチが故障することを抑制することのできるスイッチング回路を提供する。

【解決手段】

電源装置1は、電流路内に配置されオン・オフ動作可能なメインFET131と、メインFET131にオン・オフ動作を行わせる制御部19と、メインFET131の温度を検出する第1サーミスタ134と、電流路内においてメインFET131と並列に配置されオン・オフ動作可能なサブFET132と、を備え、制御部19は、メインFET131の温度が所定温度を超えた場合に、オン・オフ動作を行わせるFETをメインFET131からサブFET132に切り替える。

(もっと読む)

スタック電圧耐性を高めるためのキャパシタンス調整

【課題】 印加されるRF電圧Vswに制御可能に耐えるRFスイッチ、又はこのようなスイッチの製造方法を提供する。

【解決手段】 スイッチは直列接続された構成FETのストリングを有し、このストリングのノードは隣接するFETの各対の間にある。方法は、各構成FETにわたって分布するRFスイッチ電圧の不一致を減らすよう、容量的にストリングを有効に調整すべくストリングの異なるノードの間のキャパシタンスを制御し、それによって、スイッチ・ブレイクダウン電圧を高める。キャパシタンスは、例えば、ストリングのノードの間に容量特性配置することによって、及び/又は異なる構成FETの設計パラメータを変化させることによって、制御される。各ノードについて、ノードに現れるVswの比率による各有意なキャパシタの積の和は、おおよそ零になるよう制御され得る。

(もっと読む)

半導体チップ及びこれをパッケージングした半導体装置

【課題】サージ印加時における内部回路の誤動作を防止する。

【解決手段】半導体チップ(10)は、複数のパッド(P11、P12)と、複数のパッド(P11、P12)と電源ライン(15、16)との間に接続された複数の静電破壊保護素子(11H、11L、12H、12L)と、複数のパッドのうち少なくとも2つのパッド(P11、P12)に現れる印加電圧(S11、S12)が同一の論理レベルか否かを監視するサージ検出部(13)と、サージ検出部(13)の検出結果(S13)に応じてその動作が許可/禁止される内部回路(14)と、を有する。

(もっと読む)

スイッチング電源装置

【課題】大型化することなく、アーム短絡および損失増大の問題を解消したスイッチング電源装置を構成する。

【解決手段】ローサイドスイッチング制御部81は、ローサイドスイッチング素子(Q1)へ駆動電圧信号を出力している期間にトランスの巻線電圧の極性反転を検出したときに、遅延時間(td1)の後にローサイドスイッチング素子(Q1)をターンオフさせるローサイドターンオフ回路を備え、ハイサイドスイッチング制御部61は、トランスの巻線電圧の極性が反転してからハイサイドスイッチング素子(Q2)をターンオンさせるまでの時間(td2)を遅延させる。そして、ローサイドターンオフ遅延回路の遅延時間(td1)はハイサイドターンオン遅延回路の遅延時間(td2)よりも短く設定されている。

(もっと読む)

ゲート駆動回路

【課題】逆導通IGBTに内蔵されたダイオードで発生するリカバリ電流を低減させる。

【解決手段】逆導通IGBTに内蔵されているダイオードに順方向電流が流れている間に、逆導通IGBTのゲート−エミッタ間にゲート閾値電圧よりも低い電圧を印加することで、逆導通IGBTのドリフト領域への正孔の注入を抑制し、リカバリ電流を低減させる。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

過電圧保護回路

【課題】過電圧保護回路を提供することを課題とする。

【解決手段】過電圧保護回路であって、電圧源とポータブル電子デバイスの間に提供された入力電圧が該ポータブル電子デバイスの許容定格耐電圧を超えないように設計する過電圧保護(overvoltage protection)を提供する。該回路は入力ユニットを通じて該電圧源から発生した入力電圧を受け、該入力電圧が分圧モジュールを通じて分圧電圧を生成することで、電圧安定モジュールが第1のスイッチングユニットを短絡状態、或いは、開路状態に入ることができる第1の制御信号を生成させ、また間接的に第2のスイッチングユニットを該第1のスイッチングユニットと逆の短絡状態、或いは、開路状態に入るよう制御し、該入力電圧が該定格電圧を上回った時、該第2のスイッチングユニットを通じて該入力電圧を該ポータブル電子デバイスに供給停止することで、温度の影響を受けることなく過電圧保護を実現できる。

(もっと読む)

不揮発性プログラマブルロジックスイッチ

【課題】メモリの選択的な書き込みを行う際のパストランジスタのゲート絶縁膜の破壊を防ぐとともにパストランジスタのゲート絶縁膜を薄くすることを可能にし、かつメモリの微細化によって書き込み効率が損なわれない不揮発性プログラマブルロジックスイッチを提供する。

【解決手段】第1端子と、第2端子と、メモリ状態を制御する制御信号を受ける第3端子とを有する第1メモリと、ソース/ドレインの一方が第2端子に接続される第1トランジスタと、第1トランジスタのソース/ドレインの他方にゲートが接続される第2トランジスタとを備えた、第1セルおよび第2セルを有する。第1セルの第1メモリの第3端子と、第2セルの第1メモリの第3端子は共通に接続され、第1セルに書き込みを行う場合、第3端子が書き込み電源に接続され、第1セルの第1端子は接地電源に接続され、第2メモリの第1端子は書き込み防止電源に接続される。

(もっと読む)

過電流保護回路

【課題】過電流検出抵抗の温度特性の影響をキャンセルすることのできる過電流保護回路を提供する。

【解決手段】基準抵抗と第1定電流源との第1接続点には、該第1接続点の電位の温度特性が、過電流検出抵抗の電圧検出端子の電位の温度特性と等しくなるように、第1接続点に対して正の温度特性を有する第2定電流を供給する第2定電流源が接続されている。第2定電流源は、負の温度特性を有する第3定電流を供給する第3定電流源と、温度特性を有さない第4定電流を供給する第4定電流源と、第3定電流源に対して直列接続された第1トランジスタと、第4定電流源に対して直列接続された第2トランジスタと、により構成された第1カレントミラー回路と、第4定電流源と第2トランジスタとの接続点に接続され、第1接続点に第2定電流を供給するための電流経路と、を有する。第3定電流源は、過電流検出抵抗と同じ基板に形成されている。

(もっと読む)

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

液晶表示装置

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

正負電圧論理出力回路およびこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とし、回路動作の確実性、安定性の向上を図った正負電圧論理出力回路を提供する。

【解決手段】論理入力と負電圧との間に、ゲートに論理入力するエンハンスメント型P型電界効果トランジスタEPFET1とブレークダウン保護用素子13,14とが直列に接続され、ブレークダウン保護用素子14に並列に短絡する切替スイッチ8aが接続される。切替スイッチ8aをオン、オフ制御することで、VSSの変動に対して正常な回路動作を確保できる動作ウィンドウの拡張を可能とする。

(もっと読む)

半導体スイッチの制御装置

【課題】半導体スイッチ素子に並列に接続される保護回路の異常を検出できる半導体スイッチ素子の制御回路を得る。

【解決手段】半導体スイッチに印加される電圧を抑制するために半導体スイッチに並列に接続された保護回路と、駆動回路の出力ゲート電圧が予め設定された電圧以上あることを検出し、半導体スイッチのオン・オフ状態を判別するゲート電圧検出手段と、半導体スイッチの主端子電圧を検出する主電圧検出手段と、駆動回路に与えられた駆動信号により、駆動指令がオン指令の場合はゲート電圧状態を選択し、駆動指令がオフ指令の場合は主電圧状態を選択する選択手段と、選択手段の出力を絶縁して低圧回路に伝達する第一の信号絶縁手段と、選択手段が選択して出力したゲート電圧状態・主電圧状態と半導体スイッチの駆動指令とを比較し、半導体スイッチの正常又は異常を判別する判別手段とを備える。

(もっと読む)

半導体スイッチ回路

【課題】高いESD保護耐圧を確保しつつ、ESD保護素子の静電容量を極力小さくし、しかも、集積化の際における占有サイズを小さくする。

【解決手段】ESD保護回路103は、共通端子41とグランドとの間に設けられており、共通端子41側から順に、ESD保護スイッチ素子としての複数の直列接続された電界効果トランジスタ31−1〜31−4と、逆接続された一組のESD保護素子としてのダイオード32−1,32−2が直列接続されると共に、電界効果トランジスタ31−1〜31−4は、ゲートが相互に接続されてグランドに接続されており、ESD保護素子のダイオード32−1,32−2による静電容量を低減し、高いESD保護耐圧の確保が可能となっている。

(もっと読む)

アクティブクランプ回路

【課題】アクティブクランプ動作期間を短縮するとともにESD耐量を向上させたアクティブクランプ回路を提供する。

【解決手段】実施形態によれば、第1のスイッチ素子と、第1のダイオードと、第1の抵抗と、第1および第2の制御回路と、を備えたことを特徴とするアクティブクランプ回路が提供される。前記第1のダイオードは、前記第1のスイッチ素子の両端にかかる過電圧によりブレークダウンする。前記第1の抵抗は、前記第1のダイオードの電流を検出する。前記第1の制御回路は、前記第1の抵抗の両端の電圧を増幅して前記第1のスイッチ素子の電流を制御する。前記第2の制御回路は、前記第1の抵抗の両端の電圧に応じて前記第1のスイッチ素子の導通を制御する。

(もっと読む)

スイッチング素子の保護回路

【課題】窒化物FETを高速スイッチング動作させることができ、且つ、サージ電圧から窒化物FETを保護することができるスイッチング素子の保護回路。

【解決手段】直列に接続された高圧側素子M1及び低圧側素子M2と、高圧側素子をオンオフさせる信号を出力するハイサイドプリドライバ11と、高圧側素子と逆のオンオフ状態になるように低圧素子をオンオフさせる信号を出力するローサイドプリドライバ12と、高圧側素子と低圧側素子の接続点に制御端子が接続されたスイッチング素子Tr1と、スイッチング素子の一方の端子にカソードが接続されたダイオードD1と、ダイオードのアノードに入力端子が接続され、ダイオードのブレーク時にスイッチング素子の制御端子に電流を供給するとともに、低圧側素子のオフを指示する信号をローサイドプリドライバに供給する制御器21とを備える。

(もっと読む)

ゲート駆動回路

【課題】過電流や短絡発生時に絶縁ゲート型トランジスタへの遮断の遅延を抑制し、安全に絶縁ゲート型トランジスタを保護できるゲート駆動を提供する。

【解決手段】対を成すNPNトランジスタ15、PNPトランジスタ17によるトーテムポール回路9に駆動信号が入力され、回路9の出力が絶縁ゲート型トランジスタ3のゲート3Aに接続され、トランジスタ3のゲート3Aの電位を下げて保護動作をする保護回路11が備えられたゲート駆動回路1であって、トーテムポール回路9のトランジスタ15、17ごとに独立して設けられて駆動信号をベース15A、17Aに入力するベースライン29A、29Bと、保護回路11の保護動作の間、トーテムポール回路9の上アーム側のトランジスタ15のベース電位を下げる電位強制低下回路13と、を備える。

(もっと読む)

1 - 20 / 194

[ Back to top ]